Flipflop

Ein Flipflop (Abk. FF) ist ein Logikelement mit 2 stabilen Zuständen. Die gängigste Variante ist das D-Flipflop mit

- mindestens zwei Eingängen

- D - Data, Dateneingang

- Clk - Clock, Takteingang

- taktunabhängigen Set/Reset-Eingängen (optional)

- einem oder zwei Ausgängen

- Q - Datenausgang

- /Q - komplementärem Datenausgang (optional)

Sobald der Takteingang von LOW nach HIGH wechselt (steigende Taktflanke) wird das Signal vom Dateneingang auf den Datenausgang übernommen (gespeichert) und bleibt so lange erhalten, bis die nächste steigende Flanke am Takteingang einrifft. Ein FlipFlop ist ein flankengesteuertes Speicherelement, im Gegensatz zum Latch.

Das IC 74xx273 enthält 8 Flipflops mit einm gemeinsamen Takt und Reset-Eingang. Mit diesen ICs kann man eine Porterweiterung vornehmen, beispielsweise um einen gemultiplexten Adress-/Datenbus anzusteuern.

In Digitalschaltungen in FPGAs oder CPLDs sollten möglichst nur Flipflops verwendet werden, da sie günstigere Eigenschaften bezüglich des Zeitverhaltens aufweisen als Latches.

Zeitverhalten von FlipFlops in synchronen Logikschaltungen

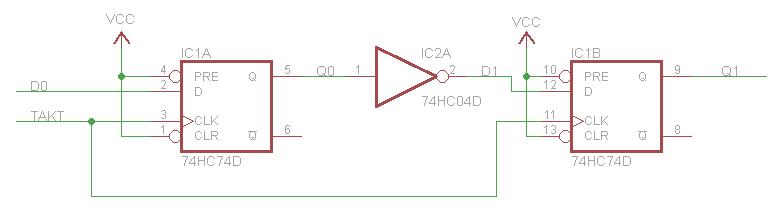

Hier soll das grundlegende Prinzip aller synchronen Logikschaltungen dargestellt werden. Es wird eine sehr einfache Schaltung verwendet, welche nur aus 2 FlipFlops und einem Inverter besteht.

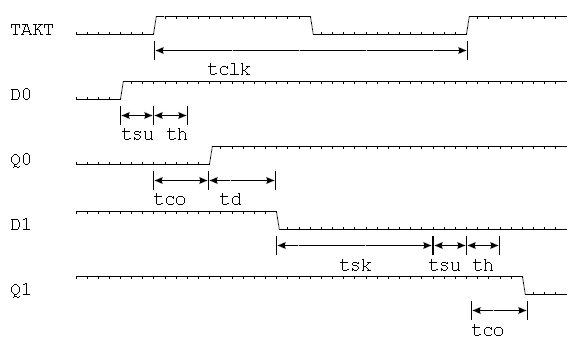

Zeitablauf

Kurz vor der aktiven (steigenden) Flanke werden die Daten an D0 von außen angelegt. Mit der ersten Taktflanke an FlipFlop IC1A werden diese gespeichert und erscheinen kurz darauf an dessen Ausgang. Die neuen Daten durchlaufen den Inverter. Ganz allgemein durchlaufen Daten aus FlipFlops eine kombinatorische Logik, die meistens deutlich komplexer ist als es hier dargestellt ist. D.h. es werden die Signale von vielen FlipFlops verarbeitet und es sind mehrere Logikfunktionen hintereinander geschaltet. Dabei treten nicht nur Verzögerungen in den Gattern auf, sondern auch auf den Leitungen, was vor allem bei schnellen FPGAs einen relativ großen Anteil an der Gesamtverzögerung ausmachen kann. Nachdem die Daten durch die Logik gelaufen sind, liegen sie am Eingang des nächsten FlipFlops IC1B an. Auch hier müssen diese wieder mindestens eine gewisse Zeit vor der nächsten Taktflanke anliegen, um sicher gespeichert zu werden. Die elementare Formel für das Zeitverhalten synchroner Logik ist.

[math]\displaystyle{ tclk \ge tco+td+tsk+tsu }[/math]

tsk darf 0ns betragen, aber nur dann, wenn alle anderen Parameter unter Berücksichtigung der Toleranzen der ICs sowie der Versorgungsspannung und Chiptemperatur auf ihren Maximalwert geprüft und in die Rechnung einbezogen wurden (worst case scenario). Diese Prüfung wird von Entwurfssoftware für FPGAs und ASICs automatisch für tausende von Logikpfaden durchgeführt.

| Symbol | Name | Erklärung |

|---|---|---|

| tsu | setup time | Daten müssen mindestens so lange vor der aktiven Taktflanke anliegen, um sicher gespeichert zu werden |

| th | hold time | Daten müssen mindestens so lange nach der aktiven Taktflanke anliegen, um sicher gespeichert zu werden. Bei vielen Logik-ICs ist diese Zeit 0ns, in wenigen Fällen sogar negativ. |

| tco | clock to output time | Verzögerung der Datenübernahme vom Takt zum Ausgang |

| tsk | slack time | Reserve für Datendurchlauf |

| tclk | clock period time | Periodendauer des Taktsignals |

| td | delay time | Verzögerungszeit der kombinatorischen Logik incl. Laufzeit auf Leitungen (FPGAs) |