## The Flyback Converter Lecture notes ECEN4517

- Derivation of the flyback converter: a transformer-isolated version of the buck-boost converter

- Typical waveforms, and derivation of  $M(D) = V/V_{o}$

- Flyback transformer design considerations

- Voltage clamp snubber

## Derivation of the flyback converter

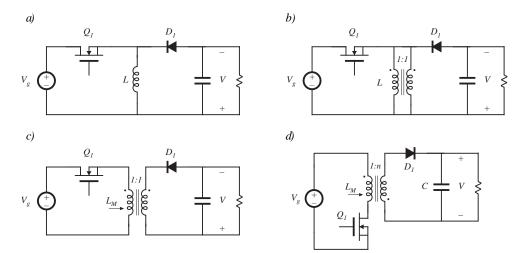

The flyback converter is based on the buck-boost converter. Its derivation is illustrated in Fig. 1. Figure 1(a) depicts the basic buck-boost converter, with the switch realized using a MOSFET and diode. In Fig. 1(b), the inductor winding is constructed using two wires, with a 1:1 turns ratio. The basic function of the inductor is unchanged, and the parallel windings are equivalent to a single winding constructed of larger wire. In Fig. 1(c), the connections between the two windings are broken. One winding is used while the transistor  $Q_1$  conducts, while the other winding is used when diode  $D_1$  conducts. The total current in the two windings is unchanged from the circuit of Fig. 1(b); however, the

Fig. 1. Derivation of the flyback converter: (a) buck-boost converter, (b) inductor L is wound with two parallel wires, (c) inductor windings are isolated, leading to the flyback converter, (d) with a 1:n turns ratio and positive output.

current is now distributed between the windings differently. The magnetic fields inside the inductor in both cases are identical. Although the two-winding magnetic device is represented using the same symbol as the transformer, a more descriptive name is "two-winding inductor". This device is sometimes also called a "flyback transformer". Unlike the ideal transformer, current does not flow simultaneously in both windings of the flyback transformer. Figure 1(d) illustrates the usual configuration of the flyback converter. The MOSFET source is connected to the primary-side ground, simplifying the gate drive circuit. The transformer polarity marks are reversed, to obtain a positive output voltage. A 1:n turns ratio is introduced; this allows better converter optimization.

## Analysis of the flyback converter

The behavior of most transformer-isolated converters can be adequately understood by modeling the physical transformer with a simple equivalent circuit consisting of an ideal

transformer in parallel with the magnetizing inductance. The magnetizing inductance must then follow all of the usual rules for inductors; in particular, volt-second balance must hold when the circuit operates in steady-state. This implies that the average voltage applied across every winding of the transformer must be zero.

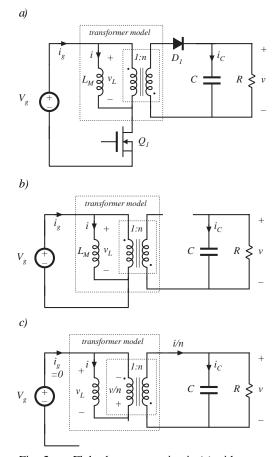

Let us replace the transformer of Fig. 1(d) with the equivalent circuit described above. The circuit of Fig. 2(a) is then obtained. The magnetizing inductance  $L_M$  functions in the same manner as inductor L of the original buck-boost converter of Fig. 1(a). When transistor  $Q_1$  conducts, energy from the dc source  $V_g$  is stored in  $L_M$ . When diode  $D_1$  conducts, this stored energy is transferred to the load, with the inductor voltage and current scaled according to the 1:*n* turns ratio.

Fig. 2. Flyback converter circuit, (a) with transformer equivalent circuit model, (b) during subinterval *1*, (c) during subinterval *2*.

During subinterval I, while transistor  $Q_I$  conducts, the converter circuit model reduces to Fig. 2(b). The inductor voltage  $v_L$ , capacitor current  $i_C$ , and dc source current  $i_g$ , are given by

$$v_L = V_g$$

$$i_C = -\frac{v}{R}$$

$$i_g = i$$

(1)

With the assumption that the converter operates with small inductor current ripple and small capacitor voltage ripple, the magnetizing current i and output capacitor voltage v can be approximated by their dc components, I and V, respectively. Equation (1) then becomes

$$v_L = V_g$$

$$i_C = -\frac{V}{R}$$

$$i_g = I$$

(2)

During the second subinterval, the transistor is in the off-state, and the diode conducts. The equivalent circuit of Fig. 2(c) is obtained. The primary-side magnetizing inductance voltage  $v_L$ , the capacitor current  $i_c$ , and the dc source current  $i_g$ , for this subinterval are:

$$v_L = -\frac{v}{n}$$

$$i_C = \frac{i}{n} - \frac{v}{R}$$

$$i_g = 0$$

(3)

It is important to consistently define  $v_L(t)$  on the same side of the transformer for all subintervals. Upon making the small-ripple approximation, one obtains

$$v_L = -\frac{V}{n}$$

$$i_C = \frac{I}{n} - \frac{V}{R}$$

$$i_g = 0$$

(4)

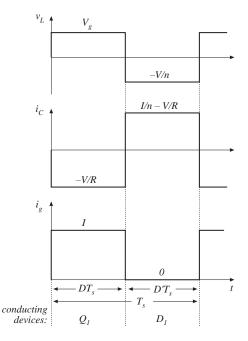

The  $v_L(t)$ ,  $i_C(t)$ , and  $i_g(t)$  waveforms are sketched in Fig. 3.

Application of the principle of voltsecond balance to the primary-side magnetizing inductance yields

$$\left\langle v_{L}\right\rangle = D\left(V_{g}\right) + D'\left(-\frac{V}{n}\right) = 0$$

(5)

Fig. 3. Flyback converter waveforms, continuous conduction mode.

Solution for the conversion ratio then leads to

$$M(D) = \frac{V}{V_g} = n \frac{D}{D'}$$

(6)

So the conversion ratio of the flyback converter is similar to that of the buck-boost converter, but contains an added factor of n.

Application of the principle of charge balance to the output capacitor C leads to

$$\left\langle i_{c}\right\rangle = D\left(-\frac{V}{R}\right) + D'\left(\frac{I}{n} - \frac{V}{R}\right) = 0 \tag{7}$$

Solution for *I* yields

$$I = \frac{nV}{D'R} \tag{8}$$

This is the dc component of the magnetizing current, referred to the primary. The dc component of the source current  $i_e$  is

$$I_g = \left\langle i_g \right\rangle = D\left(I\right) + D'\left(0\right) \tag{9}$$

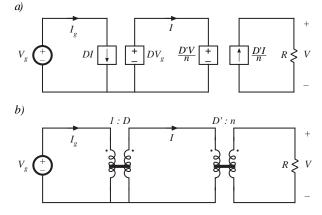

An equivalent circuit which models the dc components of the flyback converter waveforms can be constructed. The resulting dc equivalent circuit of the flyback converter is given in Fig. 4. It contains a 1:D

buck-type conversion ratio, followed by a (1 - D):1 boost-type conversion ratio, and an added factor of 1:*n*, arising from the flyback transformer turns ratio.

The flyback converter is commonly used at the 50-100W power range, as well as in highvoltage power supplies for televisions and computer monitors. It has the advantage of very low parts count. Multiple outputs can be obtained using a minimum

It has the advantage of very low Fig. 4. Flyback converter equivalent circuit model: (a) circuits corresponding to Eqs. (5), (7), and (9); (b) equivalent circuit containing ideal dc transformers.

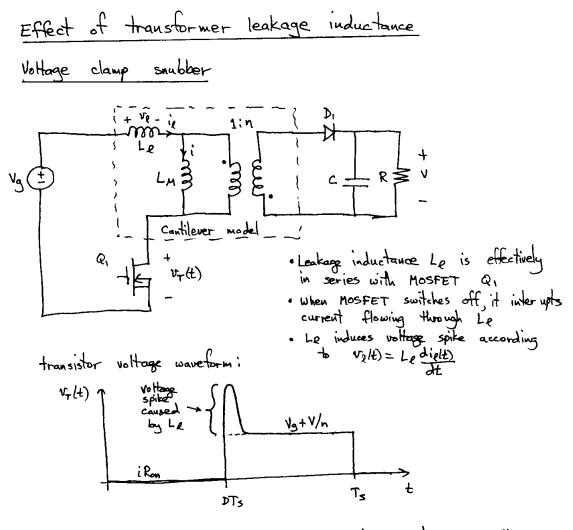

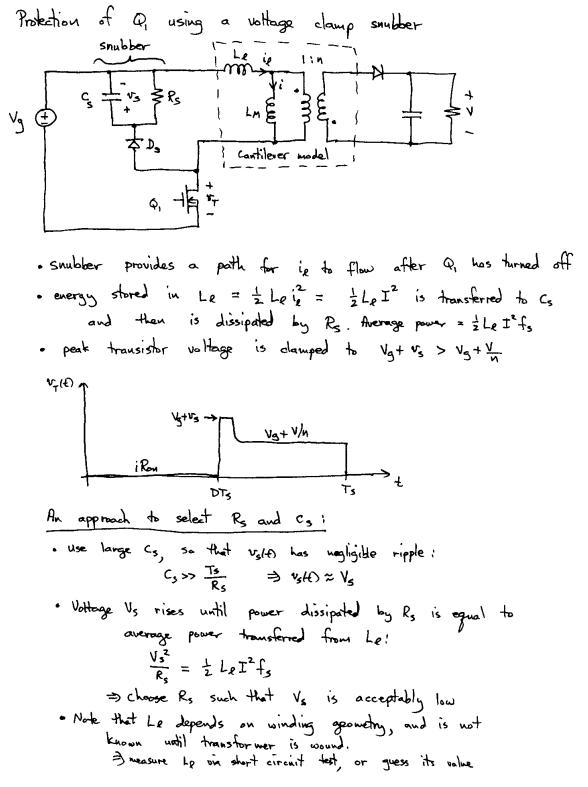

number of parts: each additional output requires only an additional winding, diode, and capacitor. The peak transistor voltage is equal to the dc input voltage  $V_g$  plus the reflected load voltage V/n; in practice, additional voltage is observed due to ringing associated with the transformer leakage inductance. A *snubber circuit* may be required to clamp the magnitude of this ringing voltage to a safe level that is within the peak voltage rating of the transistor.

Flyback transformer design

For this lab, you are given the following flyback transformer

design tosks:

• select L<sub>M</sub> such that

$$\Delta i = 502$$

of I

• use turns rotio  $n = \frac{n_2}{n_1} = 1.5$

• use a PQ 32/20 core  $\Rightarrow A_c, \omega_A, nhT, E_A$  are given

• select turns  $n_1$  such that total loss is minimized:

minimize  $P_{401} = P_{10} + P_{cu}$

core loss in residences

• f. primary and secondary

• determine air gap length  $l_g$

• determine primary and secondary wire gauges

• use fill factor  $K_u = 0.4$

• check to make sure that the peak B does not cause

the core to sofurate.

Choosing  $n_1$  to minimize  $P_{101}$

$$A_{ac} = n_1 A_a B_{ac} = L_m \Delta i$$

so  $B_{ac} = \frac{L_m \Delta i}{n_1 A_c}$

Once we have solved the converter circuit to find the desired values of Lm and Si, then Lm, Si, and Ac are known. Hence this equation relates Bac to n. Increasing n. decreases Bac, which decreases the core loss Pfe. Computing cone loss

Core loss Pie depends on the peak value of the ac component

of flux density Re. Manufacturers published data shots contain

plats of Pie , that follow functions of the form

$$P_{fe} = K_{fe} B_{hc}^{e} A_{c} ln$$

See TDK H7C3 ferrite data - course website links to data sheets

$K_{fe}$  is a constant of proportionality that depends

on switching frequency and one material

$\beta$  is an exponent that depends on core material

$A_{c} lm$  is the volume of the core

For H7C3 material :

$\beta = 2.6$

$K_{fe} = \begin{cases} 16 & \text{at SO kH2} & \text{at Go*C} \\ 40 & \text{at 100 kH2} & \text{at Go*C} \end{cases}$

with  $A_{c} lm$  expressed in Cm<sup>3</sup>

$B_{hc}$  expressed in Task

$R_{e}$  expressed in Task

$R_{e}$  expressed in Watts

$B = \frac{1}{2} \frac{1}{2}$

priver privery unding resistance

$$R_{2} = \rho \frac{n_{1}(\mu_{1T})}{R_{02}}$$

So use lots of turns to decrease core loss.

to decrease core loss.

The d

$$\frac{Copper \log vs. n_1!}{P_{cu} = P_{cus} + P_{cu_2} = I_{s,ms}^2 R_1 + I_{a,ms}^2 R_2}$$

$$= I_{s,ms}^2 P \frac{n_1^2 (MLT)}{\alpha_1 K_u W_A} + I_{a,ms}^2 P \frac{(n n_1)^2 (MLT)}{\alpha_2 K_u W_A}$$

$$= P \frac{n_1^2 (MLT)}{K_u W_A} \left( \frac{I_{s,ms}}{\alpha_1} + \frac{n^2 I_{2,ms}^2}{\alpha_2} \right) \qquad \text{with} \quad \alpha_2 = 1 - \alpha_1$$

· increasing no increases copper loss

· there is a value of ny that minimizes total loss

· Minimum copper loss occurs when window area is allocated as follows:

$$\alpha'_{1} = \frac{I_{1,ms}}{I_{1,ms} + n I_{2,ms}}, \quad \alpha'_{2} = \frac{n I_{2,ms}}{I_{1,ms} + n I_{2,ms}}$$

copper loss

$$\frac{P_{cur}}{P_{cur}}$$

A spread sheet design approach

- Try different values of us until Ptot is minimized

Then compute wire sizes, gap length, etc.

If the peak magnitude of the voltage spike exceeds the voltage rating of the MOSFET, then Q, will fail.

Example - a first-pass selection of Rs and Cs

Given

$$Vg = 150V$$

,  $V = 15V$ ,  $n = 0.2$

$f_s = 100 \text{ kHz}$ ,  $Lm = 1 \text{ mH}$   $I = 1.5A$

MOSFET peak voltage rating = 400V

$I + is$  desired to limit peak  $v_T$  to 325V

Estimate  $Lg$ : in a good, corefully could transformer, it may

be possible to achieve  $L_p = 32$  of  $L_M = 30\mu\text{H}$

Energy stored in  $Lg$  during  $0.440 \text{ DTs}$ :

$W_g = \frac{1}{2}Lg I^2 = (\frac{1}{2})(30\mu\text{H})(1.5A)^2 = 33.75\mu\text{J}$

Average power transferred from  $L_p$  to subber:

$P_g = W_p f_s = (33.75\mu\text{J})(100\text{ kHz}) = 3.375\text{ W}$

To limit peak  $V_T$  to  $325V$ , we need

$V_s = (\text{peak } V_T) - V_g = 32S - 150 = 175V$

So choose

$R_s = \frac{V_s^2}{R_s} = \frac{(175)^2}{(3.375\text{W})} = 9074 \text{ SL}$

we might use a  $10k.D_T, 500$  resistor. Then

$C_s \gg \frac{T_s}{R_s} = \frac{(10\mu s)}{(10k.52)} = 1 \text{ nF}$

A good choice might be  $C_s = 47 \text{ nF}, 250V$ .

The above calculations are based on the estimate  $L_p = 32 \text{ of } Lm$ ,

and should be considered first-pass estimates.