## 8.7 AC CHARACTERISTICS

## 8.7.1 Parallel Interface Characteristics (8080-series MPU)

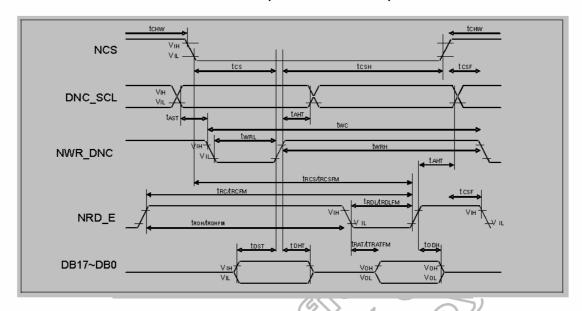

Figure 8. 1 Parallel Interface Characteristics (8080-series MPU)

(VSSA=0V, VCC=1.65V to 2.50V, VCI=2.3V to 2.9V, Ta = -30 to  $70^{\circ}$  C)

| Signal     | Symbol                                        | Parameter                                                                                                                                                                             | Min.                             | Max.                      | Unit | Description                               |

|------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------|------|-------------------------------------------|

| DNC_SCL    | tast<br>taht                                  | Address setup time Address hold time (Write/Read)                                                                                                                                     | 10<br>10                         |                           | ns   | -                                         |

| NCS        | tchw<br>tcs<br>trcs<br>trcsfm<br>tcsf<br>tcsh | Chip select "H" pulse width Chip select setup time (Write) Chip select setup time (Read ID) Chip select setup time (Read FM) Chip select wait time (Write/Read) Chip select hold time | 0<br>35<br>45<br>355<br>10<br>10 | -                         | ns   | -                                         |

| NWR_RNW    | twc<br>twrh<br>twrL                           | Write cycle Control pulse "H" duration Control pulse "L" duration                                                                                                                     | 10<br>35<br>35                   | -<br>-<br>-               | ns   | -                                         |

| NRD_E (ID) | trc<br>trdh<br>trdl                           | Read cycle (ID) Control pulse "H" duration (ID) Control pulse "L" duration (ID)                                                                                                       | 160<br>90<br>45                  | -<br>-<br>-               | ns   | When read ID data                         |

| NRD_E (FM) | trcfm<br>trdhfm<br>trdlfm                     | Read cycle (FM) Control pulse "H" duration (FM) Control pulse "L" duration (FM)                                                                                                       | 450<br>90<br>355                 | -<br>-<br>-               | ns   | When read from frame memory               |

| D15 to D0  | tdst<br>tdht<br>trat<br>tratem<br>todh        | Data setup time Data hold time Read access time (ID) Read access time (FM) Output disable time                                                                                        | 15<br>10<br>-<br>-<br>20         | -<br>-<br>40<br>340<br>80 | ns   | For maximum C∟=30pF<br>For minimum C∟=8pF |

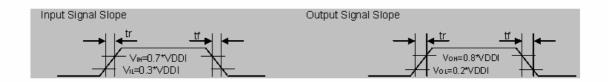

Note: The input signal rise time and fall time (tr, tf) is specified at 15 ns or less.

Logic high and low levels are specified as 30% and 70% of VDD1 for Input signals. For output, see Section 7.7.6.1

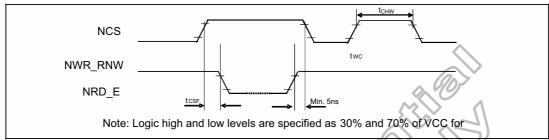

Figure 8. 2 Chip Select Timing

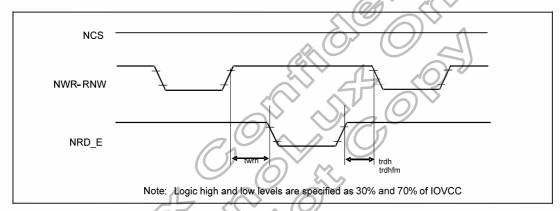

Figure 8. 3 Write to Read and Read to Write Timing