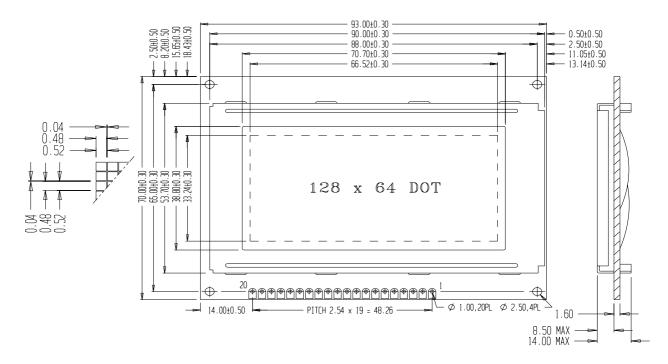

### **■ PHYSICAL DATA**

| Item                | Contents                                                                | Unit    |

|---------------------|-------------------------------------------------------------------------|---------|

| LCD type            | STN                                                                     |         |

| LCD duty            | 1/64                                                                    |         |

| LCD bias            | 1/9                                                                     |         |

| Viewing direction   | 6                                                                       | o'clock |

| Module size (W×H×T) | $93 \times 70 \times 14$ MAX $(3.66'' \times 2.76'' \times 0.55''$ MAX) | mm      |

| Viewing area (W×H)  | 70.7× 38.8 (2.78" × 1.53")                                              | mm      |

| Number of dots      | 128 × 64                                                                | dots    |

| Dot size (W×H)      | $0.48 \times 0.48 \ (0.019'' \times 0.019'')$                           | mm      |

| Dot pitch (W×H)     | $0.52 \times 0.52 \ (0.020'' \times 0.020'')$                           | mm      |

### **■ EXTERNAL DIMENSIONS**

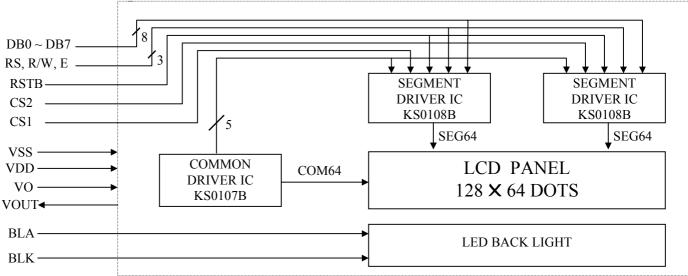

## ■ BLOCK DIAGRAM

| 20  | 19  | 18   | 17   | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6 | 5   | 4  | 3  | 2   | 1   |

|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|-----|----|----|-----|-----|

| BLK | BLA | VOUT | RSTB | CS2 | CS1 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Е | R/W | RS | VO | VDD | VSS |

|     |     |      |      |     |     |     |     |     |     |     |     |     |     |   |     |    |    |     |     |

## ■ **ABSOLUTE MAXIMUM RATINGS** ( Ta = 25°C)

| Parameter                | Symbol   | Min  | Max     | Unit |

|--------------------------|----------|------|---------|------|

| Supply voltage for logic | VDD      | -0.3 | 7.0     | V    |

| Supply voltage for LCD   | VDD - VO | -0.3 | VDD+0.3 | V    |

| Input voltage            | VI       | -0.3 | VDD+0.3 | V    |

| Operating temperature    | TOP      | 0    | 50      | °C   |

| Storage temperature      | TST      | -10  | 60      | °C   |

## ■ ELECTRICAL CHARACTERISTICS ( $VDD = +5V\pm5\%$ , VSS = 0V, Ta = 25°C )

### **♦ DC Characteristics**

| Parameter                     | Symbol   | Condition | Min    | Тур  | Max    | Unit |

|-------------------------------|----------|-----------|--------|------|--------|------|

| Supply voltage for logic      | VDD      |           | 4.5    | 5.0  | 5.5    | V    |

| Supply current for logic      | IDD      |           |        | 2.02 | 4      | mA   |

|                               |          | 0°C       | 8.4    | 8.8  | 9.2    | V    |

| Operating voltage for LCD     | VDD - VO | 25°C      | 8.1    | 8.5  | 8.9    | V    |

|                               |          | 50°C      | 7.4    | 7.8  | 8.2    | V    |

| Supply voltage for back light | VF       |           |        | 4.2  | 4.6    | V    |

| Supply current for back light | IF       | VF=4.2V   |        | 500  | 840    | mA   |

| Input voltage 'H'level        | VIH      |           | 0.7VDD |      | VDD    | V    |

| Input voltage ' L ' level     | VIL      |           | 0      |      | 0.3VDD | V    |

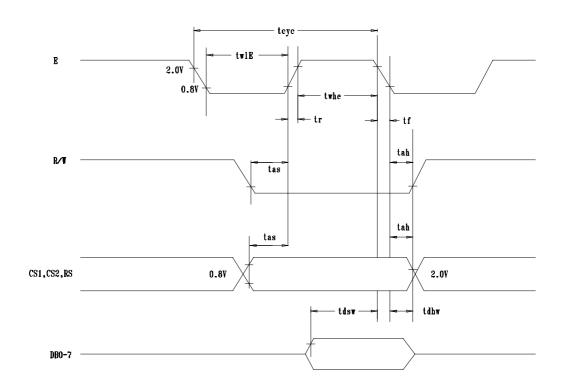

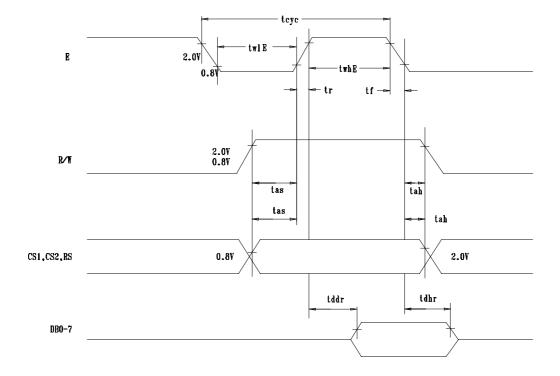

### **♦** AC Characteristics

#### • MPU Interface

| Characteristic        | Symbol  | Min  | Тур | Max | Unit |

|-----------------------|---------|------|-----|-----|------|

| E cycle               | teye    | 1000 |     |     | ns   |

| E high level width    | twhE    | 450  |     |     | ns   |

| E low level width     | twlE    | 450  |     |     | ns   |

| E rise time           | $t_{r}$ |      |     | 25  | ns   |

| E fall time           | tf      |      |     | 25  | ns   |

| Address set-up time   | tas     | 140  |     |     | ns   |

| Address hold time     | tah     | 10   |     |     | ns   |

| Data set-up time      | tdsw    | 200  |     |     | ns   |

| Data delay time       | tddr    |      |     | 320 | ns   |

| Data hold time(write) | tdhw    | 10   |     |     | ns   |

| Data hold time(read)  | tdhr    | 20   |     |     | ns   |

LCD MODULE

MPU Write Timing

MPU Read Timing

#### ■ OPERATING PRINCIPLES & METHODS

#### **♦ I/O Buffer**

Input buffer controls the status between the enable and disable of chip. Unless the CS1 or CS2 is in active mode, input or output of data and instruction do not execute. Therefore internal state is not changed. But RSTB can operate regardless of CS1 and CS2.

LCD MODULE

### **♦** Input Register

Input register is provided to interface with MPU which is different operating frequency. Input register stores the data temporarily before writing it into display data RAM.

When CS1 or CS2 is in the active mode, R/W and RS select the input register. The data from MPU is written into input register and then write it into display data RAM. Data is latched when falling of the E signal and written automatically into the display data RAM by internal operation.

#### **♦** Output Register

Output register stores the data temporarily from display data RAM when CS1 or CS2 is in active mode and R/W and RS=H. Stored data in display data RAM is latched in output register. When CS1 or CS2 is in active mode and R/W=H, RS=L, status data (busy check)can be read out.

To read the contents of display data RAM, twice access of read instruction is needed. In first access, data in display data RAM is latched into output register. In second access, MPU can read data which is latched. That is, to read the data in display data RAM, it needs dummy read. But status read does not need dummy read.

| RS | R/W | Function                                            |

|----|-----|-----------------------------------------------------|

| 0  | 0   | Instruction                                         |

|    | 1   | Status read(busy cheek)                             |

| 1  | 0   | Data write(from input register to display data RAM  |

|    | 1   | Data read(from display data RAM to output register) |

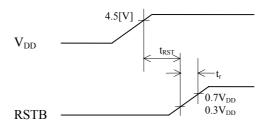

#### ◆ Reset

System reset can be initialized by setting RSTB terminal at low level when turning power on, receiving instruction from MPU. When RSTB becomes low, following procedure is occurred.

- Display off

- Display start line register becone set by 0.(Z-address 0)

While RSTB is low level, no instruction except status read can be accepted. Reset status appears at DB4. After DB4 is low, any instruction can be accepted.

The Conditions of power supply at initial power up are shown in table 1.

Table 1. Power Supply Initial Conditions

| Item       | Symbol       | Min | Тур | Max | Unit |

|------------|--------------|-----|-----|-----|------|

| Reset time | <b>t</b> rst | 1.0 |     |     | us   |

| Rise time  | tr           |     |     | 200 | ns   |

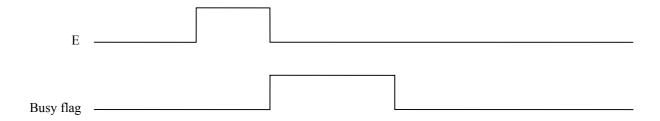

### **♦** Busy Flag

Busy flag indicates that KS0108B is operating or not operating. When busy flag is high, KS0108B is in internal operating. When busy flag is low, KS0108B can accept the data or instruction.

DB7 indicates busy flag of the KS0108B.

#### **◆** Display ON/OFF Flip-Flop

The display on/off flip-flop makes on/off of the liquid crystal display. When flip-flop is reset (logical low). selective voltage or non selective voltage appears on segment output terminals. When flip-flop is set (logical high).non selective voltage appears on segment output terminals regardless of display RAM data.

The display on/off flip-flop can change status by instruction. The display data at all segment disappear while RSTB is low. The status of the flip-flop is output to DB5 by read instruction.

#### **♦** X page Register

X page register designates page of the internal display data RAM. It has not count function. An address is set by instruction.

#### **♦** Y Address Counter

Y address counter designates address of the internal display data RAM. An address is set by instruction and is increased by 1 automatically by read or write operations of display data.

### **♦** Display Data RAM

Display data RAM stores a display data for liquid crystal display. To express on state of dot matrix of liquid crystal display. write data 1. The other way. off state writes 0.

### **♦** Display Start Line Register

The display start line register indicates address of display data RAM to display top line of liquid crystal display. Bit data (DB<0:5>) of the display start line set instruction is latched in display start line register. It is used for scrolling of the liquid crystal display screen.

## **♦** Display Control Instruction

The display control instructions control the internal state of the KS0108B. Instruction is received from MPU to KS0108B for the display control. The following table shows various instructions.

| Instruction        | RS | R/W | DB7 | DB6 | DB5               | DB4   | DB3     | DB2       | DB1          | DB0                                 | Function                            |

|--------------------|----|-----|-----|-----|-------------------|-------|---------|-----------|--------------|-------------------------------------|-------------------------------------|

| Display ON/OFF     | 0  | 0   | 0   | 0   | 1                 | 1     | 1       | 1         | 1            | 0/1                                 | Controls the display on or off.     |

|                    |    |     |     |     |                   |       |         |           |              |                                     | Internal status and display RAM     |

|                    |    |     |     |     |                   |       |         |           |              |                                     | data are not affected.              |

|                    |    |     |     |     |                   |       |         |           |              |                                     | 0:OFF, 1:ON                         |

| Set Address        | 0  | 0   | 0   | 1   |                   | Y     | addres  | ss (0~6   | 3)           |                                     | Sets the Y address in the Y         |

|                    |    |     |     |     |                   |       |         |           |              |                                     | address counter.                    |

| Set Page           | 0  | 0   | 1   | 0   | 1                 | 1     | 1       |           | Page         |                                     | Sets the X address at the X         |

| (X address)        |    |     |     |     |                   |       |         |           | $(0 \sim 7)$ |                                     | address register.                   |

| Display Start Line | 0  | 0   | 1   | 1   |                   | Γ     | Display | start lir | ne           |                                     | Indicates the display data RAM      |

|                    |    |     |     |     | (0~63)            |       |         |           |              | displayed at the top of the screen. |                                     |

| Status Read        | 0  | 1   | В   | 0   | О                 | R     | 0       | 0         | 0            | 0                                   | Read status.                        |

|                    |    |     | U   |     | N                 | E     |         |           |              |                                     | BUSY 0 : Ready                      |

|                    |    |     | S   |     | /                 | S     |         |           |              |                                     | 1 : In operation                    |

|                    |    |     | Y   |     | О                 | E     |         |           |              |                                     | ON/OFF 0 : Display ON               |

|                    |    |     |     |     | F                 | T     |         |           |              |                                     | 1 : Display OFF                     |

|                    |    |     |     |     | F                 |       |         |           |              |                                     | RESET 0 : Normal                    |

|                    |    |     |     |     |                   |       |         |           |              |                                     | 1 : Reset                           |

| Write Display Data | 1  | 0   |     |     |                   | Write | e Data  |           |              |                                     | Writes data (DB0:7) into display    |

|                    |    |     |     |     |                   |       |         |           |              |                                     | data RAM. After writing             |

|                    |    |     |     |     |                   |       |         |           |              |                                     | instruction, Y address is increased |

|                    |    |     |     |     |                   |       |         |           |              |                                     | by 1 automatically.                 |

| Read Display Data  | 1  | 1   |     |     | Read Data Reads d |       |         |           |              | Reads data (DB0:7) from display     |                                     |

|                    |    |     |     |     |                   |       |         |           |              |                                     | data RAM to the data bus.           |

## ■ DISPLAY DATA RAM ADDRESS MAP

| GE ADDRESS | DISPLAY<br>Data | 1ST KS010                                | 8B           | 2ND KS0108B | LINE<br>ADDRESS | COMMON           |

|------------|-----------------|------------------------------------------|--------------|-------------|-----------------|------------------|

|            | D 0             |                                          | +            |             | C 0             | CON 0            |

| -          | D 1             |                                          | +            |             | C 1             | CON 1            |

| DO -       | D 2<br>D 3      | <u> </u>                                 | +            |             | C 2             | CON 2<br>CON 3   |

| B8         | D 4             |                                          | +            |             | C 4             | CON 4            |

|            | D 5             | +                                        | - $ +$       |             | C 5             | CON 5            |

|            | D 6             |                                          |              |             | C 6             | CON 6            |

|            | D 7             |                                          |              |             | C 7             | CON 7            |

|            | D 0             |                                          |              |             | C 8             | CON 8            |

| -          | D 1             |                                          |              |             | C 9             | CON 9            |

|            | D 2             |                                          |              |             | C A<br>C B      | CON 10<br>CON 11 |

| B9         | D 4             |                                          |              |             | СС              | CON 12           |

| -          | D 5             |                                          |              |             | C D             | CON 13           |

|            | D 6             |                                          |              |             | C B             | CON 14           |

|            | D 7             |                                          |              |             | C P             | CON 15           |

|            | D 0             |                                          |              |             | D 0             | CON 16           |

|            | D 1             |                                          |              |             | D 1             | CON 17           |

|            | D 2             |                                          |              |             | D 2             | CON 18           |

| BA         | D 3             |                                          |              |             | D 3             | CON 19           |

| -          | D 4             |                                          |              |             | D 4             | CON 20           |

|            | D 5             |                                          |              |             | D 5<br>D 6      | CON 21           |

| -          | D 7             |                                          |              |             | D 7             | CON 22<br>CON 23 |

|            | D 0             |                                          |              |             | D 8             | CON 24           |

|            | D 1             |                                          |              |             | D 9             | CON 25           |

|            | D 2             |                                          |              |             | D A             | CON 26           |

| BB         | D 3             |                                          |              |             | D B             | CON 27           |

|            | D 4             |                                          |              |             | D C             | COM 28           |

| -          | D 5             |                                          |              |             | D D             | CON 29           |

|            | D 6             |                                          |              |             | D B             | CON 30           |

|            | D 7             |                                          |              |             | D F             | CON 31           |

| -          | D 0             |                                          |              |             | E 0<br>E 1      | CON 32<br>CON 33 |

| -          | D 2             |                                          |              |             | E 2             | CON 34           |

| BC         | D 3             |                                          |              |             | E 3             | CON 35           |

| DC -       | D 4             |                                          |              |             | E 4             | CON 36           |

|            | D 5             |                                          |              |             | E 5             | COM 37           |

|            | D 6             |                                          |              |             | E 6             | CON 38           |

|            | D 7 ' '         |                                          |              |             | E 7             | CON 39           |

| -          | D 0             |                                          |              |             | E 8             | CON 40           |

| -          | D 1             |                                          |              |             | E 9<br>E A      | CON 41<br>CON 42 |

| nn -       | D 3             |                                          |              |             | E B             | COM 42           |

| BD -       | D 4             |                                          |              |             | E C             | CON 44           |

|            | D 5             |                                          |              |             | E D             | CON 45           |

|            | D 6             |                                          |              |             | E B             | COM 46           |

|            | D 7             |                                          |              |             | E F             | COM 47           |

|            | D 0             |                                          |              |             | F O             | CON 48           |

| -          | D 1             |                                          |              |             | F 1             | CON 49           |

| , P        | D 2             |                                          |              |             | F 2<br>F 3      | CON 50<br>CON 51 |

| BE -       | D 3             |                                          |              |             | F 4             | CON 51           |

| <br>       | D 5             |                                          |              |             | F 5             | COM 53           |

|            | D 6             |                                          |              |             | F 6             | CON 54           |

|            | D 7             | · · · · ·                                |              |             | F 7             | COM 55           |

|            | D 0             |                                          |              |             | F 8             | CON 56           |

|            | D 1             |                                          |              |             | F 9             | COM 57           |

| -          | D 2             |                                          |              |             | FA              | COM 58           |

| BF _       | D 3             |                                          |              |             | F B             | CON 59           |

| -          | D 4<br>D 5      |                                          |              |             | F C<br>F D      | CON 60<br>CON 61 |

| -          | D 6             |                                          |              |             | FE              | CON 62           |

| -          | D 7             |                                          |              |             | FF              | CON 63           |

|            | SS SS           |                                          |              |             |                 | COM OU           |

|            | 물쩍 [승]          | 12 4 4 — — — — — — — — — — — — — — — — — | <del> </del> | <u>-</u> L  | 1               |                  |

|            | # 14 B E E      | 444                                      | 12-1-        |             | 2-              |                  |

|            | S               |                                          |              |             |                 |                  |

|            | COLU            |                                          |              |             | SBC 127 7       |                  |

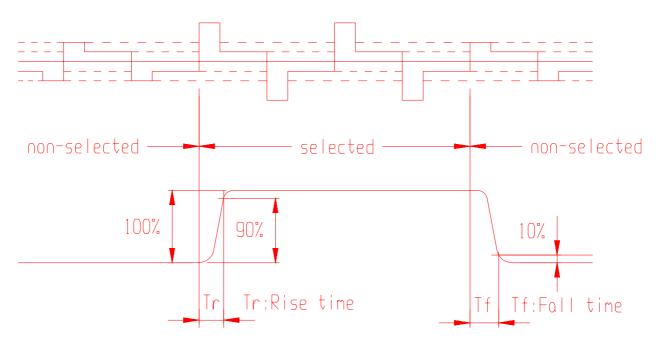

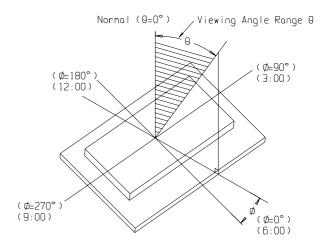

## ■ ELECTRO-OPTICAL CHARACTERISTICS ( $V_{OP} = 8.5V$ , $T_a = 25$ °C)

| Item                | Symbol | Condition  | Min | Тур  | Max | Unit | Remarks  | Note |

|---------------------|--------|------------|-----|------|-----|------|----------|------|

| Response time       | Tr     |            |     | 389  |     | ms   |          | 1    |

|                     | Tf     |            |     | 153  |     | ms   |          | 1    |

| Contrast ratio      | Cr     |            |     | 15.8 |     |      |          | 2    |

|                     |        |            | 30  |      |     | deg  | Ø = 90°  | 3    |

| Viewing angle range | θ      | $Cr \ge 2$ | 30  |      |     | deg  | Ø = 270° | 3    |

|                     |        |            | 26  |      |     | deg  | Ø = 0°   | 3    |

|                     |        |            | 50  |      |     | deg  | Ø = 180° | 3    |

Note1: Definition of response time.

Note2: Definition of contrast ratio 'Cr'

Brightness of selected segment(B1) Brightness curve for non-selected segment Brightness Brightness curve for selected segment В1 Driving Voltage ۷ор

Brightness of non-selected segment(B2)

Note3: Definition of viewing angle range ' $\theta$ '.

# ■ INTERFACE PIN CONNECTIONS

| Pin No. | Symbol | Level                | Description                  |

|---------|--------|----------------------|------------------------------|

| 1       | VSS    | 0V                   | Ground                       |

| 2       | VDD    | 5.0V                 | Supply voltage for logic     |

| 3       | VO     |                      | Input voltage for LCD        |

| 4       | RS     | H/L                  | H: Data, L: Instruction code |

| 5       | R/W    | H/L                  | H: Read mode, L: Write mode  |

| 6       | E      | $H, H \rightarrow L$ | Chip enable signal           |

| 7       | DB0    | H/L                  | Data bit 0                   |

| 8       | DB1    | H/L                  | Data bit 1                   |

| 9       | DB2    | H/L                  | Data bit 2                   |

| 10      | DB3    | H/L                  | Data bit 3                   |

| 11      | DB4    | H/L                  | Data bit 4                   |

| 12      | DB5    | H/L                  | Data bit 5                   |

| 13      | DB6    | H/L                  | Data bit 6                   |

| 14      | DB7    | H/L                  | Data bit 7                   |

| 15      | CS1    | Н                    | Chip select signal for IC1   |

| 16      | CS2    | Н                    | Chip select signal for IC2   |

| 17      | RSTB   | L                    | Reset signal                 |

| 18      | VOUT   | -5V                  | Output voltage for LCD       |

| 19      | BLA    | 4.2V                 | Back light anode             |

| 20      | BLK    | 0V                   | Back light cathode           |

## **■ PART LIST**

| Part Name          | Description       | Quantity |

|--------------------|-------------------|----------|

| IC                 | KS0107B.PCC       | 1        |

| IC                 | KS0108B.PCC       | 2        |

| IC                 | SCI7660MOA        | 1        |

| IC                 | NJM064M(OP-AMP)   | 1        |

| LCD                | 64128A            | 1        |

| PCB                | 64128A            | 1        |

| Frame              | MG12864-1B        | 1        |

| Rubber connector   | 83.7x6.9x2.9mm YS | 2        |

| Heatseal connector | 6405              | 1        |

| Resistor           | 3ΚΩ               | 4        |

| Resistor           | 15ΚΩ              | 1        |

| Resistor           | 1ΜΩ               | 1        |

| Resistor           | 47ΚΩ              | 1        |

| Capacitor          | 27pF ± 5%         | 1        |

| Capacitor          | 10uF              | 2        |

| Transistor         | M5                | 1        |

| LED box            | LB12864-1         | 1        |

| LED light          | LB12864A1-3       | 1        |

| LED light          | ED-011YGU         | 84       |