# 5 Aufgaben einer Schaltung

Man kann Teilschaltungen auch nach ihrer Funktion innerhalb der Gesamtschaltung untergliedern:

## 5.1 Eingangsschaltungen

Zwei spezielle Probleme bei Eingangsschaltungen sind einerseits zu kleine, zu hohe oder nicht definierte Spannungen, andererseits die Umsetzung mechanisch bewirkter Spannungsänderungen. Darauf wird im Folgenden kurz eingegangen.

## 5.1.1 Nicht definierte Eingangsspannung

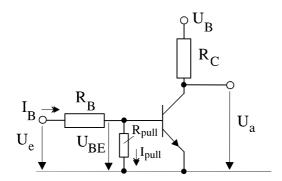

Bisher wurde angenommen, daß die Eingangsspannung U<sub>e</sub> stets definiert im Highoder im Low-Bereich liegt. Ist das nicht der Fall, weil auch ein hochohmiger Zustand möglich ist (falls z.B. der Eingang an den Open-Collector-Ausgang eines vorausgehenden Bausteins angeschlossen ist), so muß man selbst mit Pullup- oder Pulldown-Widerständen dafür sorgen, daß diese Voraussetzung nachträglich erfüllt wird. Bild 5-1 zeigt das Beispiel einer Eingangsschaltung mit Pulldown-Widerstand.

Bild 5-1: Eingangsschaltung mit Pulldown-Widerstand. Der Transistor wird so sicher gesperrt, falls nicht eine Spannung  $U_e$  im High-Bereich anliegt.

$I_{pull}$  in Bild 5-1 soll klein sein, um die Verlustleistung zu minimieren. Die Faustregel lautet:  $I_{pull} \le 0.1~I_B$ . Daraus folgt

$$R_{pull} \ge 10 U_{BE}/I_{B}$$

Im Beispiel von Abschnitt 4.2 erhält man daraus

$$R_{pull} \ge$$

Ge V 5 - 1 9/99

## 5.1.2 Verstärkung kleiner Eingangsspannungen

Schwankt eine Eingangsspannung um weniger als 0.7 V, wenn sie von high zu low wechselt, so läßt sich ein normaler Transistor damit nicht mehr sicher schalten. Die Eingangsspannung muß folglich verstärkt werden. Eine ausführliche Behandlung des Themas fällt in das Fach Elektronik, deshalb nachstehend nur zwei Rezepte:

## Verstärkung mit einem Transistor:

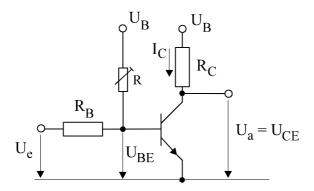

Das ist die billigste Lösung (Preis eines geeigneten Transistors um 10 Pfennige). Bild 5-2 zeigt ein Beispiel zur Verstärkung einer Eingangsspannung mit low entsprechend 0 V und high entsprechend 0.5 V.

Bild 5-2: Verstärkung einer zu kleinen Eingangsspannung mit einem Transistor

Es sei nun  $U_B=5$  V. Da die Eingangsschaltung in der Regel Logikbausteine zu versorgen hat, muß man darauf achten, daß  $I_C$  diese treiben kann. Ein typischer Wert für den Eingangsstrom eines Logikbausteins im High-Zustand ist 0.04 mA. Wählt man nun beispielsweise ein maximales  $I_C=0.50$  mA, so ist man auf der sicheren Seite. Man könnte damit sogar mehrere (bis zu 12) Logikbausteine parallel betreiben. Aus

$$I_C$$

= 0.5 mA und  $U_B$  = 5 V folgt  $R_C$  = 10 k $\Omega$ . Weitere Forderungen sind:

$$U_e = 0.00 \; V \quad \Rightarrow \quad U_a = 5.0 \; V \; \; (\text{da der Transistor invertient})$$

$$U_e = 0.50 \text{ V} \implies U_a = 0.0 \text{ V}$$

Da der Transistor als Analogverstärker arbeiten soll, läßt man ihn für die mittlere Eingangsspannung von 0.25 V in der "Mitte" des Ausgangskennlinienfeldes arbeiten. Daraus folgt

$$U_e = 0.25 \text{ V} \implies U_a = 2.5 \text{ V}$$

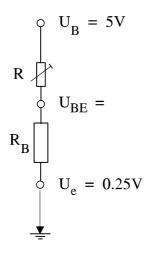

Nun bilden R<sub>B</sub> und R einen Spannungsteiler gemäß Bild 5-3.

Ge V 5 - 2 9/99

Bild 5-3: Spannungsteiler von R und  $R_B$  in Bild 5-2

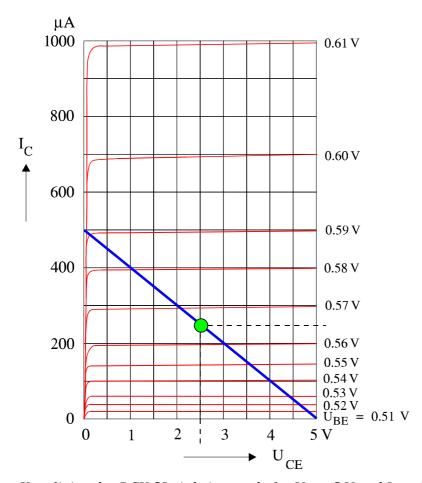

Man muß daher R und R\_B so wählen, daß sich für  $U_e=0.25~V$  im Kennlinienfeld  $U_{CE}=2.5~V$  einstellt. Bild 5-4 zeigt, daß dafür  $U_{BE}\approx 0.565~V$  nötig ist.

Bild 5-4: Kennlinien des BCY 58. Arbeitsgerade für  $U_B=5\ V$  und  $I_C=0.5\ mA$ . Arbeitspunkt bei  $U_{CE}=2.5\ V$ .

Ge V 5 - 3 9/99

Daraus ergibt sich mit  $R_B = 100 \text{ k}\Omega$  (Faustformel  $R_B \approx 10 \cdot R_C$ ) aus der Gleichung  $R/R_B = (5 \text{ V} - U_{BE})/(U_{BE} - 0.25 \text{ V})$

ein Wert von

$$R \approx 1.41 \text{ M}\Omega$$

Die Rechnung ist nicht ganz korrekt, da sie von einem unbelasteten Spannungsteiler ausgeht und somit I<sub>B</sub> vernachlässigt. Praktisch wird man deshalb, auch wegen der Bauteiltoleranzen, die Rechnung oben gar nicht so genau durchführen, sondern R, wie in Bild 5-3 angedeutet, variabel wählen, und dann den Arbeitspunkt mit dem Potentiometer einstellen.

## Verstärkung mit einem Operationsverstärker:

Der Aufwand für die Bauteile ist hier etwas größer, da Verstärker ≥ 1 DM kosten. Verwendbar ist z.B. der OP07.

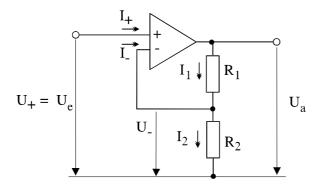

Bild 5-5: Verstärkung einer kleinen Eingangsspannung mit OP und Widerstandskombination

Nimmt man für die Schaltung in Bild 5-5 an, daß die Eingangs-Offsetspannung den Wert 0 hat  $(U_+ = U_- \Rightarrow U_a = 0)$ , so erzwingt der OP infolge seiner hohen Verstärkung (um  $10^5$ ) und infolge der Rückkoppelung über  $R_1$  zum **invertierenden** Minuseingang eine Spannungsdifferenz von  $U_+ \approx U_-$ . Damit wird  $U_- \approx U_+ = U_e$ . Ferner sind die Eingangswiderstände eines Operationsverstärkers so groß, daß man näherungsweise mit  $I_+ \approx 0$  und  $I_- \approx 0$  rechnen kann. Folglich ist  $I_1 \approx I_2$ . Damit wird

$$U_a = R_1 \cdot I_1 + R_2 \cdot I_2 = R_2 I_2 (R_1 I_1 / R_2 I_2 + 1) \approx U_e (R_1 I_1 / R_2 I_2 + 1)$$

oder

$$U_a \approx U_e (R_1 / R_2 + 1)$$

Ge V 5 - 4 9/99

## Aufgabe 5-1:

Berechnen Sie das Verhältnis der Widerstände in Bild 5-5, das eine Spannungsverstärkung von 10:1 bewirkt. Geben Sie vernünftige Widerstandswerte für R<sub>1</sub> und R<sub>2</sub> an.

## 5.1.3 Stromverstärkung mit Darlingtonschaltung

Was ist zu tun, wenn zwar der Hub der Eingangsspannung ausreicht, wenn aber die Spannungsquelle keinen hinreichend großen Strom liefert? Im Dimensionierungs-beispiel von Abschnitt 4.2 mußte  $I_B$  wegen B=250 mindestens 60  $\mu$ A betragen, damit der geforderte Strom  $I_C$  für die Leuchtdiode fließen konnte. Was ist zu tun, wenn die Spannungquelle in diesem Fall z.B. nur 10  $\mu$ A liefern kann?

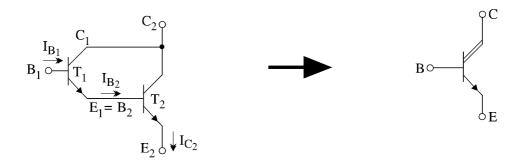

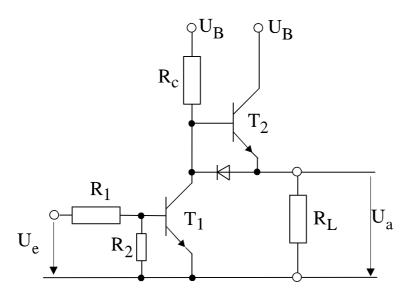

Antwort: Man muß den Strom in mehreren Stufen verstärken. Dazu kann die **Darlingtonschaltung** dienen. Siehe dazu Bild 5-6.

Bild 5-6: Darlingtonschaltung mit 2 Transistoren und Symbol für diese Schaltung (rechts)

Die Stromverstärkung der Darlingtonschaltung nach Bild 5-6 beträgt  $B = B_1 \cdot B_2$ . Das ergibt sich aus der Betrachtung der Ströme  $I_{B_1}$ ,  $I_{B_2}$ ,  $I_{C_2}$ .

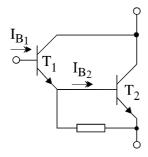

Bemerkung: Man kann T2 in der Darlingtonschaltung schneller sperren, wenn man einen zusätzlichen Widerstand gemäß Bild 5-7 einbaut. So können die Ladungsträger schneller abfließen, wenn  $I_{\rm B2}$  auf 0 zurückgeht

Bild 5-7: Verbesserte Darlingtonschaltung

Ge V 5 - 5 9/99

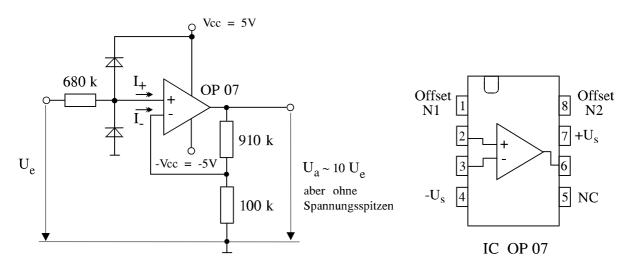

#### 5.1.4 Schutz vor zu großen Eingangsspannungen

In vielen Fällen muß damit gerechnet werden, daß kleine Eingangsspannungen entweder von Störungen überlagert werden, oder daß beim Umschalten von high zu low oder umgekehrt kurzfristig Spannungsspitzen entstehen, welche die nachfolgenden Transistoren, Verstärker usw. zerstören können. Die übliche Gegenmaßnahme sind Dioden. Bild 5-8 zeigt eine solche Schutzschaltung, die außerdem einen im Normalfall zu kleinen High-Pegel verstärkt. Der Vorwiderstand R muß klein sein gegen den Eingangswiderstand des Operationsverstärkers. Er dient dem Schutz der Dioden im Falle von Spannungsspitzen, die in diesem Beispiel bis zu 300 V betragen sollen. Da der OP 07 einen Eingangswiderstand von 7 M $\Omega$  hat, kann man z.B. R = 680 k $\Omega$  wählen. Das scheint hoch, doch muß man an die Verlustleistung im Widerstand beim Eintreffen einer Spannungsspitze denken. Wegen N = U²/R erhält man bei U = 300 V einen Wert N = 0.13 W, den ein normaler Widerstand verträgt. Dagegen wäre R = 68 k $\Omega$  mit N = 1.3 W deutlich zu klein!

Bild 5-8: Eingangsschaltung mit Diodenschutz und Verstärker. Angenommen wird eine Eingangsspannung zwischen 0 und 0.5 V mit Spitzen beim Umschalten von bis zu 300 V. Die Ausgangsspannung liegt dann - störungsfrei - zwischen 0 und 5 V.

## 5.1.5 Entprellschaltungen

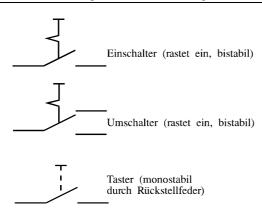

Häufig werden Eingangsspannungen über Taster oder Schalter manuell geschaltet. In diesem Fall ist es wichtig, daß nicht durch Prellen ein mehrfacher Spannungswechsel vorgetäuscht wird. Dagegen helfen "Entprellschaltungen". Bild 5-9 zeigt einige gebräuchliche Schalter bzw. Taster.

Ge V 5 - 6 9/99

Bild 5-9: Symbole von Schaltern (bistabil) und Tastern (monostabil)

Beim Betätigen eines Tasters oder Schalters rechnet man mit Prellzeiten im 1 ms-Bereich oder darunter. Dies ist beim Entwurf einer Entprellschaltung zu beachten.

## Entprellschaltung mit RC-Glied:

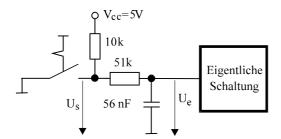

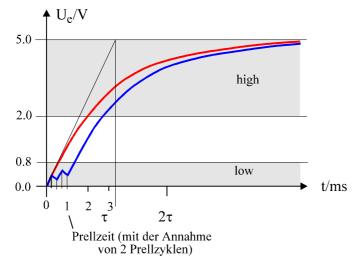

Bild 5-10 zeigt die Schaltung selbst, Bild 5-11 das Verhalten der Eingangsspannung  $U_e$  beim Öffnen des Einschalters, d.h. beim Übergang der speisenden Spannung  $U_s$  von high zu low im Zeitpunkt t=0.

Bild 5-10: Entprellschaltung

Bild 5-11: Eingangsspannung U<sub>e</sub> von Bild 5-10 beim Prellen

Ge V 5 - 7 9/99

Erläuterung zur Dimensionierung in Bild 5-10: Bei den üblicherweise angenommenen Prellzeiten unter oder gleich 1 ms wird gewünscht, daß beim Wechsel der treibenden Spannung  $U_s$  in Bild 5-10 die Eingangsspannung  $U_e$  solange im Low-Bereich bleibt, bis das Prellen nach 2, 3 oder mehr Zyklen beendet ist. Das RC-Glied soll also die Sprünge von  $U_e$  nach dem Prinzip von Bild 5-11 dämpfen. Bei der Annahme von 1 ms Prellzeit muß daher  $\tau$  so gewählt werden, daß  $U_e$  nicht größer als 0.8 V wird. Da  $U_e$  aber nur während der Hälfte der Prellzeit steigt, sonst aber fällt, ist man auf der sicheren Seite, wenn man  $\tau$  so wählt, daß  $U_e$  nach 0.5 ms noch kleiner oder gleich 0,8 V ist. Für  $U_e$  ohne Prellen gilt

$$U_e = 5V(1 - e^{-t/\tau})$$

Mit  $t = 0.5 \,\text{m}\,\text{s}$ ,  $U_e = 0.8 \,\text{V}$  folgt daraus

$$1 - e^{-t/\tau} = 0.8V / 5.0V = 0.16$$

oder

$$e^{-t/\tau} = 0.84$$

oder

$$t/\tau = \ln(1/0.84) = 0.1743$$

Damit wird

$$\tau \ge t / 0.1743 = 0.5 \text{ ms} / 0.1743 \approx 2.9 \text{ ms}$$

Das läßt sich mit R = 51 k und C = 56 nF wegen RC =  $51.56.10^3.10^{-9}$   $\Omega$  = 2.86 ms nahezu erreichen. Zu beachten ist, daß wegen des notwendigen Pullup-Widerstandes von 10 kΩ die Zeitkonstante  $\tau = 61.56.10^{3}.10^{-9}$  Ω = 3.42 ms, also etwas größer wird. Man könnte auch 510 k und 5.6 nF wählen. Dann wäre aber der maximale Eingangsstrom, der durch die Summe von Entprellwiderstand und Pullabwiderstand bestimmt wird, vermutlich zu klein. Bei der Wahl gemäß Bild 5-10 dagegen ergibt sich  $I_e = 5 \text{ V} / (10 \text{ k} + 51 \text{ k}) \approx 80 \,\mu\text{A}$ . Das ist zum Ansteuern eines Transistors (siehe Beispiel in Abschnitt 4.2) ausreichend. Man sieht aber, daß bei der Wahl der RC-Kombination dieser Gesichtspunkt von entscheidender Bedeutung ist. Meist werden deshalb Entprellschaltungen der Einfachheit halber mit Flipflops realisiert. Dazu trägt auch bei, daß ein für das Entprellen erforderliches zu großes τ unter Umständen den Anstieg von Ue so sehr verzögert, daß die Flankensteilheit für die Folgeschaltung zu gering ist. Man müßte dann noch einen Schmitt-Trigger nachschalten. Trotzdem ist das Entprellen mit RC-Glied manchmal nützlich, z.B. dann, wenn bei einem Serienprodukt die ursprünglich vorgesehenen entprellten Schalter wegen Lieferschwierigkeiten nicht rechtzeitig verfügbar sind. Dann läßt sich die fertige Platine leichter mit Widerstand und Kondensator nachbessern als mit einem IC und seinem vorgegebenen Pinmuster.

Ge V 5 - 8 9/99

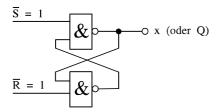

## Entprellschaltung mit Flipflop:

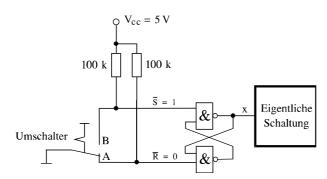

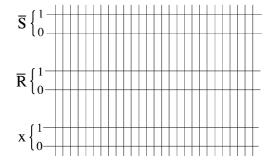

Mit Hilfe von zwei NAND-Gattern läßt sich eine **bistabile Kippschaltung**, ein sogenanntes "Flipflop" aufbauen. Wie man durch Studium von Bild 5-12 erkennt, bleibt eine der beiden stabilen Zustände x = 0 oder x = 1 bestehen, solange die Eingänge  $\neg S$  (von Set = setzen) und  $\neg R$  (von Reset = Rücksetzen) beide auf high (logisch 1) liegen. Dagegen setzt bereits ein kurzer Low-Impuls am Eingang  $\neg S$  den Ausgang x = 1 (bzw. beläßt es bei diesem Wert, wenn er schon eingestellt war). Entsprechend verursacht ein Low-Impuls an  $\neg R$  die Einstellung x = 0. Man nennt deshalb ein solches Flipflop auch RS-Flipflop.

Bild 5-12: RS-Flipflop aus zwei NAND-Gattern

Beim Einsatz von Flipflops zum Entprellen benötigt man einen **Umschalter**. Ein Einschalter oder Taster läßt sich wegen nur zwei statt drei Anschlüssen so nicht entprellen. Bild 5-13 zeigt die Schaltung, Bild 5-14 ein Zeitdiagramm beim Schalten von Kontakt A zu Kontakt B.

Bild 5-13: Entprellen eines Umschalters mit Hilfe eines RS-Flipflops

Bild 5-14: Zeitdiagramm beim Schalten von A nach B in Bild 5-13

| Ge   | V = 0   | Q/QQ |  |

|------|---------|------|--|

| ( †A | V 5 - 9 | 4/44 |  |

|      |         |      |  |

## **Entprellen mit Software:**

Enthält eine Schaltung einen Prozessor, so kann man auch auf die Hardwareentprellung der Eingabedaten verzichten und diese Aufgabe der Software übertragen. Auf solche Techniken wird in der Vorlesung über Mikroprozessoren eingegangen.

# 5.2 Logikschaltungen

Unter diesem Begriff soll hier der Teil der Schaltung verstanden werden, der die logische Funktion gewährleistet. Nach dem bisherigen Verständnis kann man sich darunter eine Black Box mit n Eingangs- und m Ausgangsleitungen vorstellen, die aus jeder Signalkombination auf den n Eingangsleitungen eindeutig eine Signalkombination auf den m Ausgangsleitungen erzeugt. Man spricht in diesem Fall auch von Schaltnetzen oder von kombinatorischer Logik. Später wird eine andere Art von Black Box betrachtet, welche zusätzlich Speicher enthält, und deren Ausgangssignale dann nicht nur von den Eingangssignalen abhängen, sondern auch vom Inhalt des Speichers, oder wie man sagt, vom "inneren Zustand". In diesem Fall spricht man von Schaltwerken oder von sequentieller Logik.

Logikschaltungen werden heute nicht mehr aus einzelnen Transistoren aufgebaut, sondern aus integrierten Schaltkreisen oder "Integrated Circuits", kurz ICs genannt. Doch enthalten die ICs letzten Endes auch nur die herkömmlichen Bauelemente, wenn auch in miniaturisierter Form. Es treten also die gleichen Fragen auf wie bei diskreten Schaltungen. Einige davon werden nachstehend behandelt.

#### 5.2.1 Störabstände

Es gibt verschiedene Methoden, logische Gatter wie AND, NAND, NOR usw. aus Transistoren, Widerständen und anderen Bauelementen aufzubauen. Auch die Betriebsspannungen  $U_B$  variieren. Je nach Schaltung und Wahl der Parameter ergeben sich daraus unterschiedliche sogenannte **Logikfamilien**. Eine der bekanntesten unter ihnen ist die Familie **TTL** gleich **T**ransistor-**T**ransistor-**L**ogik. Hier ist festgelegt:  $U_B = 5$  V,  $U_H = 2.0$  V und  $U_L = 0.8$  V für Eingangsspannungen. D.h. Eingangsspannungen  $\geq 2.0$  V werden als high erkannt und Eingangsspannungen  $\leq 0.8$  V als low. Andererseits werden bei korrektem Betrieb (siehe Abschnitt 5.2.2) die Ausgangsspannungen  $U_{OH} \geq 2.4$  V und  $U_{OL} \leq 0.4$  V garantiert. Die Abstände zwischen der Ausgangsspannunge einer bestimmten Schaltung und den festgelegten Grenzwerten der Eingangsspannungen nennt man die **Störabstände**  $S_H$  und  $S_L$ . Sie hängen nicht nur

von der Logikfamilie ab, sondern auch von der Schaltung und ihrer Belastung.

# Definition für den "worst case":

$$S_{H} \ = \ U_{OHmin} - U_{I\,Hmin}$$

$$S_L = U_{ILmax} - U_{OLmax}$$

S<sub>H</sub> heißt auch H-Störabstand, S<sub>L</sub> der L-Störabstand.

Für die TTL-Technik gilt im Extremfall (worst case), nämlich wenn man einen IC-Baustein mit nachgeschalteten ICs in gerade noch zulässiger Weise (siehe dazu Abschnitt 5.2.2) belastet,

$$S_H = 2.4 \text{ V} - 2.0 \text{ V} = 0.4 \text{ V}$$

$$S_{I} = 0.8 \text{ V} - 0.4 \text{ V} = 0.4 \text{ V}$$

Belastet man dagegen einen IC in normaler Weise, so gilt i.a.  $U_a \approx 0.1 \text{ V}$ , und daher

$$S_I = 0.8 \text{ V} - 0.1 \text{ V} = 0.7 \text{ V}$$

Auf alle Fälle ist der Abstand  $S_L$  in der TTL-Technik ziemlich gering. Bessere Werte hat z.B. die CMOS-Logik. Dort können die Störabstände wegen der variablen Spannung  $U_B$ , die bis zu 18 V betragen darf, wesentlich größer sein.

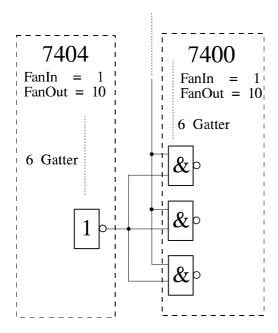

#### 5.2.2 FanIn, FanOut

Zur Vereinfachung arbeitet der Entwickler beim Schaltungsentwurf mit den Begriffen Fan In und Fan Out. D.h. er berechnet nicht für jeden Ausgang eines ICs die Belastung durch die nachfolgenden parallel geschalteten Bausteine, sondern er entnimmt den Bauteilekatalogen die jeweiligen FanIn- und FanOut-Werte. Dann genügt eine einfache Addition, um festzustellen, ob alle Bauteile noch im Rahmen des Zulässigen beansprucht werden. In der TTL-Technik geht das so:

Die Belastung eines IC-Ausgangs durch den Eingang eines 7400-NAND-Gatters wird als Einheitslast aufgefaßt. Man sagt, der 7400 habe einen FanIn von 1. Drei parallel liegende NAND-Gatter nach Bild 5-15 z.B. erzeugen nun 3 solcher Einheitslasten am Ausgang des links stehenden Bausteins 7404. Ist das zulässig? Das Datenblatt sagt "ja", denn der FanOut des Inverters 7404 beträgt 10 > 3.

Bild 5-15: FanIn und FanOut am Beispiel der TTL-Bausteine 7400 und 7404

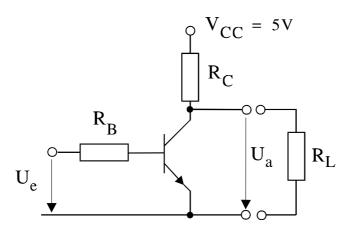

## 5.2.3 Minimierung der Verlustleistung

Logische Gatter sollen möglichst leistungslos arbeiten, und zwar in beiden Schaltzuständen. Der Inverter nach Bild 5-16 sollte daher ein möglichst **großes**  $R_C$  aufweisen, damit bei  $U_e$  = high und geöffnetem Transistor  $I_C$  möglichst klein wird. Andererseits sollte  $R_C$  bei  $U_e$  = low möglichst **klein** gegenüber  $R_L$  werden, damit bei gesperrtem Transistor der Spannungsteiler aus  $R_C$  und  $R_L$  ein möglichst großes  $U_a$  liefert. Dies ist im Grund die Forderung nach einem variablen Widerstand, der durch eine

Gegentaktendstufe oder "Totem Pole" Schaltung nach Bild 5-17 realisiert werden kann.

Bild 5-16: Widersprüchliche Forderungen an  $R_C$  für  $U_e$  = high und für  $U_e$  = low

Bild 5-17: Gegentaktendstufe oder Totem Pole Schaltung

#### Wirkungsweise:

- a)  $U_e = low: \Rightarrow T_1$  sperrt. Der Emitter von  $T_2$  liegt über  $R_L$  auf Masse, während das Basispotential auf  $U_B$  ansteigt. Die Diode D verhindert, daß der Emitter von  $T_2$  folgen kann. Damit öffnet  $T_2$ , und  $R_L$  wird praktisch **ohne** Vorwiderstand über  $T_2$  mit der Betriebsspannung  $U_B$  versorgt.

- b)  $U_e = high: \Rightarrow T_1$  öffnet. Der Emitter von  $T_2$  liegt bei ca. 0.1 V und ebenso die Basis von  $T_2$ . Damit sperrt  $T_2$ . Im Falle einer kapazitiven (statt ohmschen) Belastung durch  $R_L$  muß sich der Kondensator am Ausgang über D und  $T_1$  entladen, was bedeutet, daß  $U_a$  nicht unter 0.8 V sinken kann. Dann sperrt aber  $T_2$  erst recht. Es fließt jetzt nur ein Strom  $I_C$  über  $R_C$ . Dieser Widerstand darf folglich sehr groß sein, ohne daß er im Fall a) durch unerwünschte Spannungsteilung mit  $R_L$  stören kann.

# 5.3 Ausgangsschaltungen

Ausgangsschaltungen müssen häufig größere Ströme oder Spannungen liefern, für die logische ICs nicht ausgelegt sind. Deshalb wird hier auch heute noch gelegentlich mit diskreten Transistoren und anderen diskreten Bauelementen gearbeitet. Die Aus-legung dieser sogenannten Endstufen hängt davon ab, ob es sich um ohmsche, induktive (Spulen) oder kapazitive (Kondensatoren) Lasten handelt oder auch um eine Mischung. Hier wird nur kurz auf die drei Typen in "reiner" Form eingegangen.

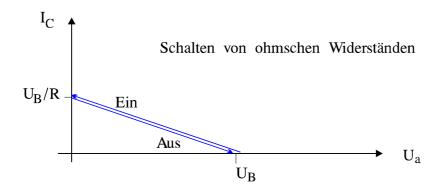

#### **5.3.1** Schalten ohmscher Lasten

Alle bisherigen Beispiele beruhten auf der Annahme einer ohmschen Last am Ausgang der Transistorschaltung. Zu beachten ist besonders, daß beim Ein- und Ausschalten des Transistors der Punkt  $(U_a,I_C)$  mit  $U_a=U_{CE}$  auf einer Geraden im  $U_{CE}$ - $I_C$ -Diagramm wandert.

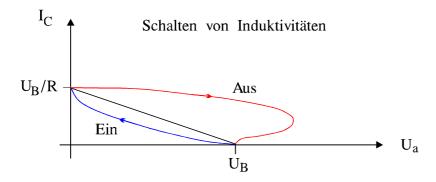

#### **5.3.2** Schalten induktiver Lasten

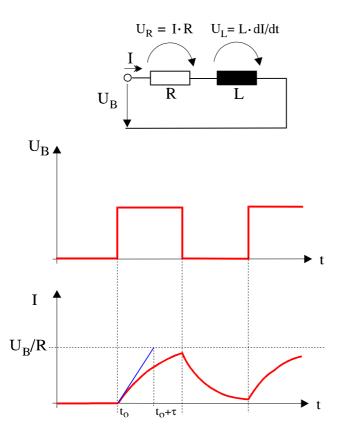

Beim Einschalten einer induktiven Last folgt der Strom einer sprunghaften Spannungsänderung verzögert als Exponentialfunktion. Siehe dazu Bild 5-18.

Bild 5-18: Durch Induktivität verzögerte Stromänderung bei sprungförmiger Spannung  $U_B$

$U = L \cdot dI/dt$

induzierte Spannung, die dieser Änderung entgegenwirkt. Bild 5-18 zeigt die Änderung des Stromes für eine Reihenschaltung von ohmschem und induktivem Widerstand bei sprungförmigem Verhalten der Spannung  $U_{\rm B}$ .

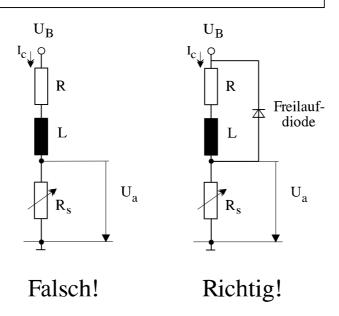

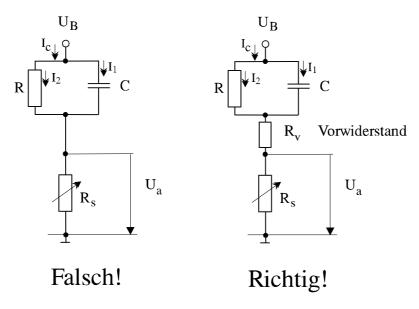

Schaltet man allerdings eine Induktivität als Last an den offenen Kollektor eines ICs oder Transistors, so ändert sich gar nicht  $U_B$ , sondern der Schaltwiderstand des Transistors gemäß Bild 5-19. Das hat beim Einschalten keinen anderen Effekt als bei einem Sprung der Betriebsspannung von 0 auf 5 V. Anders jedoch beim Ausschalten! Dem durch  $R_s \approx 0$  fließenden Strom  $I_C$  soll bei sprunghafter Änderung zu  $R_s \approx \infty$  eine sprunghafte Änderung zu 0 aufgezwungen werden. Das aber würde bedeuten

$$dI/dt = -\infty$$

was physikalisch nicht möglich ist. Praktisch gibt es allerdings keinen Sprung in  $R_s$  beim Sperren des Transistors, sondern nur einen sehr raschen Anstieg von einigen  $\Omega$  auf einige  $M\Omega$ . Die Folge ist eine sehr hohe induzierte Spannung  $U_L$ , die versucht, den Strom möglichst ungeändert durch den Transistor zu treiben. Das kann zu seiner Zerstörung führen. Man muß deshalb beim Schalten induktiver Lasten eine <u>Freilauf</u>diode vorsehen, die das verhindert. Siehe dazu Bild 5-19.

# Schalten von induktiven Lasten

Bild 5-19: Schalten einer Induktivität. Links falsch, rechts richtig.

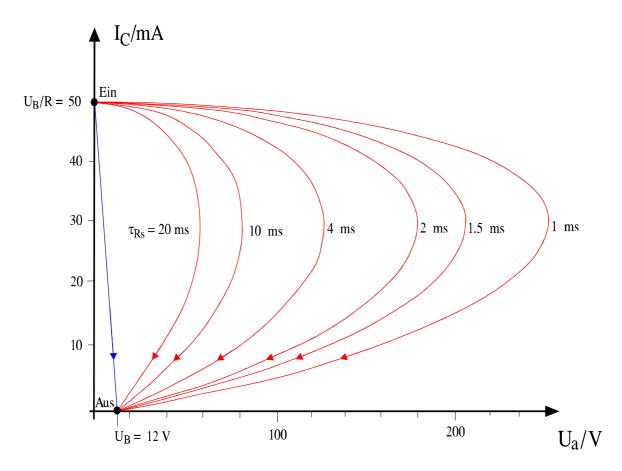

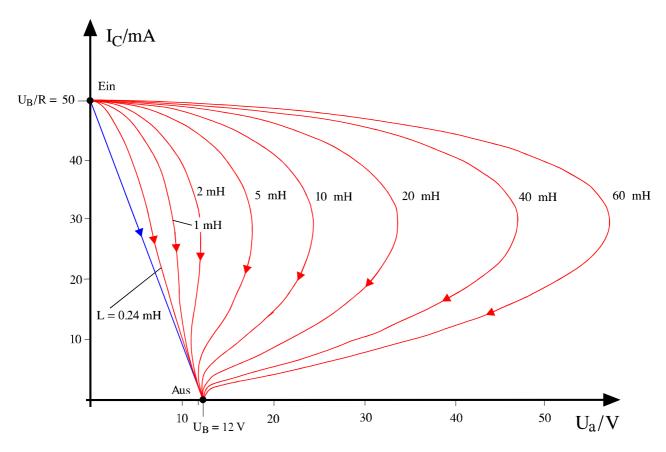

Beim Einschalten und besonders beim Ausschalten einer Induktivität bewegt sich der Punkt ( $U_a$ , $I_C$ ) nicht auf einer Geraden, sondern auf gekrümmten Linien, die von der Bewegungsrichtung abhängen! Beim Einschalten ist die Abweichung von der Geraden unbedeutend, beim Ausschalten dagegen in Abhängigkeit von der Schaltgeschwindigkeit erheblich. Macht man die vereinfachende Annahme, daß sich beim Sperren eines Transistors sein Widerstand exponentiell von 0 bis auf einen sehr hohen Widerstand  $R_\infty$  verändert, läßt sich diese Kurve relativ einfach numerisch ermitteln. Bild 5-20 zeigt einige dieser Kurven in Abhängigkeit von  $\tau_{Rs}$ , der Zeitkonstante dieser Widerstandsänderung.

Bild 5-20: Spannungsüberhöhung beim Ausschalten einer Induktivität in Abhängigkeit von der Schaltgeschwindigkeit, die von  $\tau_{Rs}$  bestimmt wird. Je kleiner  $\tau_{Rs}$ , umso größer ist die Schaltgeschwindigkeit. Angenommen wurde:

$$U_B = 12 V$$

(siehe Bild 5-19)

$R = 240 \Omega$

$L = 60 \text{ mH}$

$R_{\infty} = 1 M\Omega$

Natürlich spielt auch das Verhältnis von R zu L einer Rolle. Bild 5-21 zeigt das für verschiedene Induktivitäten bei  $\tau_{Rs} = 20$  ms für verschiedene Induktivitäten.

Bild 5-21: Spannungsüberhöhung beim Ausschalten einer Induktivität in Abhängigkeit von der Größe dieser Induktivität bei konstanter Schaltgeschwindigkeit. Angenommen wurde:

$U_B = 12 V$  (siehe Bild 5-19)  $R = 240 \Omega$   $t_{RS} = 20 ms$  $R_{\infty} = 1 M\Omega$

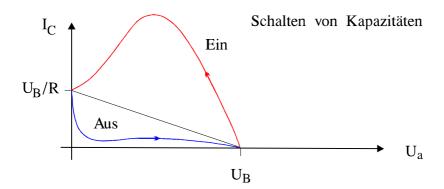

## **5.3.3** Schalten kapazitiver Lasten

Kapazitäten und Induktivitäten verhalten sich dual. Während bei der Induktivität das **Aus**schalten kritisch ist und **Spannungs**überhöhungen bis zu einigen 100 V bewirken kann, ist bei Kapazitäten das **Ein**schalten gefährlich. Ohne Gegenmaßnahmen führt es zu **Strom**überhöhungen. Bild 5-22 zeigt das Prinzip.

# Schalten von kapazitiven Lasten

Bild 5-22: Schalten einer Kapazität. Links falsch, rechts richtig.

## Begründung:

- a) Beim Einschalten (Übergang  $R_s$  von  $\infty$  zu 0) wirkt die Kapazität C als Kurzschluß, da sie vorher das Potential  $U_B$  angenommen hat und dieses erst allmählich mit dem Abtransport der Ladung verliert. Es wird also  $U_B$  praktisch widerstandslos mit Masse verbunden. Dies führt zu einem sehr hohen Strom durch  $R_s$ , d.h. den Transistor, der so zerstört werden kann. mit dem Vorwiderstand  $R_v$  kann man das verhindern.

- b) Das Ausschalten dagegen ist ungefährlich. Der Strom  $I_1$  (s. Bild 5-21) lädt den Kondensator auf, wobei er nach einer Exponentialfunktion gegen 0 strebt.

Wie in Abschnitt 5.3.2 kann man auch hier Annahmen über den Schaltvorgang im Transistor treffen und daraus Kurven für verschiedene Schaltgeschwindigkeiten und verschiedene Werte von C und R ermitteln. Doch soll darauf verzichtet werden. Die Kurven sind "dual" zu denen in Bild 5-20 und 5-21. D.h. die Überhöhung betrifft nicht die Spannung, sondern den Strom und führt deshalb zu Ausbauchungen in vertikaler statt in horizontaler Richtung.

Bild 5-23 gibt eine qualitative Zusammenfassung der Verhältnisse beim Ein- und Ausschalten von ohmschen, induktiven und kapazitiven Lasten.

Bild 5-23: Schalten von ohmschen, induktiven und kapazitiven Lasten. Zusammenfassung.