# Solid State Voice Recorder Using Flash MSP430

Murugavel Raju

Mixed Signal Controllers

#### ABSTRACT

The promise of cost-effective re-programmable MSP430 MCU systems has recently come to fruition with the integration of In-System Programmable (ISP) flash memory. Firmware delivered just in time during manufacturing, updateable code in field-deployed systems, and the elimination of discrete EEPROMs are now design realities. This application report demonstrates the flexibility of in-system programmable flash by implementing a solid state voice recorder. Not only does the MSP430 convert the analog voice pattern to digital with the integrated analog-to-digital converter, but also the voice data is stored real-time in the MCU Flash memory and played back. This application demonstrates the ability to use the same memory array for both program execution and dynamic data storage.

#### Contents

| 1 Introduction             | 1 |  |

|----------------------------|---|--|

| 2 Hardware                 | 2 |  |

| 2.1 System Overview        |   |  |

| 2.2 Analog Hardware        | 3 |  |

| 2.3 Digital Hardware       | 5 |  |

| 3 Software                 | 6 |  |

| 4 Code F149 Voice Demo.s43 |   |  |

| References                 |   |  |

|                            |   |  |

#### Figures

| Figure 1. | Block Diagram                       | 2 |

|-----------|-------------------------------------|---|

| Figure 2. | Microphone Pre-amplifier and Filter | 3 |

| Figure 3. | Serial DAC and Filter               | 4 |

| Figure 4. | Audio Power Amplifier               | 5 |

|           | MSP430F149 Schematic                |   |

| 0         |                                     |   |

### 1 Introduction

The introduction of the flash MSP430 microcontrollers has opened up flexibility in today's microcontroller application designs. The in-system programmability of the flash and retention time of data in flash for tens of years makes the device ideally suited for these applications. This application is designed using the MSP430F149, the member of the 1xx family of MSP430 flash microcontrollers. This device was chosen as it has 60K bytes of flash memory to hold up to 10 seconds of speech and integrated 12-bit A/D converter to digitize the analog voice signal.

This application demonstrates the following:

In-system erasing and programming of flash memory in flash MSP430

- Real-time Flash programming in MSP430

- Running the MSP430x13x / 14x using XT2 HF XTAL

- Using the integrated A/D converter ADC12 in real-time data conversion

- Interfacing TI data converter TLV5616 with MSP430

- Application of TI opamp TLV2252 and power amplifier TPA721 in MSP430 mixed signal circuits

- MSP430 mixed-signal operation with 3-V battery

## 2 Hardware

#### 2.1 System Overview

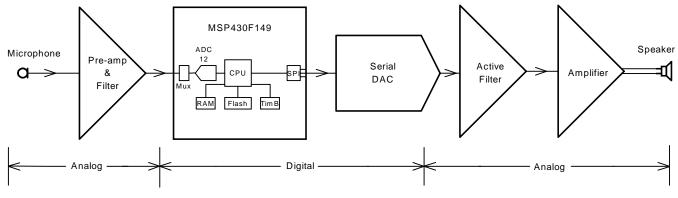

Figure 1 shows the block diagram of the application setup. The analog and digital blocks are marked accordingly. Arrowheads show the signal path from the microphone to the speaker. The peripherals used actively in this application are shown internal to the MSP430F149 block. Notice the integrated 12-bit analog to digital converter ADC12. The analog multiplexer integrated in the MSP430F149 allows 8 channels of analog data to be input to the ADC12. In this application only one channel 'A0' is used as analog input. The pre-amplified and filtered analog voice signal is directly input to the analog input 'A0' of the MSP430. During record, only the first two blocks are active and during playback the last two blocks are the active blocks. During playback the stored voice signal data is sent to the serial DAC via the MSP430 USART SPI. The active filter filters the edges from the digital to analog converter output. This filtered signal is then amplified by the amplifier section and drives a speaker to play back the stored voice information.

### 2.2 Analog Hardware

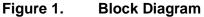

Figure 2. Microphone Pre-amplifier and Filter

Figure 2 shows the microphone pre-amplifier and the filter circuit. The condenser microphone picks up the voice and converts it into an analog signal. The analog voice signal is then amplified by a TI opamp TLV2252. Reference [3] is the datasheet for this device. The TLV2252 is a lowvoltage and low-power dual opamp, one of which is used for microphone signal amplification and the other in an active low-pass filter circuit associated with the DAC. The TLV2252 is chosen because of its capability to operate at 3 Volts with a low operating current. The amplified analog signal is bandwidth limited to the required voice spectrum before it is input to the integrated A/D converter of the MSP430F149. A simple RC filter at the output does the bandwidth limiting with a cutoff frequency approximately 2.7 KHz. The capacitor C4 across the feedback path also provides some high frequency roll-off. Technically this filter is the antialiasing filter and is required to avoid frequency aliasing of the input signal after sampling. Bandwidth limiting to 2.7 KHz is essential to satisfy the Nyquist requirement as a sampling frequency of 5.5 KHz is used in this application. The sampling frequency of 5.5 KHz is chosen as a tradeoff between voice guality and maximum duration of voice that can be stored in the flash memory. With the above values, approximately six seconds of speech can be stored in the flash. The digitized 12-bit voice data is directly stored in the flash without any compression. Compressing the voice data using A-law or  $\mu$ -law to 8-bits doubles the storage time to 12 seconds.

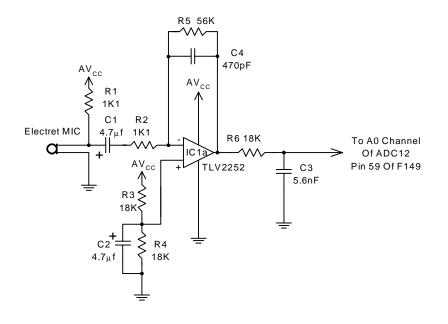

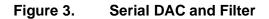

Figure 3 shows the serial DAC and the output filter circuit. The TI data converter device TLV5616 DAC used in this application features 3-V operation with less than 0.5 LSB DNL. Reference [4] is the datasheet for this device. The DAC interfaces with the integrated hardware USART of the MSP430 configured in SPI mode. The MSP430 SPI handles the required 16-bit word transfer to the DAC by taking advantage of the double-buffering capability of the integrated hardware USART module. The TLV5616 is a voltage output DAC that directly interfaces with the output filter circuit built with the TLV2252 opamp. This filter is a second-order Sallen-Key active low pass filter circuit that filters the sampling edges from the DAC output. The filtered output needs further amplification before it can be made audible by the speaker.

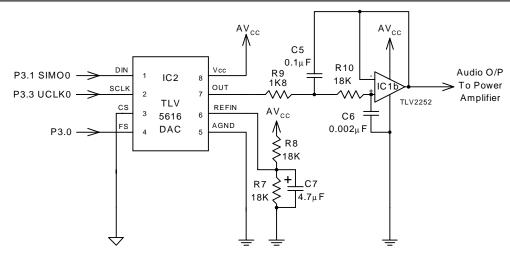

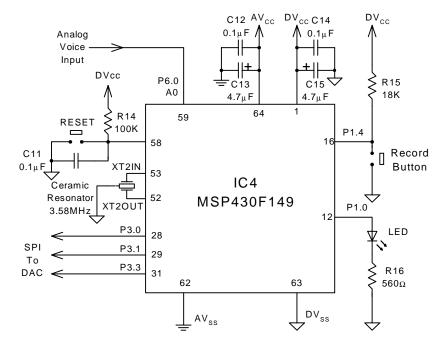

Figure 4 shows the audio power amplifier circuit. It is based on the TI audio power amplifier device TPA721. Reference [5] is the datasheet for this device. The TPA721 has a wide power supply compatibility of 2.5 V to 5 V. The BTL (bridge-tied load) design of the output stage of the TPA721 provides approximately 6  $V_{PP}$  drive to an 8-ohm speaker at a supply voltage of 3 Volts. The BTL also eliminates the need for a speaker coupling capacitor. The TPA721 is available in an MSOP footprint called the PowerPAD<sup>TM</sup> that allows a compact PCB design to be realized. Notice that an RC low pass filter built around R13 and C9, also known as the power supply decoupling circuit, is shown in Figure 4. This RC circuit filters the voice signal superimposed on the battery supply by the power amplifier, before it is fed to the analog circuitry.

Audio Power Amplifier

### 2.3 Digital Hardware

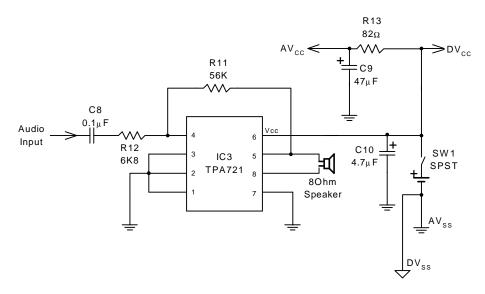

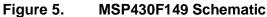

The digital hardware is the MSP430F149 flash microcontroller and its associated passive components. Reference [1] is the datasheet for this device. The integrated peripherals simplify the digital design and this application is a good example for MSP430 being a "System in a Chip." A 3.58-MHz ceramic resonator clocks the MSP430. The resonator used in this application has built-in load capacitors for the internal clock oscillator circuit. Timer B7 is used to generate the timed interrupts for the sampling frequency. Timer B7 is clocked by the stable 3.58-MHz clock as any jitter in this would reflect as jitter in the sampling frequency and affect the voice quality. The sampled analog voice signal is digitized by the integrated ADC12 peripheral of the MSP430. Take care in interfacing the analog and digital circuits. Notice that the analog and digital grounds are separately shown. Also the analog and digital supplies must be separated out as shown in the schematic. Refer to page 331, figure 15-26 of the MSP430x1xx Family User's Guide, reference [2], for recommended A/D grounding and noise considerations.

The digitized voice data is stored sequentially in the flash memory. Refer to page 413, Appendix C of the MSP430x1xx Family User's Guide, reference [2], for details on flash memory access. During playback the stored data is transmitted in the same sequence as it was stored and using the same sampling frequency, to the serial DAC via the hardware USART in SPI mode. The DAC converts these data patterns to the original voice signal and the following filter and amplifier circuit renders it audible via the speaker.

### 3 Software

The code for this application is written in assembly language, using the IAR KickStart integrated development environment. The MSP430F149 has 120 segments of main memory starting from 1100h to FFFFh. Segment 0 to segment 118 are 512 bytes wide and segment 119 is 256 bytes wide. Segment 0 carries the interrupt vectors and must not be modified during run time. Two more segments called Segment A and B each 128 bytes wide are allocated as information memory in the device. The user can use this information memory for storing device identification codes. The information memory can also be used to substitute an EEPROM or can be used to store executable codes depending on the assembler definition. The information memory is left unused in this application. Refer to page 16 of MSP430F149 datasheet, reference [1], for memory mapping of the flash memory in the device.

The executable code for this application vectors at 1100h, the start address of the main memory. The compiled code size is 346 bytes and occupies segment 119 (256 bytes) and segment 118 (90 bytes out of 512 bytes). Segment 0 is programmed with the interrupt vectors. The remaining segments 1 to 117 are allocated by software to store the digitized voice data. This is referred to as record memory array and is 117 segments wide (59904 bytes) starting at 1400h and ending at FDFFh. During recording the voice data words are sequentially written into this flash memory array, and during playback the voice data words are sequentially read from this array.

The software implemented runs the application in two modes, Playback and Record, depending on the status of the record push button. As soon as the system is switched ON it goes to the playback mode and plays back any previously recorded voice message. The playback is repeated continuously as long as the system is switched ON. To enter Record mode the following steps are to be followed. While the system plays back a message hold the Record button. The LED lights up in a moment indicating that the flash memory is erased and ready for a new recording. Release the button and speak into the microphone. The voice is stored in the flash and when the Record Memory array reaches its capacity the LED goes OFF, indicating that the recording is over. Now the recorded voice is automatically played back as long as the system is switched ON.

Note that the flash memory can be erased and programmed only if the MSP430 supply voltage is greater than or equal to 2.7 V. Please refer to the device specific datasheet. If it falls below 2.7 V because of the draining battery, the system cannot record voice. However, it plays back the previously stored message a few more times until the voltage drops below the operational level of the analog circuitry.

**Note:** This is not intended to be a speech application and is only an example to demonstrate the real-time in-system programmability (ISP) of the flash and the digital signal processing (DSP) capability of the MSP430. To keep the application simple no voice compression is implemented, only the PCM data is stored and playback. TI has a whole range of speech devices, please visit

http://www.ti.com/sc/docs/products/speech/index.htm for more details.

# 4 Code F149 Voice Demo.s43

;

;

; THIS PROGRAM IS PROVIDED "AS IS". TI MAKES NO WARRANTIES OR

; REPRESENTATIONS, EITHER EXPRESS, IMPLIED OR STATUTORY,

; INCLUDING ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS

; FOR A PARTICULAR PURPOSE, LACK OF VIRUSES, ACCURACY OR

; COMPLETENESS OF RESPONSES, RESULTS AND LACK OF NEGLIGENCE.

; TI DISCLAIMS ANY WARRANTY OF TITLE, QUIET ENJOYMENT, QUIET

; POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY

; INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO THE PROGRAM OR

; YOUR USE OF THE PROGRAM.

;

;

; IN NO EVENT SHALL TI BE LIABLE FOR ANY SPECIAL, INCIDENTAL,

; CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY

; THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED

; OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT

; OF THIS AGREEMENT, THE PROGRAM, OR YOUR USE OF THE PROGRAM.

#### SLAA123

; EXCLUDED DAMAGES INCLUDE, BUT ARE NOT LIMITED TO, COST OF ; REMOVAL OR REINSTALLATION, COMPUTER TIME, LABOR COSTS, LOSS ; OF GOODWILL, LOSS OF PROFITS, LOSS OF SAVINGS, OR LOSS OF ; USE OR INTERRUPTION OF BUSINESS. IN NO EVENT WILL TI'S ; AGGREGATE LIABILITY UNDER THIS AGREEMENT OR ARISING OUT OF ; YOUR USE OF THE PROGRAM EXCEED FIVE HUNDRED DOLLARS ; (U.S.\$500). ; Unless otherwise stated, the Program written and copyrighted ; by Texas Instruments is distributed as "freeware". You may, ; only under TI's copyright in the Program, use and modify the ; Program without any charge or restriction. You may ; distribute to third parties, provided that you transfer a ; copy of this license to the third party and the third party ; agrees to these terms by its first use of the Program. You ; must reproduce the copyright notice and any other legend of ; ownership on each copy or partial copy, of the Program. ; You acknowledge and agree that the Program contains ; copyrighted material, trade secrets and other TI proprietary ; information and is protected by copyright laws, ; international copyright treaties, and trade secret laws, as ; well as other intellectual property laws. To protect TI's ; rights in the Program, you agree not to decompile, reverse ; engineer, disassemble or otherwise translate any object code ; versions of the Program to a human-readable form. You agree ; that in no event will you alter, remove or destroy any ; copyright notice included in the Program. TI reserves all ; rights not specifically granted under this license. Except ; as specifically provided herein, nothing in this agreement ; shall be construed as conferring by implication, estoppel, ; or otherwise, upon you, any license or other right under any ; TI patents, copyrights or trade secrets. ; You may not use the Program in non-TI devices. F149VoiceDemo ; MSP430F149 Voice Recording in FLASH Demonstration NAME ;Author Murugavel Raju

# TEXAS INSTRUMENTS

| i                                            | Texas                                   | Instruments, Inc                        |                                     |  |  |  |

|----------------------------------------------|-----------------------------------------|-----------------------------------------|-------------------------------------|--|--|--|

| ; * * * * * * * * * * * * * * * * * * *      |                                         |                                         |                                     |  |  |  |

| #include                                     | "msp430x14x.h"                          |                                         |                                     |  |  |  |

| ; * * * * * * * * *                          | ; * * * * * * * * * * * * * * * * * * * |                                         |                                     |  |  |  |

| ;                                            | CPU runs from XT2 @3.58MHz              |                                         |                                     |  |  |  |

| ;                                            |                                         |                                         |                                     |  |  |  |

| ;                                            | Consta                                  | nts Definition                          |                                     |  |  |  |

| FS                                           | equ                                     | 001h                                    |                                     |  |  |  |

| Memstart                                     | equ                                     | 1401h                                   |                                     |  |  |  |

| Memend                                       | equ                                     | 0fe01h                                  |                                     |  |  |  |

| -<br>; * * * * * * * * * * * * * * * * * * * |                                         |                                         |                                     |  |  |  |

|                                              | RSEG                                    | CSTACK                                  |                                     |  |  |  |

|                                              | DS                                      | 0                                       |                                     |  |  |  |

| ;*******                                     | * * * * * * * *                         | * * * * * * * * * * * * * * * * * * * * | ********                            |  |  |  |

|                                              | RSEG C                                  | ODE                                     |                                     |  |  |  |

| ;*******                                     | * * * * * * * *                         | * * * * * * * * * * * * * * * * * * * * | **********                          |  |  |  |

| RESET                                        | mov.w                                   | #SFE(CSTACK),SP                         | ; define stackpointer               |  |  |  |

|                                              | call                                    | #Init_Sys                               | ; Initialize System                 |  |  |  |

|                                              | mov.b                                   | &P1IN,R5                                | ; Test P1.1 for mode                |  |  |  |

|                                              | and.b                                   | #BIT4,R5                                | ; Mask Bit4 to test 'Record' button |  |  |  |

|                                              | jnz                                     | Play                                    | ; Jump to Play if not pressed       |  |  |  |

|                                              | call                                    | #Erase                                  | ; Flash erase subroutine            |  |  |  |

|                                              | xor.w                                   | #FXKEY+WRT,&FCTL1                       | ; Enable FLASH write for recording  |  |  |  |

|                                              | bis.b                                   | #BIT0,&P1OUT                            | ; Led ON                            |  |  |  |

| Play                                         | eint                                    |                                         | ; Enable interrupts                 |  |  |  |

|                                              | mov.w                                   | #Memstart,R14                           | ; Start memory address to R14       |  |  |  |

| Mainloop                                     | jmp                                     | \$                                      | ; Keep looping, only ISR's          |  |  |  |

|                                              |                                         |                                         | ; are serviced                      |  |  |  |

| ; * * * * * * * * *                          | * * * * * * * *                         | * * * * * * * * * * * * * * * * * * * * | ***********                         |  |  |  |

| TB7_ISR;                                     | Timer                                   | B7 ISR samples and stores               | during RECORD                       |  |  |  |

| ;                                            | ; and send out data during PLAY         |                                         |                                     |  |  |  |

| ;*******                                     | * * * * * * * *                         | * * * * * * * * * * * * * * * * * * * * | ***********                         |  |  |  |

|                                              | bit.b                                   | #BIT4,R5                                | ; Test for mode button              |  |  |  |

|                                              | jnz                                     | Playl                                   | ; Jump to Play1 if not pressed      |  |  |  |

|                                              | bic.w                                   | #ADC12SC,&ADC12CTL0                     | ; Start conversion                  |  |  |  |

| Conv_tst                                     | bit.w                                   | #ADC12BUSY,&ADC12CTL1                   | ; Test for conversion complete      |  |  |  |

|                                              | jc                                      | Conv_tst                                | ; Loop till conversion complete     |  |  |  |

|                                              | bis.w                                   | #ADC12SC,&ADC12CTL0                     | ; back to sample mode               |  |  |  |

|                                              | mov.w                                   | &ADC12MEM0,0(R14)                       | ; Write word to FLASH               |  |  |  |

|           | incd.w | R14                               | ;   | Increment pointer                   |

|-----------|--------|-----------------------------------|-----|-------------------------------------|

|           | cmp.w  | #Memend,R14                       | ;   | Check if memarray full              |

|           | jnz    | Proceed                           | ;   | Jump to Proceed if not full         |

|           | bic.b  | #BIT0,&P1OUT                      | ;   | Led OFF if record memory array full |

|           | xor.w  | #FXKEY+WRT,&FCTL1                 | ;   | Disable FLASH write                 |

|           | xor.w  | <pre>#FXKEY+LOCK,&amp;FCTL3</pre> | ;   | Lock FLASH memory                   |

|           | jmp    | RESET                             | ;   | Loop again (will Playback if        |

|           |        |                                   | ;   | button released)                    |

| Play1     | mov.w  | @R14,R15                          | ;   | Read data from memory pointer       |

|           | Incd.w | R14                               | ;   | Double increment pointer to point   |

|           |        |                                   | ;   | to next data word                   |

|           | cmp.w  | #Memend,R14                       | ;   | Check if end of memarray            |

|           | jnz    | Go_on                             | ;   | Jump to Go_on if not end            |

|           | jmp    | RESET                             | ;   | Loop again if end                   |

| Go_on     |        |                                   |     |                                     |

| L1        | bit.b  | #UTXIFG0,&IE1                     | ;   | Loop to wait until previous         |

|           | jc     | L1                                | ;   | transmission done and buffer empty  |

|           | bis.b  | #FS,&P3OUT                        | ;   | Pulse Frame sync                    |

|           | bic.b  | #FS,&P3OUT                        | ;   | to start loading TLV5516 with       |

|           |        |                                   | ;   | next data word                      |

|           | swpb   | R15                               | ;   | Swap bytes in R15                   |

|           | mov.b  | R15,&TXBUF0                       | ;   | High byte to SPI TXBUF              |

|           | swpb   | R15                               | ;   | Swap bytes in R15                   |

|           | mov.b  | R15,&TXBUF0                       | ;   | Low byte to SPI TXBUF               |

| Proceed   | reti   |                                   | ;   | Return from ISR                     |

| ;*******  | ****** | ****                              | * * | ******                              |

| Init_Sys; | Setu   | up Peripherals                    |     |                                     |

| ;*******  | ****** | ****                              | * * | ******                              |

| StopWDT   | mov.w  | #WDTPW+WDTHOLD,&WDTCTL            | ;   | Stop Watchdog Timer                 |

| SetupBC   | bic.b  | #XTOFF,&BCSCTL1                   | ;   | XT2 ON                              |

|           | call   | #Delay                            | ;   | Delay for crystal stabilization     |

|           | mov.b  | #SELM1+SELS,&BCSCTL2              | ;   | MCLK=SMCLK=XT2CLK                   |

|           | bic.b  | #OFIFG,&IFG1                      | ;   | Clear OFIFG                         |

| SetupP1   | mov.b  | #0h,&P1OUT                        | ;   | Clear P1 output register            |

|           | bis.b  | #0ffh,&P1DIR                      | ;   | P1.0 for LED output                 |

|           |        |                                   | ;   | and unused pins as o/p's            |

|           | bic.b  | #BIT4,&P1DIR                      | ;   | For switch input                    |

| SetupP2   | mov.b  | #0h,&P20UT                        | ;   | Clear P2 output register            |

|           | bis.b  | #0ffh,&P2DIR                      | ;   | Unused pins as o/p's                |

|           |        |                                   |     |                                     |

# TEXAS INSTRUMENTS

| SetupP3               | bis.b             | #00ah,&P3SEL                                   | ;     | P3.1 & P3.3 SPI option select                            |

|-----------------------|-------------------|------------------------------------------------|-------|----------------------------------------------------------|

|                       | bis.b             | #FS,&P3OUT                                     | ;     | FS set                                                   |

|                       | bis.b             | #0feh+FS,&P3DIR                                | ;     | P3.0,3.1,3.3 & unsued pins o/p dir.                      |

| SetupP4               | mov.b             | #0h,&P4OUT                                     | ;     | Clear P4 output register                                 |

|                       | bis.b             | #0ffh,&P4DIR                                   | ;     | Unused pins as o/p's                                     |

| SetupP5               | mov.b             | #0h,&P50UT                                     | ;     | Clear P5 output register                                 |

|                       | bis.b             | #0ffh,&P5DIR                                   | ;     | Unused pins as o/p's                                     |

| SetupP6               | bis.b             | #BIT0,&P6SEL                                   | ;     | P6.0 = ADC12 A0 input                                    |

|                       | mov.b             | #0h,&P6OUT                                     | ;     | P6 output pins to reset                                  |

|                       | bis.b             | #0feh,&P6DIR                                   | ;     | P6.1 to 6.7 outputs (unused)                             |

| SetupADC              | Call              | #ADCset                                        | ;     | Initialize ADC12                                         |

| SetupUSART            | bis.b             | #040h,&ME1                                     | ;     | Enable USART module                                      |

|                       | mov.b             | #CHAR+SYNC+MM,&U0CTL                           | ;     | 8-bit SPI Master                                         |

|                       | mov.b             | #CKPL+SSEL1+SSEL0+STC,8                        | &U0   | TCTL                                                     |

|                       |                   |                                                | ;     | SMCLK for TX, 3-pin mode                                 |

|                       | mov.b             | #02h,&U0BR0                                    | ;     | SMCLK/2 for baud rate                                    |

|                       | clr.b             | &U0BR1                                         | ;     |                                                          |

|                       | clr.b             | &U0MCTL                                        | ;     | Clear Modulation                                         |

| SetupCCR0             | bis.w             | #CCIE,&TBCCTL0                                 |       |                                                          |

|                       | Mov.w             | #649,&TBCCR0                                   | ;     | Initialize TBCCR0 for sampling                           |

|                       |                   |                                                | ;     | frequency of 5.5Khz                                      |

| SetupTB7              | bis.w             | #TBSSEL1+MC0,&TBCTL                            | ;     | TimerB in UP mode                                        |

| SetupFlash            | xor.w             | #FXKEY+FN2+FN1+FN0,&FC                         | TL2   |                                                          |

|                       |                   |                                                | ;     | Set FLASH timing generator 447.5Khz                      |

|                       | ret               |                                                | ;     | Return from subroutine                                   |

| ,                     |                   |                                                |       | ********                                                 |

| ADCset;               |                   | ize ADC12, $V_{CC}$ as ADC Re                  |       |                                                          |

| ;<br>•********        | -                 | channel (A0) single-con                        |       | sion mode                                                |

| ,                     | bis.w             | #ADC12ON+ADC12SC+ENC,&A                        |       |                                                          |

|                       | DIS.W             | #ADCIZON+ADCIZSC+ENC, &                        |       |                                                          |

|                       | call              | #Delay                                         |       | Turn ON ADC12 & S/H in sample<br>Delay for stabilization |

|                       | bis.w             | #Delay<br>#ADC12SSEL 1+ADC12SSEL               |       |                                                          |

|                       | M.GTO             | <sup>₩</sup> חקפפדסראבד <sup>−</sup> דשחרדפפפד |       | ADC12C1L1<br>ADC12 Clock=SMCLK                           |

|                       | ret               |                                                |       | Return from subroutine                                   |

| ; * * * * * * * * * * |                   | * * * * * * * * * * * * * * * * * * * *        |       | **************************************                   |

|                       |                   |                                                |       |                                                          |

| Erase;                | Initial           | ize FCTL & Erase FLASH :                       | for   | new recording                                            |

| ; * * * * * * * * * * | * * * * * * * * * | *****                                          | * * * | *******                                                  |

|                       | dint              |                                                | ;     | Disable interrupts                                       |

|                       |                   |                                                |       |                                                          |

#### SLAA123

|                                         | xor.w           | <pre>#FXKEY+LOCK,&amp;FCTL3</pre>       | ;   | Unlock FLASH for write              |

|-----------------------------------------|-----------------|-----------------------------------------|-----|-------------------------------------|

| Test_Busyl                              | bit.w           | <pre>#BUSY,&amp;FCTL3</pre>             | ;   | Check BUSY flag                     |

|                                         | jnz             | Test_Busy1                              | ;   | Loop till not busy                  |

|                                         | mov.w           | #1400h,R13                              | ;   | Start of record memory array to R13 |

| NextSeg                                 | mov.w           | #(FWKEY+ERASE),&FCTL1                   | ;   | Set                                 |

|                                         | Clr.b           | 0(R13)                                  | ;   | Perform a dummy write to activate   |

|                                         |                 |                                         | ;   | segment erase                       |

| Test_Busy2                              | bit.w           | <pre>#BUSY,&amp;FCTL3</pre>             | ;   | Check BUSY flag                     |

|                                         | jnz             | Test_Busy2                              | ;   | Loop till not busy                  |

|                                         | add.w           | #200h,R13                               | ;   | Point to next segments              |

|                                         | cmp.w           | #0fe00h,R13                             | ;   | Check if all segments are erased    |

|                                         | jnz             | NextSeg                                 | ;   | If not proceed erasing next segment |

|                                         | ret             |                                         | ;   | Return from subroutine              |

| ; * * * * * * * * * *                   | * * * * * * * * | * * * * * * * * * * * * * * * * * * * * | * * | *******                             |

| Delay;                                  | Softwar         | e delay                                 |     |                                     |

| ; * * * * * * * * * * * * * * * * * * * |                 |                                         |     |                                     |

|                                         | push.w          | #0FFFFh                                 | ;   | Delay to TOS                        |

| DL1                                     | dec.w           | 0(SP)                                   | ;   | Decrement TOS                       |

|                                         | jnz             | DL1                                     | ;   | Delay over?                         |

|                                         | Incd.w          | SP                                      | ;   | Clean TOS                           |

|                                         | ret             |                                         | ;   | Return from subroutine              |

| ;********                               | * * * * * * * * | * * * * * * * * * * * * * * * * * * * * | * * | ********                            |

|                                         | COMMON          | INTVEC                                  | ;   | MSP430F14x Interrupt vectors        |

| ; * * * * * * * * * *                   | * * * * * * * * | * * * * * * * * * * * * * * * * * * * * | * * | ********                            |

|                                         | ORG             | TIMERB0_VECTOR                          |     |                                     |

| WDT_VEC                                 | DW              | TB7_ISR                                 | ;   | Timer B7 ISR                        |

|                                         |                 |                                         |     |                                     |

|                                         | ORG             | RESET_VECTOR                            |     |                                     |

| RESET_VEC                               | DW              | RESET                                   | ;   | POR, ext. Reset, Watchdog           |

|                                         |                 |                                         |     |                                     |

|                                         | END             |                                         |     |                                     |

### References

- 1. MSP430x13x, MSP430x14x Mixed Signal Flash Microcontroller datasheet (SLAS272B)

- 2. MSP430x1xx Family User's Guide (SLAU049)

- 3. TLV225x Rail-To-Rail Low-Voltage Low-Power Operational Amplifier (SLOS185B)

- 4. TLV5616 Low Power 12-Bit Digital-To-Analog Converters (SLAS152B)

- 5. TPA721 700-mW Mono Low-Voltage Audio Power Amplifier (SLOS231B)

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated