# MP650UCG **Datasheet**

Revision 0.95

2010-03-24

# **Revision History**

| Date          | Revision | Description                                                         |  |

|---------------|----------|---------------------------------------------------------------------|--|

| Nov. 10. 2009 | 0.9      | Initial Draft                                                       |  |

| Mar. 23, 2010 | 0.95     | Update General Description and Feature list                         |  |

|               |          | 2. Correct FGPIO index for FXD_RB pin of sec. 4.2                   |  |

|               |          | 3. Supplement ADC_IN3~0 pin descriptions of sec. 4.2                |  |

|               |          | 4. Supplement power-on strap descriptions of sec. 4.3.1             |  |

|               |          | 5. Supplemental descriptions for boot-up configurations of sec. 5.1 |  |

|               |          | 6. Revise IDU function description of sec. 5.5                      |  |

|               |          | 7. Revise Operating conditions and DC characteristics of Chapter 6  |  |

## **TABLE OF CONTENT**

| RE | VISIO | ON H | STORY                          | 2  |

|----|-------|------|--------------------------------|----|

| 1  |       |      | AL DESCRIPTION                 |    |

|    |       |      |                                |    |

| 2  | FEA   | ATUR | ES                             | 6  |

| 3  | BLC   | СК   | DIAGRAM                        | 10 |

| 4  | PIN   | ASS  | IGNMENT                        | 11 |

| 4  | 1.1   | Pin  | Diagram                        | 11 |

| 2  | 1.2   | PIN  | DESCRIPTION                    | 12 |

| 2  | 1.3   | PIN  | Configuration                  | 23 |

|    | 4.3.  | 1    | Power-on Strap                 | 23 |

|    | 4.3.  | 2    | SDRAM/DDR Interface            | 23 |

|    | 4.3.  | 3    | Memory Card Interface          | 24 |

|    | 4.3.  | 4    | Display Interface              | 25 |

|    | 4.3.  | 5    | Panel Power PWM Interface      | 26 |

|    | 4.3.  | 6    | Secondary UART Interface       | 26 |

|    | 4.3.  | 7    | USBOTG Interface               | 26 |

|    | 4.3.  | 8    | I2S Digital Audio Interface    | 26 |

|    | 4.3.  | 9    | GPIO Interface                 | 26 |

|    | 4.3.  | 10   | ADC Interface                  | 27 |

| 5  | FUN   | ICTI | ONAL DESCRIPTION               | 28 |

| į  | 5.1   | CPL  | J                              | 28 |

|    | 5.1.  |      | Memory Mapping                 |    |

|    | 5.1.  | 2    | Boot-up Configuration          |    |

| į  | 5.2   | DMA  | A CONTROLLER                   | 29 |

| Ę  | 5.3   | GEN  | ERIC MEMORY COPY DMA           | 30 |

| Ę  | 5.4   | IMAG | SE PROCESSING UNIT (IPU)       | 30 |

| į  | 5.5   | IMAG | SE DISPLAY UNIT (IDU)          | 30 |

| į  | 5.6   | JPE  | G CODEC                        | 31 |

| į  | 5.7   | Mul  | TI-FORMAT VIDEO DECODER        | 32 |

| į  | 5.8   | MEN  | ORY CARD CONTROLLER            | 34 |

| Ę  | 5.9   | SPI  | SERIAL FLASH CONTROLLER        | 34 |

| Ę  | 5.10  | USE  | OTG CONTROLLER 0 AND 1         | 34 |

| ţ  | 5.11  | Digi | TAL AUDIO INTERFACE UNIT (AIU) | 34 |

| Ę  | 5.12  | PER  | PHERAL CONTROLLER              | 34 |

|    | 5.12  | 2.1  | GPI0                           | 34 |

|    | 5.12  | 2.2  | I2C Master                     | 35 |

|   | 5.12.3          | I2C Slave                           | 35 |

|---|-----------------|-------------------------------------|----|

|   | 5.12.4          | UART Controller A and B             | 35 |

|   | 5.12.5          | IR Controller                       | 35 |

| 6 | ELECTI          | RICAL CHARACTERISTICS               | 36 |

| 6 | 5.1 <b>A</b> BS | SOLUTE MAXIMUM RATINGS              | 36 |

| 6 | .2 REG          | COMMENDED OPERATING CONDITIONS      | 36 |

| 6 | .3 DC           | CHARACTERISTICS                     | 37 |

| 6 | .4 CAF          | PACITANCE                           | 37 |

| 6 | .5 AC           | Characteristics                     | 37 |

|   | 6.5.1           | Reset Timing                        | 37 |

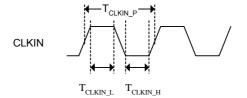

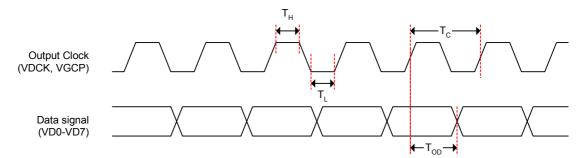

|   | 6.5.2           | Input Clock                         | 37 |

|   | 6.5.3           | SDRAM/DDR Interface Timing          | 38 |

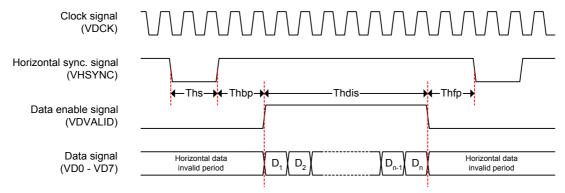

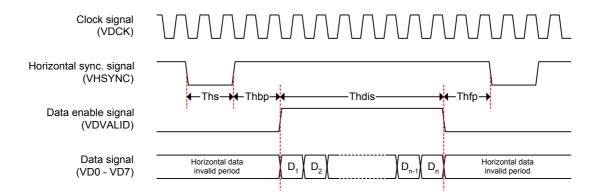

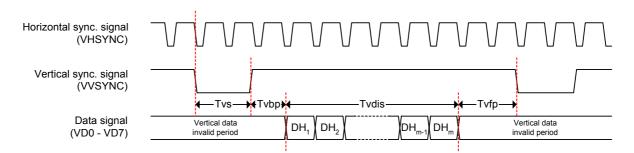

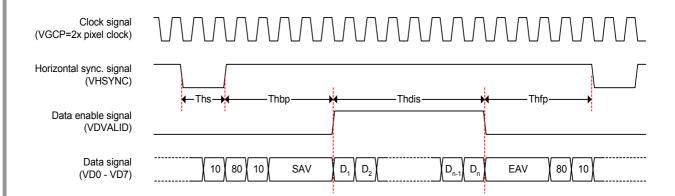

|   | 6.5.4           | RGB-888 Display Output, W/O TCON    | 39 |

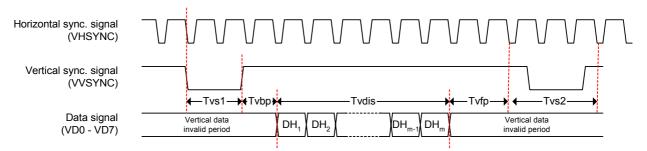

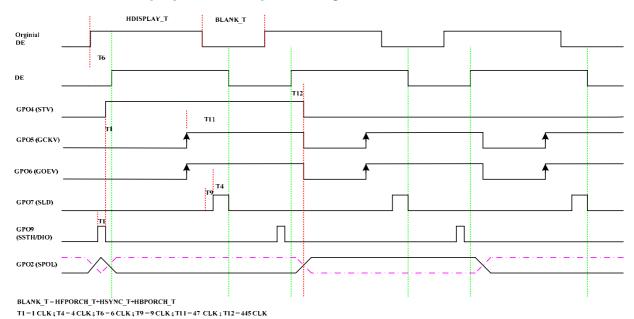

|   | 6.5.5           | Display TCON Output Timing          | 41 |

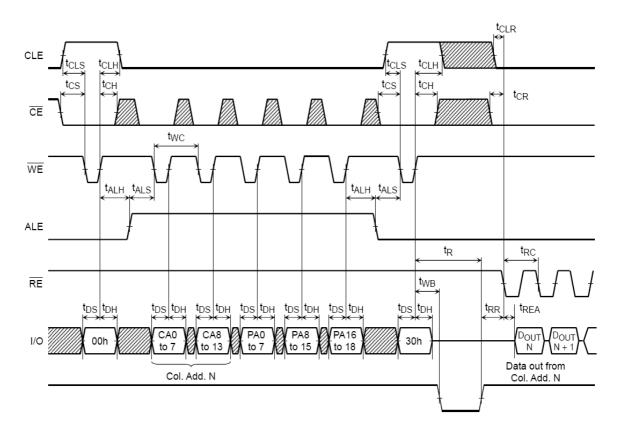

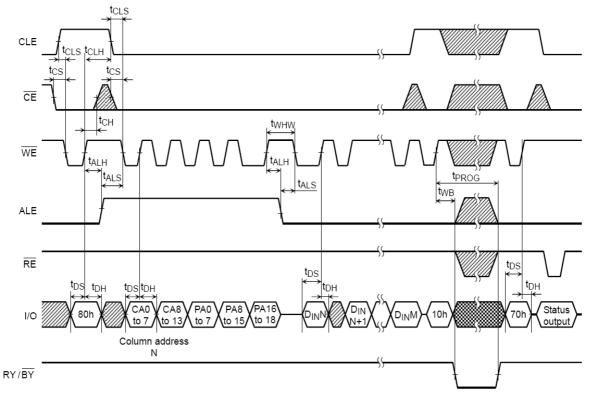

|   | 6.5.6           | NAND Flash Interface Timing         | 41 |

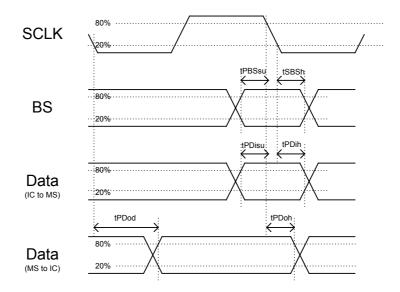

|   | 6.5.7           | SD Card Interface Timing            | 44 |

|   | 6.5.8           | Memory Stick Card Interface Timing  | 45 |

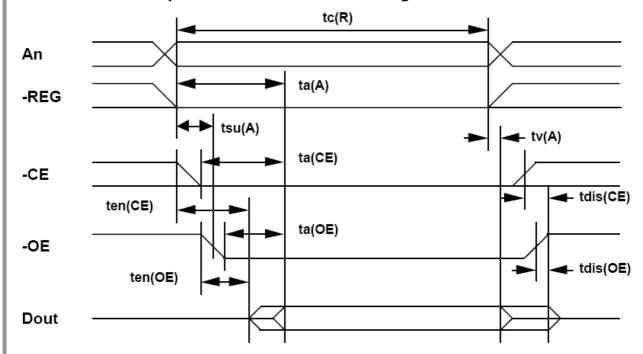

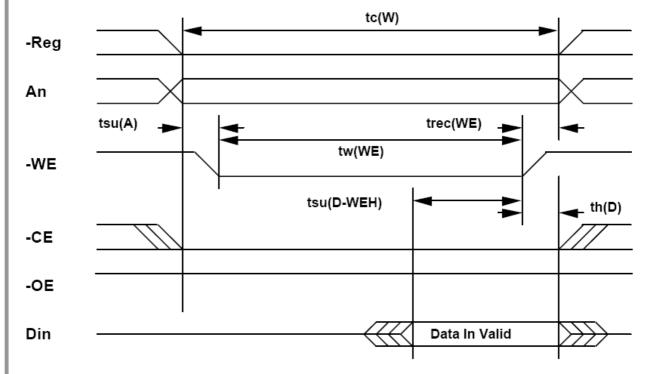

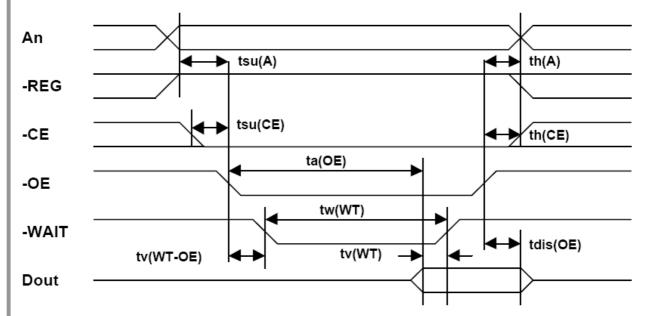

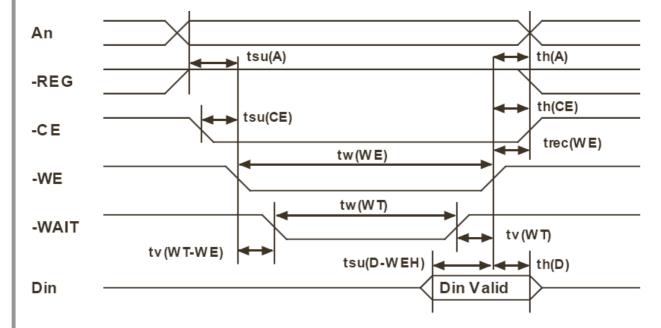

|   | 6.5.9           | Compact Flash Card Interface Timing | 48 |

| 6 | 6.6 ANA         | ALOG ELECTRICAL CHARACTERISITCS     | 50 |

|   | 6.6.1           | ADC                                 | 50 |

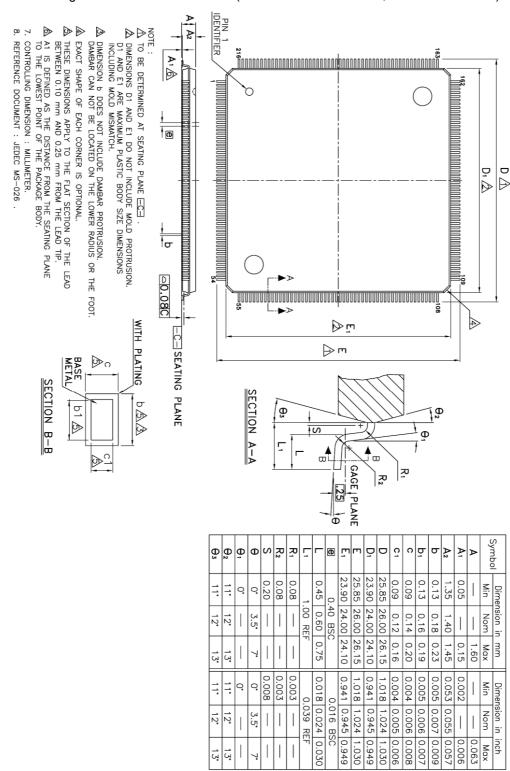

| 7 | PACKA           | GE DIMENSION                        | 51 |

## 1 General Description

The MP650UCG is a highly-integrated SOC (System-On-Chip) that's suitable for various multimedia applications like digital picture frame, media player and etc. It is capable of real-time decoding for various audio, video and image contents. A high-performance JPEG engine is included. A variety of JPEG data formats are supported. The embedded Video engine supports a variety of video compression standards, including MPEG-1/2/4 and H.264. It also supports Sorenson Spark FLV format for internet video. A flexible Image Processing Unit is built in to support high-quality image and color processing. It also includes a Special Effect controller to support various image effects in real time.

A 32-bit RISC CPU is built in to allow flexible system control. Proprietary instructions are included to improve performance and save power of S/W audio codec. A boot ROM which supports booting from NAND Flash or SD card is embedded. External NOR Flash for code storage is not needed. However, booting from Serial NOR Flash is also supported. The Serial NOR Flash can also be used as data storage in either boot-up scheme. An effective DMA and SDRAM/DDR controller is specially designed to optimize memory bandwidth efficiency.

A Stereo Audio DAC & Line Out Driver are integrated. I2S digital interface is also supported to utilize external audio codec to extend audio functions. The user can playback MP3, WMA as the background music when playing Slide-Show.

MP650UCG provides a versatile hardwired interface to support most popular memory card standards, including Compact Flash, SD/ mini SD/ Micro SD (It can support SD2.0 for SDHC specification), MMC/RS-MMC, xD, Memory Stick/Pro/MSPROHG. It offers the maximum flexibility to the customer. Secondary SD interface is included for peripheral, or SD card expansion.

The NAND Flash controller built into MP650UCG is equipped with flexible timing and parameter adjustment. The programmable configurations are designed to cover varieties of SLC/MLC/TLC NAND Flash in not only the existing technology, but also the future ones. As NAND Flash technology advances, it also demands higher bits ECC capability due to higher data error probability. To satisfy this requirement, MP650UCG has included a configurable ECC controller that supports up to 24-bit BCH ECC per 1KB.

Various display output formats, including CCIR-601/656/709, RGB-666/656, serial RGB, are supported by the Display Controller. It also includes a digital Timing Controller (TCON) with flexible timing configuration for glue-less panel connection.

2 sets of PWM are supported for external voltage boosters, which can be used as panel VGL/VGH and backlight drivers.

For data transfer to/from PC/Pict-Bridge enabled printer, it provides both USB and popular UART interfaces. It includes dual USBOTG high-speed controllers which are compliant with the USB 2.0 standard. It enables high-speed communications with a variety of hosts or devices, like PC, Camera, Printer and etc.

For flexible peripheral control and user interface, it provides several GPIOs. Most function pins can also be configured as GPIO. It also includes an IR (Infra-Red) controller supporting NEC Button and Remote Point Mouse protocols. I2C master and slave functions are supported to facilitate peripheral control and extend system functions. Several ADC are included to support various information inputs, like key control, battery detection, and etc.

With abundant features, superior performance and quality and highly integrated peripheral support, MP650UCG provides a best cost-effective solution for media player applications.

## 2 Features

#### Power

Dual Power. 1.2V for core, 3.3V/2.5V for I/O, 3V for RTC

### **■** Image Processing Unit

- > Hardware scaling engine to scale up and down images for resolution conversion

- Configurable Edge detection and sharpness enhancement

- RGB Color management engine with 24 independent color angles

- RGB Color management SW tool to allow independent skin tone / preference colors setting

- > YCbCr Color Control with 256 regions independent color hue adjustment

- Dual image windows overlay

- De-interlacing for interlaced video (Up to D1@60 field/sec)

- Hardware special photo effect controller.(High contrast, Color Mix, Black/White, Comic-style)

#### ■ JPEG Codec

- Support image resolution up to 64K x 64K for decoding, up to 8K x 8K for encoding

- ➤ High speed JPEG compression and decompression (>40M Pixel/sec in 100MHZ)

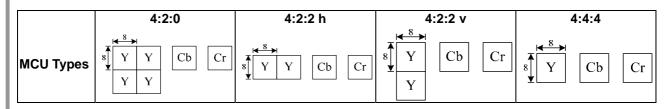

- Support JPEG decoding input formats: YCbCr 422h/422v/444/420, Y-only, 1/2/3/4-component Raw Data with 2-Huff, 2-Q tables at max

- Support JPEG encoding output formats: YCbCr 422h

- Support programmable image sub-sampling down to 1/8 ratio in H and V after JPEG decompression

- Support HW image rotation (90/-90/180 degree) / Zoom In / Panning.

- Picture Luma /Chroma statistics histogram for adaptive image processing

#### Audio/Video decoding HW accelerator

- Support MPEG Audio Layer 1, 2, MP3, WMA, OGG, AAC\_LC, AMR audio decoding.

- Full bit-rate support for MP3, WMA

- Hardware video decoding engine for H.264, MPEG-1,2,4,M-JPEG, H.263 & Flash Video(FLV-Sorenson Spark)

#### H.264 1280x720p@30 frame/sec

- ✓ Profile Support: Baseline, Main & High profiles

- ✓ Level Support : Level 1.0~3.1

#### MPEG-4 1280x720p@30 frame/sec

- ✓ Profile Support: Simple & Advanced Simple profiles

- ✓ Level Support : Level 0~5

- FLV(Sorenson Spark) 1280x720p@30 frame/sec

- MPEG-1 1280x720@30 frame/sec

- MPEG-2 1280x720@30 frame/sec

✓ Profile Support: Baseline, Main profile

✓ Level Support: Low & Main levels

- H.263 1280x720p@30 frame/sec

- ✓ Profile Support: Profile 0

- ✓ Level Support: Level 10~70

- Motion-JPEG 1280x720p@30 frame/sec

- \* DDR-I is necessary for 1280x720p video decoding

#### ■ Memory Interface

- Support DDR-I up to 64MB (16bit data bus), 166MHZ

- Support SDRAM up to 32MB (16bit data bus), 166MHZ

- SPI NOR flash support, 1-bit with max capacity 4MB

#### ■ Multiple Boot up methods

- Boot from SPI NOR flash

- Boot from embedded ROM

- Loader and code from NAND in user mode.

- Loader and code from SD card for production test mode

- Support In System (NAND) Programming (ISP)

## ■ Memory Card/NAND Flash Interface

- Support Security Disk (SD1.2/2.0), Multi-Media Card (MMC, MMC4.0/3.2), Memory Stick Pro & 8 bit mode MSPROHG, xD Picture Card(1.0/1.1)

- Support Compact Flash (2.0/3.0/4.0/4.1)

- Support SLC/MLC/TLC type NAND Flash memory with page size 512B, 1K/2K/4K and 8KB

- Programmable ECC with Hamming 1 bit and BCH 8/12/16-bit-ECC per 512-byte and 24-bit ECC per 1K-byte for 3X nm NAND Flash (3-bit per cell)

- Support auto page read and write, including FTL, ECC & data, for NAND Flash access to reduce SW overhead

- ➤ Support 3,4,5 and 6 NAND row address cycles, support 2-die NAND chip

- > Support multi-sector DMA and deep FIFOs for better through-put

- Support card-to-card and card-to/from-NAND copy.

- Support 2<sup>nd</sup> SD Card or SDIO (Independent DMA and controller)

#### Audio Interface

- Embedded Stereo Audio DAC with max 48KHz

- Embedded Stereo Line out driver

- ▶ I²S digital interface for external audio Codec

#### **■** USB Interface

- > Dual USB OTG 2.0 ports for versatile USB dongle applications

- Support Direct Print function (Pict-Bridge)

- Power saving control to comply with USB spec.

- Support uploading and downloading capability

- Support USB Mass Storage Class for both High Speed Device and High Speed Host functions

#### ■ Display Interface

- > Supported digital output format : CCIR-601/656/709, RGB-666/656, serial RGB

- Support digital input format: XRGB-888, RGB-888, YCbCr 444/422

- Output Resolution up to 1024x768 with SDRAM, and 1280x800 or 1366x768 with DDR

- > Independent RGB gamma adjustment (32-step Piecewise-linear)

- Programmable (Spatial or temporal) dithering for RGB666 panels

- Embedded Digital TCON for up to 800x600 resolution

- ➤ OSD engine supports 2-, 4- or 8-bit palette-indexed Bit-mapped On Screen Display (OSD).

- One programmable Color Space Converter

## ■ LDO (Charge Pump for Panel)

Two set of Max 1.5Mhz PWM with driver transistor protection support for VGH/VGL & backlight LED driver

#### ■ RTC

- > 3.0V single voltage supply with 64-bits storage registers built-in

- Calibration adjustment support

- Alarm function and output pin support

#### ■ Low speed ADC

- ➤ 4 ADC input ports support for key control, battery detection or other purposes.

- Maximum sample rate: 3.3Msps @20MHz clock

#### Power Management and EMI

- 4 phase-locked loop (PLL) on chip for versatile clocking applications

- Patented Spread Spectrum function inside the PLL to reduce EMI peaks

- Dedicated clock for USB

- Support deep power down mode

- Support Alarm trigger system wake up or GPIO wake-up

#### ■ CPU

- Embedded high performance 32-bit RISC processor with 8KB instruction cache and 2KB data cache.

- On chip 24KB SRAM and 512MB memory addressing capability

- Support up to 166MHz system & CPU clock

- > MAC Unit with MPX audio accelerator built into CPU core

#### ■ I2C/UART/IR/Timer/GPIO

- > Dual UART ports with one port supporting flow control, max baud rate is 8Mbps

- Support generic DMA for memory fill and copy actions ( linear or 2D mode ) and prioritized DMA channels support

- > I2C Master interface support

- ➤ I2C Slave interface support

- ➤ IR support with NEC and Remote Point Mouse Protocol

- ▶ 6 timers with 32 bits counters

- > Flexible GPIO control for variety of peripheral control

### ■ Package

> 216-pin LQFP (24mm x 24mm x 1.4mm)

### System Development Kit & Software Support

- Support real time OS: u-iTron 4.0

- Reference PCB Design Schematics and Layout Guides

- > System Application Notes

- > UI (User Interface) Builder

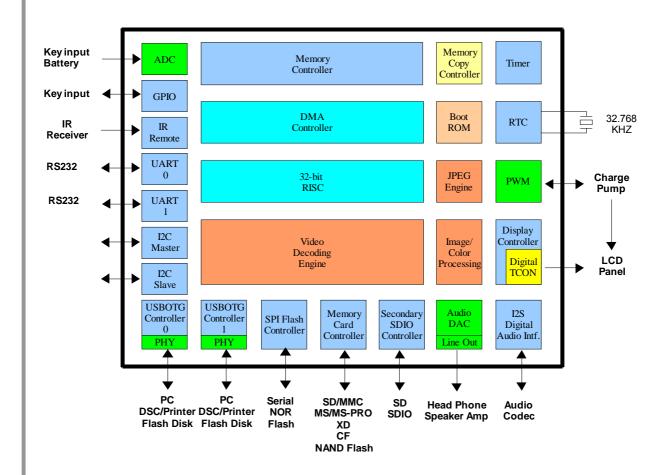

#### 3 **Block diagram**

Fig. 3-1 MP650UCG Block Diagram

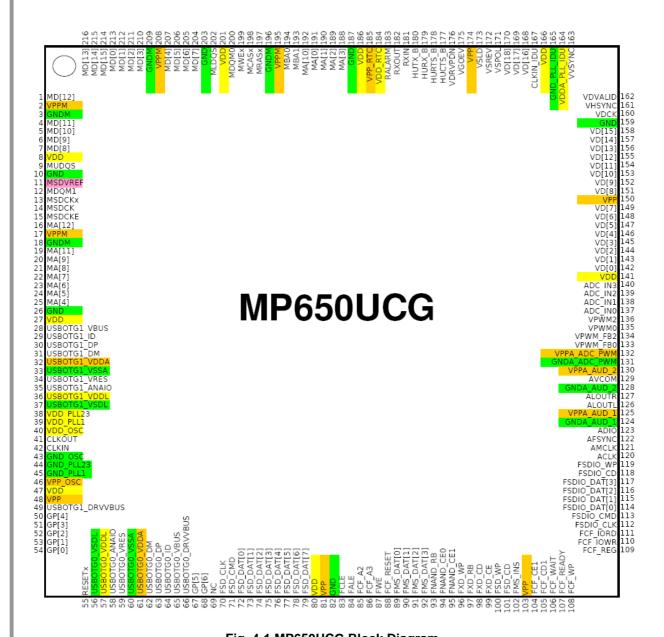

## 4 Pin Assignment

## 4.1 Pin Diagram

Fig. 4-1 MP650UCG Block Diagram

## 4.2 Pin Description

| Pin Name           | Pin Number          | I/O | Description                                                          |

|--------------------|---------------------|-----|----------------------------------------------------------------------|

| DRAM Interface     |                     |     |                                                                      |

| MD[15:0]           | 214, 215, 216,1,    | I/O | SDRAM/DDR Data                                                       |

|                    | 4, 5, 6, 7,         |     |                                                                      |

|                    | 204, 205, 206, 207, |     |                                                                      |

|                    | 210, 211, 212, 213  |     |                                                                      |

| MA[12:0]           | 16, 19, 192, 20, 21 | 0   | SDRAM/DDR Address                                                    |

|                    | 22, 23, 24, 25,     |     |                                                                      |

|                    | 188, 189, 190, 191  |     |                                                                      |

| MBA0               | 194                 | 0   | SDRAM/DDR Bank Address bit 0                                         |

| MBA1               | 193                 | 0   | SDRAM/DDR Bank Address bit 1                                         |

| MRASx              | 197                 | 0   | SDRAM/DDR RASx, Row Address Strobe                                   |

| MCASx              | 198                 | 0   | SDRAM/DDR CASx, Column Address Strobe                                |

| MWEx               | 199                 | 0   | SDRAM/DDR WEx                                                        |

| MDQM0              | 200                 | 0   | SDRAM/DDR low byte Data Mask, for MD[7:0]                            |

| MDQM1              | 12                  | 0   | SDRAM/DDR high byte Data Mask, for MD[15:8]                          |

| MSDCK              | 14                  | 0   | SDRAM/DDR Clock                                                      |

| MSDCKx             | 13                  | 0   | DDR Inverted Clock                                                   |

| MSDCKE             | 15                  | 0   | SDRAM/DDR Clock Enable                                               |

| MLDQS              | 202                 | 0   | DDR low-byte Data Strobe, for MD[7:0]                                |

| MUDQS              | 9                   | 0   | DDR high-byte Data Strobe, for MD[15:8]                              |

| MSDVREF            | 11                  | Р   | DDR Voltage Reference. Set to VPPM/2 for proper                      |

|                    |                     |     | operation                                                            |

| Memory Card and NA | ND Flash Interface  |     |                                                                      |

| FSD_CLK            | 70                  | I/O | It's the clock signal CLK for SD/MMC and MS/MS-PRO.                  |

|                    |                     |     | It can also be configured as general input/output, FGPIO[0].         |

|                    |                     |     | As SPI Serial Flash is selected, it's the serial clock output, SCLK. |

| FSD_CMD            | 71                  | I/O | It's a multi-function pin.                                           |

|                    |                     |     | It's the CMD signal for SD/MMC.                                      |

|                    |                     |     | It's the RE# output for NAND/xD.                                     |

|                    |                     |     | When Compact Flash is selected, it's the OE#.                        |

|                    |                     |     | It can also be configured as general input/output, FGPIO[1].         |

| FSD_DAT[7:0] | 79 ~ 72 | I/O | It's the data bus for NAND Flash, xD, 8-bit MMC and Compact Flash. For SD, and 4-bit MMC, only FSD_DAT[3:0] is effective.                    |

|--------------|---------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

|              |         |     | For MS-PRO HG, {FSD_DAT[7:4], MS_DAT[3:0]} forms the 8-bit data bus.                                                                         |

|              |         |     | When configured as GPIO, they are corresponding to FGPIO[9:2].                                                                               |

|              |         |     | As SPI Serial Flash is selected, the corresponding pins are remapped as below:                                                               |

|              |         |     | FSD_DAT[4] – Serial data input, SI from Serial Flash<br>FSD_DAT[6] – WP# output to Serial Flash<br>FSD_DAT[7] – HOLD# output to Serial Flash |

| FWE          | 87      | I/O | It's the WE# signal for NAND Flash, xD and Compact Flash.                                                                                    |

|              |         |     | It can also be configured as general input/output, FGPIO[10].                                                                                |

| FCLE         | 83      | I/O | It's the Command Latch Enable signal, CLE, for NAND Flash and xD.                                                                            |

|              |         |     | When Compact Flash is selected, it's the bit 0 of Address output, A0.                                                                        |

|              |         |     | When configured as general input/output, it's corresponding to FGPIO[11].                                                                    |

| FALE         | 84      | I/O | It's the Address Latch Enable signal, ALE, for NAND Flash and xD.                                                                            |

|              |         |     | For MS/MS-PRO, it's the BS signal.                                                                                                           |

|              |         |     | When Compact Flash is selected, it's the bit 1 of Address output,A1.                                                                         |

|              |         |     | When configured as general input/output, it's corresponding to FGPIO[12].                                                                    |

| FCF_A2       | 85      | I/O | It's the bit 2 of Address output, A2,for Compact Flash.                                                                                      |

|              |         |     | When configured as general input/output, it's corresponding to FGPIO[13].                                                                    |

| FCF_A3       | 86      | I/O | It's the bit 3 of Address output, A3,for Compact Flash.                                                                                      |

|              |         |     | When configured as general input/output, it's corresponding to FGPIO[14].                                                                    |

| FCF_RESET    | 88      | I/O | It's the RESET# output for Compact Flash.                                                                                                    |

|              |         |     | When configured as general input/output, it's corresponding to FGPIO[15].                                                                    |

| FMS_DAT[3:0] | 92 ~ 89 | I/O | It's the data bus [3:0] for MS and MS-PRO. For MS-PRO HG, it's the data bus [3:0]. The high nibble data bus [7:4] come from FSD_DAT[7:4].    |

|              |         |     | When configured as general input/output, it's corresponding to FGPIO[19:16].                                                                 |

| FCF_WAIT  | 106 | I/O | It's the WAIT# output for Compact Flash.                                                                                                   |

|-----------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------|

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[20].                                                                  |

| FNAND_RB  | 93  | I/O | It's the RDY/BSY# signal for NAND Flash. When pulled low, it indicates that the NAND Flash is busy and not be able to accept new commands. |

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[21].                                                                  |

| FNAND_CE0 | 94  | I/O | It's the Chip Enable output 0 for NAND Flash. It's active low.                                                                             |

|           |     |     | It's also the Chip Enable output when SPI Serial Flash is selected.                                                                        |

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[22].                                                                  |

| FNAND_CE1 | 95  | I/O | It's the 2 <sup>nd</sup> Chip Enable output for NAND Flash. It's active low.                                                               |

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[23]                                                                   |

| FXD_CE    | 99  | I/O | It's the Chip Enable output for xD. It's active low.                                                                                       |

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[24].                                                                  |

| FCF_CE1   | 104 | I/O | It's the R/W access Enable output for Compact Flash. It should be connected to CE0# of the Compact Flash.                                  |

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[25].                                                                  |

| FCF_CD1   | 105 | I/O | It's the Card Detection input for Compact Flash. It can be connected to either CD0# or CD1# of the Compact Flash. It's active low.         |

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[26].                                                                  |

| FXD_CD    | 98  | I/O | It's the Card Detection input for xD. It's active low.                                                                                     |

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[27].                                                                  |

| FSD_CD    | 101 | I/O | It's the Card Detection input for SD/MMC. It's active low.                                                                                 |

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[28].                                                                  |

| FMS_INS   | 102 | I/O | It's the Card Insertion input for MS/MS-PRO. It indicates that the MS/MS-PRO card is plugged in when asserted low.                         |

|           |     |     | When configured as general input/output, it's corresponding to FGPIO[29].                                                                  |

| FSD_WP         | 100       | I/O | It's the Write Protect input for SD/MMC. When pulled low, it indicates that the SD/MMC card is prohibited from write access. |

|----------------|-----------|-----|------------------------------------------------------------------------------------------------------------------------------|

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[30].                                                    |

| FXD_WP         | 96        | I/O | It's the Write Protect output for xD. Pull it to low to prohibit xD card from write access.                                  |

|                |           |     | As SPI Serial Flash is selected, it's the serial data output to the Flash.                                                   |

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[31].                                                    |

| FCF_WP         | 108       | I/O | It's the Write Protect input for the Compact Flash interface.                                                                |

| _              |           |     | When configured as general input/output, it's corresponding to FGPIO[32].                                                    |

| FCF_REG        | 109       | I/O | It's the REG# output for Compact Flash.                                                                                      |

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[33].                                                    |

| FCF_IOWR       | 110       | I/O | It's the IOWR# output for the Compact Flash interface. It's not effective if memory mode is selected for Compact Flash.      |

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[34].                                                    |

| FCF_IORD       | 111       | I/O | It's the IORD# output for the Compact Flash interface. It's not effective if memory mode is selected for Compact Flash.      |

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[35].                                                    |

| FSDIO_CLK      | 112       | I/O | It's the clock output for the 2 <sup>nd</sup> SD interface.                                                                  |

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[36].                                                    |

| FSDIO_CMD      | 113       | I/O | It's the CMD signal for the 2 <sup>nd</sup> SD interface.                                                                    |

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[37].                                                    |

| FSDIO_DAT[3:0] | 117 ~ 114 | I/O | It's the data bus for the 2 <sup>nd</sup> SD interface.                                                                      |

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[41:38].                                                 |

| FCF_READY      | 107       | I/O | It's the READY input for Compact Flash.                                                                                      |

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[42].                                                    |

| FSDIO_CD       | 118       | I/O | It's the Card Detection input for the 2 <sup>nd</sup> SD interface.                                                          |

|                |           |     | When configured as general input/output, it's corresponding to FGPIO[43].                                                    |

| FSDIO_WP          | 119       | I/O | It's the Write Protect input for the 2 <sup>nd</sup> SD interface.                                                              |

|-------------------|-----------|-----|---------------------------------------------------------------------------------------------------------------------------------|

|                   |           |     | When configured as general input/output, it's corresponding to FGPIO[44].                                                       |

| FXD_RB            | 97        | I/O | It's the RDY/BSY# signal for xD. When pulled low, it indicates that the xD card is busy and not be able to accept new commands. |

|                   |           |     | When configured as general input/output, it's corresponding to FGPIO[45].                                                       |

| Display Interface |           |     |                                                                                                                                 |

| VD[7:0]           | 149 ~ 142 | I/O | For CCIR-656, it's the 8-bit pixel output.                                                                                      |

|                   |           |     | For CCIR-601, it's the 8-bit luma (Y) output.                                                                                   |

|                   |           |     | If RGB-888 is selected, it's the R[7:0] output.                                                                                 |

|                   |           |     | If built-in TCON is selected, VD[7:6] is the G[1:0], and VD[5:0] the R[5:0] output of RGB-666.                                  |

|                   |           |     | If Serial RGB is selected, it's the 8-bit pixel output.                                                                         |

|                   |           |     | When configured as general input/output, it's corresponding to VGPIO[7:0].                                                      |

| VD[15:8]          | 158 ~ 151 | I/O | For CCIR-601, it's the 8-bit Chroma (C) output.                                                                                 |

|                   |           |     | If RGB-888 is selected, it's the G[7:0] output.                                                                                 |

|                   |           |     | If built-in TCON is selected, VD[11:8] is the G[5:2], and VD[15:12] the B[3:0] output of RGB-666.                               |

|                   |           |     | When configured as general input/output, it's corresponding to VGPIO[15:8].                                                     |

| VD[16]            | 168       | I/O | If RGB-888 is selected, it's the B[0] output.                                                                                   |

|                   |           |     | If built-in TCON is selected, it's the B[4] output of RGB-666.                                                                  |

|                   |           |     | When configured as general input/output, it's corresponding to VGPIO[16].                                                       |

| VD[17]            | 169       | I/O | If RGB-888 is selected, it's the B[1] output.                                                                                   |

|                   |           |     | If built-in TCON is selected, it's the B[5] output of RGB-666.                                                                  |

|                   |           |     | When configured as general input/output, it's corresponding to VGPIO[17].                                                       |

| VD[18]            | 170       | I/O | If RGB-888 is selected, it's the B[2] output.                                                                                   |

|                   |           |     | If built-in TCON is selected, it can be configured as the Gate Driver Polarity Select, GPOL.                                    |

|                   |           |     | When configured as general input/output, it's corresponding to VGPIO[18].                                                       |

| VDCK              | 160       | I/O | It's the pixel clock output for all types of panels.                                                                            |

|                   |           |     | When configured as general input/output, it's corresponding to VGPIO[19].                                                       |

| VHSYNC  | 161 | I/O | It's the HSYNC output for CCIR-601, RGB-888 and Serial                                                      |

|---------|-----|-----|-------------------------------------------------------------------------------------------------------------|

|         |     |     | RGB.                                                                                                        |

|         |     |     | If built-in TCON is selected, it can be configured as the Horizontal Start Pulse, STH.                      |

|         |     |     | When configured as general input/output, it's corresponding to VGPIO[20].                                   |

| VDVALID | 162 | I/O | It's the Data Valid output, DVALID, for CCIR-601, RGB-888 and Serial RGB.                                   |

|         |     |     | If built-in TCON is selected, it can be configured as the Gate Driver Start Pulse, STV.                     |

|         |     |     | When configured as general input/output, it's corresponding to VGPIO[21].                                   |

| VVSYNC  | 163 | I/O | It's the VSYNC output for CCIR-601, RGB-888 and Serial RGB.                                                 |

|         |     |     | If built-in TCON is selected, it can be configured as the Gate Driver Shift Clock, CKV.                     |

|         |     |     | When configured as general input/output, it's corresponding to VGPIO[22].                                   |

| VSPOL   | 171 | I/O | If RGB-888 is selected, it's the B[3] output.                                                               |

|         |     |     | If built-in TCON is selected, it can be configured as the Source Driver Polarity Select, SPOL .             |

|         |     |     | When configured as general input/output, it's corresponding to VGPIO[23].                                   |

| VSREV   | 172 | I/O | If RGB-888 is selected, it's the B[4] output.                                                               |

|         |     |     | If built-in TCON is selected, it can be configured as the Source Driver Data Reverse Control, SREV.         |

|         |     |     | When configured as general input/output, it's corresponding to VGPIO[24].                                   |

| VSLD    | 173 | I/O | If RGB-888 is selected, it's the B[5] output.                                                               |

|         |     |     | If built-in TCON is selected, it can be configured as the Source Driver Latch Pulse and Output Enable, SLD. |

|         |     |     | When configured as general input/output, it's corresponding to VGPIO[25].                                   |

| VGOEV   | 175 | I/O | If RGB-888 is selected, it's the B[6] output.                                                               |

|         |     |     | If built-in TCON is selected, it can be configured as the Gate Driver Output Enable, GOEV.                  |

|         |     |     | When configured as general input/output, it's corresponding to VGPIO[26].                                   |

| VDRVPDN | 176 | I/O | If RGB-888 is selected, it's the B[7] output.                                                               |

|         |     |     | If built-in TCON is selected, it can be configured to output with required timing.                          |

|         |     |     | When configured as general input/output, it's corresponding to VGPIO[27].                                   |

| CKIN_IDU              | 167 | I/O   | It can be used as the clock input to PLL_IDU.                                                                                                                                                               |

|-----------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |     |       | When configured as general input/output, it's corresponding to VGPIO[28].                                                                                                                                   |

| Panel Power Interface |     |       |                                                                                                                                                                                                             |

| VPWM0                 | 135 | Ю     | By default, it's the primary PWM output for external panel power charge pump, like VGL/VGH.                                                                                                                 |

|                       |     |       | When configured as Alternative function 1, it's a general input/output, PGPIO[0].                                                                                                                           |

|                       |     |       | When configured as Alternative function 2, it's the I2C Master clock output.                                                                                                                                |

| VPWM_FB0              | 133 | AIO   | By default, it's the voltage divider analog input to the primary PWM generator. PWM output will be enabled only if the input voltage level is greater than internal bias, which is typically set to 1.2V.   |

|                       |     |       | It can also be configured to function as digital pin. When configured as Alternative function 1, it's a general input/output, PGPIO[1].                                                                     |

|                       |     |       | When configured as Alternative function 2, it's the I2C Master data input/output.                                                                                                                           |

| VPWM2                 | 136 | Ю     | By default, it's the secondary PWM output for external panel power charge pump, like LED Backlight.                                                                                                         |

|                       |     |       | When configured as Alternative function 1, it's a general input/output, PGPIO[2].                                                                                                                           |

|                       |     |       | When configured as Alternative function 2, it's the I2C Slave clock output.                                                                                                                                 |

| VPWM_FB2              | 134 | AIO   | By default, it's the voltage divider analog input to the secondary PWM generator. PWM output will be enabled only if the input voltage level is greater than internal bias, which is typically set to 1.2V. |

|                       |     |       | It can also be configured to function as digital pin. When configured as Alternative function 1, it's a general input/output, PGPIO[3].                                                                     |

|                       |     |       | When configured as Alternative function 2, it's the I2C Slave data input/output.                                                                                                                            |

| USB Interface         |     |       |                                                                                                                                                                                                             |

| USBOTG0_VRES          | 59  | AIO   | External resistor connection for current reference of USBOTG0 PHY.                                                                                                                                          |

| USBOTG0_VBUS          | 65  | AIO5V | 5V VBUS for USBOTG0.                                                                                                                                                                                        |

| USBOTG0_DM            | 62  | AIO   | Negative output channel of USBOTG0 that is connected to the serial USB cable.                                                                                                                               |

| USBOTG0_DP            | 63  | AIO   | Positive output channel of USBOTG0 that is connected to the serial USB cable.                                                                                                                               |

| USBOTG0_ID            | 64  | AIO   | USB ID pin of mini-AB receptacle for USBOTG0.                                                                                                                                                               |

| USBOTG0_ANAIO         | 58  | AIO   | USBOTG0 PHY debug pin.                                                                                                                                                                                      |

| USBOTG0_DRVVBUS | 66       | I/O   | By default, it's the USBOTG0 5V power driving enable.                                                      |

|-----------------|----------|-------|------------------------------------------------------------------------------------------------------------|

|                 |          |       | It can also be used as GPIO, OGPIO[0], by configuring to Alternative function 1.                           |

| USBOTG1_VRES    | 34       | AIO   | External resistor connection for current reference of USBOTG1 PHY.                                         |

| USBOTG1_VBUS    | 28       | AIO5V | 5V VBUS for USBOTG1                                                                                        |

| USBOTG1_DM      | 31       | AIO   | Negative output channel of USBOTG1 that is connected to the serial USB cable.                              |

| USBOTG1_DP      | 30       | AIO   | Positive output channel of USBOTG1 that is connected to the serial USB cable.                              |

| USBOTG1_ID      | 29       | AIO   | USB ID pin of mini-AB receptacle for USBOTG1.                                                              |

| USBOTG1_ANAIO   | 35       | AIO   | USBOTG1 PHY debug pin.                                                                                     |

| USBOTG1_DRVVBUS | 49       | I/O   | By default, it's the USBOTG1 5V power driving enable.                                                      |

|                 |          |       | It can also be used as GPIO, OGPIO[1], by configuring to Alternative function 1.                           |

| GPIO Interface  |          | 1     |                                                                                                            |

| GP[0]           | 54       | I/O   | By default, it's the general input/output, GP[0].                                                          |

|                 |          |       | It can also be used as the RX input of the primary UART.                                                   |

|                 |          |       | When Alternative function 3 is selected, it's the I2C Master clock output.                                 |

| GP[1]           | 53       | I/O   | By default, it's the general input/output, GP[1].                                                          |

|                 |          |       | When Alternative function 1 is selected, it's the TX output of the primary UART.                           |

|                 |          |       | When Alternative function 3 is selected, it's the I2C Master data input/output.                            |

| GP[2]           | 52       | I/O   | By default, it's the general input/output, GP[2].                                                          |

| J. [-]          | <u> </u> |       | It can also be configured as the CTS input of the primary UART.                                            |

|                 |          |       | When Alternative function 3 is selected, it's the Timer 2 output which can be used to generate PWM signal. |

|                 |          |       | It can also be used as the IR input from external IR receiver.                                             |

| GP[3]           | 51       | I/O   | By default, it's the general input/output, GP[3].                                                          |

| 1-1             |          |       | When Alternative function 1 is selected, it's the RTS output of the primary UART.                          |

|                 |          |       | When Alternative function 3 is selected, it's the Timer 3 output which can be used to generate PWM signal. |

| GP[4]           | 50       | I/O   | By default, it's the general input/output, GP[4].                                                          |

| 1.1             |          | 5     | When Alternative function 2 is selected, it's a buffer output of the 12MHZ clock input from the CLKIN pin. |

| GP[5]                      | 67  | I/O | By default, it's the general input/output, GP[5].                                                           |

|----------------------------|-----|-----|-------------------------------------------------------------------------------------------------------------|

|                            |     |     | When Alternative function 2 is selected, it's Timer 4 output which can be used to generate PWM signal.      |

| GP[6]                      | 68  | I/O | By default, it's the general input/output, GP[6].                                                           |

|                            |     |     | When Alternative function 2 is selected, it's Timer 5 output which can be used to generate PWM signal.      |

| Secondary UART Interfa     | псе | 1   |                                                                                                             |

| HURX_B                     | 179 | I/O | By default, it's a general input/output, UGPIO[4].                                                          |

|                            |     |     | It can also be used as the RX input of the secondary UART.                                                  |

| HUTX_B                     | 180 | I/O | By default, it's a general input/output, UGPIO[5].                                                          |

|                            |     |     | When Alternative function 1 is selected, it's the TX output of the secondary UART.                          |

| HUCTS_B                    | 177 | I/O | By default, it's a general input/output, UGPIO[6].                                                          |

|                            |     |     | It can also be used as the CTS input of the secondary UART.                                                 |

| HURTS_B                    | 178 | I/O | By default, it's a general input/output, UGPIO[7].                                                          |

| _                          |     |     | When Alternative function 1 is selected, it's the RTS output of the secondary UART.                         |

| I2S Digital Audio Interfac | ce  | l   |                                                                                                             |

| ACLK                       | 120 | I/O | By default, it's a general input/output, AGPIO[0].                                                          |

|                            |     |     | When configured as Alternative function 1, it's the bit clock output to external audio codec.               |

| AMCLK                      | 121 | I/O | By default, it's a general input/output, AGPIO[1].                                                          |

|                            |     |     | When configured as Alternative function 1, it's the master clock input/output from/to external audio codec. |

| AFSYNC                     | 122 | I/O | By default, it's a general input/output, AGPIO[2].                                                          |

|                            |     |     | When configured as Alternative function 1, it's the Frame Sync output to external audio codec.              |

| ADIO                       | 123 | I/O | By default, it's a general input/output, AGPIO[3].                                                          |

|                            |     |     | When configured as Alternative function 1, it's the data input/output from/to external audio codec.         |

| Analog Audio Interface     |     |     |                                                                                                             |

| ALOUTL                     | 126 | AO  | Left channel of Audio Line Output                                                                           |

| ALOUTR                     | 127 | AO  | Right channel of Audio Line Output                                                                          |

| AVCOM                      | 129 | AIO | Analog reference voltage for the audio DAC. It's typically set to half of the audio power, VPPA AUD.        |

| ADC_IN0          | 137   | AIO  | By default, it's the channel 0 ADC input.                                                                                                 |

|------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| , 15 0_1110      | 107   | 7110 | It can also be configured to function as digital pin. When configured as default digital function, it's a general input/output, KGPIO[0]. |

|                  |       |      | If configured as Alternative function 1, it's the master clock input/output, AMCLK, from/to the external audio codec.                     |

|                  |       |      | When configured as Alternative function 2, it's the I2C Slave data input/output.                                                          |

| ADC_IN1          | 138   | AIO  | By default, it's the channel 1 ADC input.                                                                                                 |

|                  |       |      | It can also be configured to function as digital pin. When configured as default digital function, it's a general input/output, KGPIO[1]. |

|                  |       |      | If configured as Alternative function 1, it's the frame synchronization output, AFSYNC, to the external audio codec.                      |

|                  |       |      | When configured as Alternative function 2, it's the RX input of the primary UART.                                                         |

| ADC IN2          | 139   | AIO  | By default, it's the channel 2 ADC input.                                                                                                 |

| _                |       |      | It can also be configured to function as digital pin. When configured as default digital function, it's a general input/output, KGPIO[2]. |

|                  |       |      | If configured as Alternative function 1, it's the audio data input/output, ADIO, from/to the external audio codec.                        |

|                  |       |      | When configured as Alternative function 2, it's the TX output of the primary UART.                                                        |

| ADC_IN3          | 140   | AIO  | By default, it's the channel 3 ADC input.                                                                                                 |

|                  |       |      | It can also be configured to function as digital pin. When configured as default digital function, it's a general input/output, KGPIO[3]. |

|                  |       |      | If configured as Alternative function 1, it's the RTC 1HZ clock output.                                                                   |

|                  |       |      | When configured as Alternative function 2, it's the 3D_CLI output to 3D panels.                                                           |

| RTC Interface    | •<br> |      |                                                                                                                                           |

| RXIN             | 181   | I    | It's the 32.768KHZ RTC Oscillator input                                                                                                   |

| RXOUT            | 182   | 0    | It's the 32.768KHZ RTC Oscillator output                                                                                                  |

| RALARM           | 183   | I/O  | By default, it's the RTC Alarm output. It will be asserted when the RTC counter equals the RTC ALARM setting.                             |

|                  |       |      | It can also be configured as a general input/output.                                                                                      |

| System Interface |       |      |                                                                                                                                           |

| RESETx           | 55    | I    | It's the hardware reset input, active low.                                                                                                |

| CLKIN            | 42    | ı    | It's the 12MHZ main oscillator input.                                                                                                     |

| CLKOUT           | 41    | 0    | It's the 12MHZ main oscillator output.                                                                                                    |

| Power/Ground     |       |      |                                                                                                                                           |

| VPPM         | 2, 17, 195, 208                      | Р | It's the I/O power for SDRAM/DDR interface. It's separated from the other I/O powers. It's typically 3.3V for SDRAM, and 2.5V for DDR.       |

|--------------|--------------------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------------|

| GNDM         | 3, 18, 196, 209                      | Р | It's the I/O ground for SDRAM/DDR interface. It's separated from the other I/O ground.                                                       |

| USBOTG0_VDDA | 61                                   | Р | It's the 3.3V analog power for USBOTG0 PHY.                                                                                                  |

| USBOTG0_VSSA | 60                                   | Р | It's the analog ground corresponding to 3.3V analog power for USBOTG0 PHY.                                                                   |

| USBOTG0_VDDL | 57                                   | Р | It's the 1.2V analog power for USBOTG0 PHY.                                                                                                  |

| USBOTG0_VSDL | 56                                   | Р | It's the analog ground corresponding to 1.2V analog power for USBOTG0 PHY.                                                                   |

| USBOTG1_VDDA | 32                                   | Р | It's the 3.3V analog power for USBOTG1 PHY.                                                                                                  |

| USBOTG1_VSSA | 33                                   | Р | It's the analog ground corresponding to 3.3V analog power for USBOTG1 PHY.                                                                   |

| USBOTG1_VDDL | 36                                   | Р | It's the 1.2V analog power for USBOTG1 PHY.                                                                                                  |

| USBOTG1_VSDL | 37                                   | Р | It's the analog ground corresponding to 1.2V analog power for USBOTG1 PHY.                                                                   |

| VPP_OSC      | 46                                   | Р | It's the 3.3V I/O power for the 12MHZ main oscillator I/O.                                                                                   |

| VDD_OSC      | 40                                   | Р | It's the 1.2V core power for the 12MHZ main oscillator I/O.                                                                                  |

| VDD_PLL23    | 38                                   | Р | It's the 1.2V power for PLL_2 and PLL_3.                                                                                                     |

| GND_PLL23    | 44                                   | Р | It's the analog ground for PLL_2 and PLL_3.                                                                                                  |

| VDD_PLL1     | 39                                   | Р | It's the 1.2V power for PLL_1.                                                                                                               |

| GND_PLL1     | 45                                   | Р | It's the analog ground for PLL_1.                                                                                                            |

| VDDA_PLL_IDU | 164                                  | Р | It's the 1.2V power for PLL_IDU.                                                                                                             |

| GND_PLL_IDU  | 165                                  | Р | It's the analog ground for PLL_IDU.                                                                                                          |

| VPPA_AUD_1   | 125                                  | Р | It's the 3.3V analog power for the audio DAC.                                                                                                |

| VPPA_AUD_2   | 130                                  | Р | It's the 3.3V analog power for the audio DAC.                                                                                                |

| GNDA_AUD_1   | 124                                  | Р | It's the analog ground corresponding to VPPA_AUD_1 for the audio DAC.                                                                        |

| GNDA_AUD_2   | 128                                  | Р | It's the analog ground corresponding to VPPA_AUD_2 for the audio DAC.                                                                        |

| VPPA_ADC_PWM | 132                                  | Р | It's the 3.3V analog power for the ADCs and PWMs.                                                                                            |

| GNDA_ADC_PWM | 131                                  | Р | It's the analog ground for the ADCs and PWMs.                                                                                                |

| VDD_RTC      | 184                                  | Р | It's the 1.2V power input for the RTC core. If internal RTC 3V-to-1.2V DC converter is enabled, it is used as external capacitor connection. |

| VPP_RTC      | 185                                  | Р | It's the dedicated I/O power for RTC.                                                                                                        |

| VPP          | 48, 81, 103, 150,<br>174             | Р | 3.3V digital I/O power                                                                                                                       |

| VDD          | 8, 27, 47, 80, 141,<br>166, 186, 201 | Р | 1.2V digital core power                                                                                                                      |

| GND          | 10, 26, 82, 159, 187,<br>203         | Р | Digital ground                                                                                                                               |

## 4.3 Pin Configuration

## 4.3.1 Power-on Strap

MP650UCG defines several power-on strap configurations through pins VD[7:0] and VHSYNC. The states of the power-on strap pins are latched by the rising edge of the internal delayed RESETx signal. They are then utilized by the chip itself or boot code to determine the key configurations for proper operation. Each power-on strap pin should be pulled up to VPP or down to GND through a resistor typically in 10K ohm.

| Power-on<br>Strap Pin | Function        | Description                                                                                      |

|-----------------------|-----------------|--------------------------------------------------------------------------------------------------|

| VD[0]                 | Reserved        | Leave it floating or pull it down for proper operation                                           |

| VD[1]                 | DRAM_Type       | 0 – SDRAM<br>1 – DDR SDRAM                                                                       |

| VD[3:2]               | DRAM_SIZE       | 2'b00 – 4Mb*16<br>2'b01 – 8Mb*16<br>2'b10 – 16Mb*16<br>2'b11 – 32Mb*16 → applicable only for DDR |

| VD[4]                 | INT_BOOT_SEL    | Load software code from:<br>0 – SD Card<br>1 – NAND Flash                                        |

| VD[7:5]               | NF_ROW_CYC[2:0] | Number of NAND Flash Row Address Cycle = NF_ROW_CYC[2:0] + 1                                     |

| VHSYNC                | BTDEVICE        | Boot up from:<br>0 – Internal ROM<br>1 – SPI Serial Flash                                        |

Note: 0 state means pull low to GND; 1 means pull high to VPP.

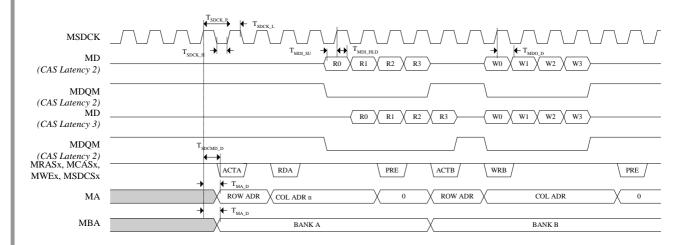

## 4.3.2 SDRAM/DDR Interface

| Pin Name | SDRAM    | DDR      |

|----------|----------|----------|

| MD[15:0] | DQ[15:0] | DQ[15:0] |

| MA[12:0] | A[12:0]  | A[12:0]  |

| MBA0     | BA0      | BA0      |

| MBA1     | BA1      | BA1      |

| MRASx    | RAS#     | RAS#     |

| MCASx    | CAS#     | CAS#     |

| MWEx     | WE#      | WE#      |

| MDQM0    | LDQM     | LDQM     |

| MDQM1    | UDQM     | UDQM     |

| MSDCK    | CLK      | CLK      |

| MSDCKx   | -        | CLK#     |

| MSDCKE   | CKE      | CKE      |

| MLDQS    | -        | LDQS     |

| MUDQS    | -        | UDQS     |

The CS# input of the SDRAM and DDR should be pulled low to GND for proper operation.

## 4.3.3 Memory Card Interface

|              |              |                        |          | Alt. Fı      | ınc. 1       |          |          | SPI<br>Flash                | Pull H/L<br>Config. |

|--------------|--------------|------------------------|----------|--------------|--------------|----------|----------|-----------------------------|---------------------|

| Pin Name     | Default      | CF<br>(Memory<br>mode) | SD_0     | ММС          | NAND         | XD       | MS       |                             |                     |

| FSD_CLK      | FGPIO[0]     |                        | CLK      | CLK          |              |          | CLK      | SCLK                        | Н                   |

| FSD_CMD      | FGPIO[1]     | OE#                    | CMD      | CMD          | RE#          | RE#      |          |                             | Н                   |

| FSD_DAT[3:0] | FGPIO[5:2]   | DAT[3:0]               | DAT[3:0] | DAT[3:<br>0] | DAT[3:<br>0] | DAT[3:0] |          |                             | Н                   |

| FSD_DAT[7:4] | FGPIO[9:6]   | DAT[7:4]               |          | DAT[7:<br>4] | DAT[7:<br>4] | DAT[7:4] | DAT[7:4] | {HOLD#<br>, WP#, -,<br>SI}} | Н                   |

| FWE          | FGPIO[10]    | WE#                    |          |              | WE#          | WE#      |          |                             | Н                   |

| FCLE         | FGPIO[11]    | A0                     |          |              | CLE          | CLE      |          |                             | L                   |

| FALE         | FGPIO[12]    | A1                     |          |              | ALE          | ALE      | BS       |                             | L                   |

| FCF_A2       | FGPIO[13]    | A2                     |          |              |              |          |          |                             | L                   |

| FCF_A3       | FGPIO[14]    | A3                     |          |              |              |          |          |                             | L                   |

| FCF_RESET    | FGPIO[15]    | RESET                  |          |              |              |          |          |                             | L                   |

| FMS_DAT[3:0] | FGPIO[19:16] |                        |          |              |              |          | DAT[3:0] |                             | L                   |

| FCF_WAIT     | FGPIO[20]    | WAIT#                  |          |              |              |          |          |                             | Н                   |

| FNAND_RB     | FGPIO[21]    |                        |          |              | R/B#         |          |          |                             | Н                   |

| FNAND_CE0    | FGPIO[22]    |                        |          |              | CE0#         |          |          | SCS#                        | Н                   |

| FNAND_CE1    | FGPIO[23]    |                        |          |              | CE1#         |          |          |                             | Н                   |

| FXD_CE       | FGPIO[24]    |                        |          |              |              | CE#      |          |                             | Н                   |

| FCF_CE1      | FGPIO[25]    | CE1#                   |          |              |              |          |          |                             | Н                   |

| FCF_CD1      | FGPIO[26]    | CD1#                   |          |              |              |          |          |                             | Н                   |

| FXD_CD       | FGPIO[27]    |                        |          |              |              | CD#      |          |                             | Н                   |

| FSD_CD       | FGPIO[28]    |                        | CD#      | CD#          |              |          |          |                             | Н                   |

| FMS_INS      | FGPIO[29]    |                        |          |              |              |          | INS#     |                             | Н                   |

| FSD_WP       | FGPIO[30]    |                        | WP_IN#   | WP_IN#       |              |          |          |                             | Н                   |

| FXD_WP       | FGPIO[31]    |                        |          |              |              | WP_OUT#  |          | SO                          | L                   |

| FCF_WP       | FGPIO[32]    | WP_IN                  |          |              |              |          |          |                             | Н                   |

| FCF_REG      | FGPIO[33]    | REG#                   |          |              |              |          |          |                             | Н                   |

| FCF_IOWR     | FGPIO[34]    |                        |          |              |              |          |          |                             | Н                   |

| FCF_IORD     | FGPIO[35]    |                        |          |              |              |          |          |                             | Н                   |

| FCF_READY    | FGPIO[42]    | READY                  |          |              |              |          |          |                             | Н                   |

| FXD_RB       | FGPIO[45]    |                        |          |              |              | R/B#     |          |                             | Н                   |

The built-in pull high/low for each pin is configurable and can be turned on or off by software.

The pin configuration of the secondary SD interface is summarized as below.

| Pin Name       | Default      | Alt. Func. 1 | Pull H/L<br>Config. |

|----------------|--------------|--------------|---------------------|

| FSDIO_CLK      | FGPIO[36]    | CLK          | Н                   |

| FSDIO_CMD      | FGPIO[37]    | CMD          | Н                   |

| FSDIO_DAT[3:0] | FGPIO[41:38] | DAT[3:0]     | Н                   |

| FSDIO_CD       | FGPIO[43]    | CD#          | Н                   |

| FSDIO_WP       | FGPIO[44]    | WP           | Н                   |

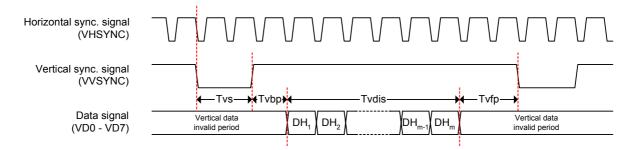

## 4.3.4 Display Interface

|           |                          | Alt. Func. 1 |            |            |                  | Alt. Func. 2   | Alt. Func. |

|-----------|--------------------------|--------------|------------|------------|------------------|----------------|------------|

| Pin Name  | Default                  | CCIR-656     | CCIR-601   | RGB 24-bit | Serial RGB 8-bit | TCON + RGB-666 | TCON       |

| VD0       | VGPIO[0]                 | YC[0]        | YC[0]      | VR0        | D0               | R0             |            |

| VD1       | VGPIO[1]                 | YC[1]        | YC[1]      | VR1        | D1               | R1             |            |

| VD2       | VGPIO[2]                 | YC[2]        | YC[2]      | VR2        | D2               | R2             |            |

| VD3       | VGPIO[3]                 | YC[3]        | YC[3]      | VR3        | D3               | R3             |            |

| VD4       | VGPIO[4]                 | YC[4]        | YC[4]      | VR4        | D4               | R4             |            |

| VD5       | VGPIO[5]                 | YC[5]        | YC[5]      | VR5        | D5               | R5             |            |

| VD6       | VGPIO[6]                 | YC[6]        | YC[6]      | VR6        | D6               | G0             |            |

| VD7       | VGPIO[7]                 | YC[7]        | YC[7]      | VR7        | D7               | G1             |            |

| VD8       | VGPIO[8]                 |              | VCCIR_C[0] | VG0        |                  | G2             |            |

| VD9       | VGPIO[9]                 |              | VCCIR_C[1] | VG1        |                  | G3             |            |

| VD10      | VGPIO[10]                |              | VCCIR_C[2] | VG2        |                  | G4             |            |

| VD11      | VGPIO[11]                |              | VCCIR_C[3] | VG3        |                  | G5             |            |

| VD12      | VGPIO[12]                |              | VCCIR_C[4] | VG4        |                  | В0             |            |

| VD13      | VGPIO[13]                |              | VCCIR_C[5] | VG5        |                  | B1             |            |

| VD14      | VGPIO[14]                |              | VCCIR_C[6] | VG6        |                  | B2             |            |

| VD15      | VGPIO[15]                |              | VCCIR_C[7] | VG7        |                  | В3             |            |

| VD16      | VGPIO[16]                |              |            | VB0        |                  | B4             |            |

| VD17      | VGPIO[17]                |              |            | VB1        |                  | B5             |            |

| VD18      | VGPIO[18]                |              |            | VB2        |                  | GPOL (GPO3)    | ckh2       |

| VDCK      | VGPIO[19]                | VDCK         | VDCK       | VPXCK      | VPXCK            | SCKH           | ckh1       |

| VHSYNC    | VGPIO[20]                | VHSYNC       | VHSYNC     | DVHSYNC    | DVHSYNC          | SSTH (GPO9)    | sth        |

| VDVALID   | VGPIO[21]                | VDVALID      | VDVALID    | DVDVALID   | DVDVALID         | GSTV (GPO4)    | stv        |

| VVSYNC    | VGPIO[22]                | VVSYNC       | VVSYNC     | DVVSYNC    | DVVSYNC          | GCKV (GPO5)    | ckv        |

| VSPOL     | VGPIO[23]                |              |            | VB3        |                  | SPOL (GPO2)    | com        |

| VSREV     | VGPIO[24]                |              |            | VB4        |                  | SREV (GPO0)    | q1h_ctr    |

| VSLD      | VGPIO[25]                |              |            | VB5        |                  | SLD (GPO7)     | oev1_mod2  |

| VGOEV     | VGPIO[26]                |              |            | VB6        |                  | GOEV (GPO6)    | oeh_mod1   |

| VDRVPDN   | VGPIO[27]                |              |            | VB7        |                  | PWRDN (GPO8)   | ckh3       |

| CLKIN_IDU | VGPIO[28] /<br>CLKIN_IDU |              |            |            |                  |                |            |

## 4.3.5 Panel Power PWM Interface

| Pin Name | Default  | Alt. Func. 1 | Alt. Func. 2   |

|----------|----------|--------------|----------------|

| VPWM0    | VPWM0    | PGPIO[0]     | I2CM_CLK (O)   |

| VPWM_FB0 | VPWM_FB0 | PGPIO[1]     | I2CM_DAT (I/O) |

| VPWM2    | VPWM2    | PGPIO[2]     | I2CS_CLK (I)   |

| VPWM_FB2 | VPWM_FB2 | PGPIO[3]     | I2CS_DAT (I/O) |

## 4.3.6 Secondary UART Interface

| Pin Name | Default  | Alt. Func. 1 | Pull H/L<br>Config. |

|----------|----------|--------------|---------------------|

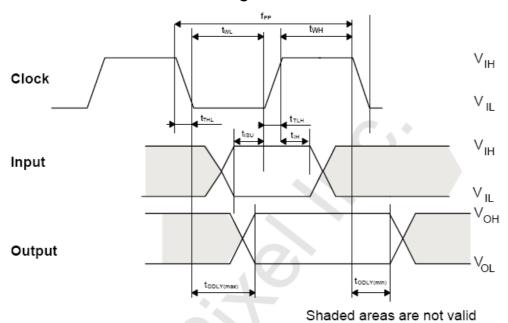

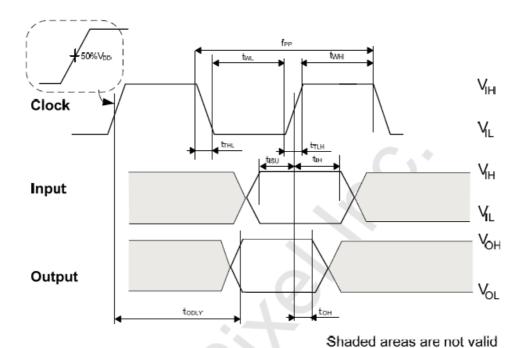

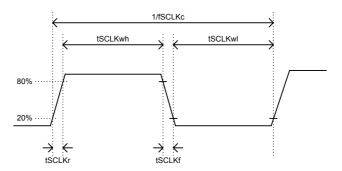

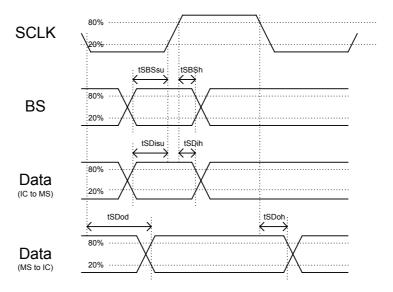

| HURX_B   | UGPIO[4] | HURX_B       | Н                   |