#### Controller Area Network (MultiCAN) Controller

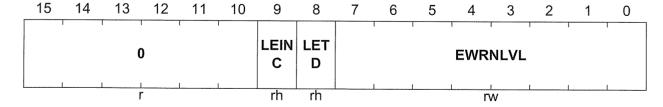

#### 22.2.3 CAN Node Control

Each CAN node may be configured and run independently from the other CAN nodes. To this end each CAN node is equipped with an individual set of SFR registers to control and to monitor the CAN node.

#### 22.2.3.1 Bit Timing

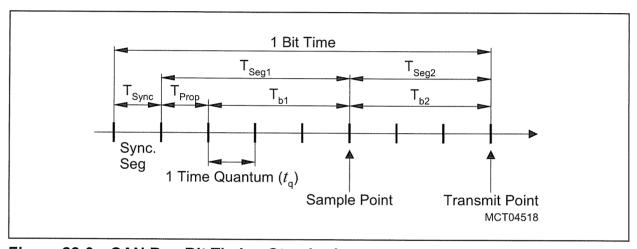

According to ISO 11898 standard, a CAN bit time is subdivided into different segments (**Figure 22-3**). Each segment consists of multiples of a time quantum  $t_q$ . The magnitude of  $t_q$  is adjusted by the bit field BRP and by bit DIV8, both controlling the baud rate prescaler (see bit timing register NBTR). The baud rate prescaler is driven by the MultiCAN module  $\operatorname{clock} f_{\operatorname{CAN}}$ .

Figure 22-3 CAN Bus Bit Timing Standard

The Synchronization Segment ( $T_{\rm Sync}$ ) allows a phase synchronization between transmitter and receiver time base. The Synchronization Segment length is always 1  $t_{\rm q}$ . The Propagation Time Segment ( $T_{\rm Prop}$ ) takes into account the physical propagation delay in the transmitter output driver, on the CAN bus line and in the transceiver circuit. For a working collision detect mechanism,  $T_{\rm Prop}$  has to be two times the sum of all propagation delay quantities rounded up to a multiple of  $t_{\rm q}$ . The Phase Buffer Segments 1 and 2 ( $T_{\rm b1}$ ,  $T_{\rm b2}$ ) before and after the signal sample point are used to compensate a mismatch between transmitter and receiver clock phase detected in the synchronization segment.

The maximum number of time quanta allowed for resynchronization is defined by bit field SJW in the CAN Node Bit Timing register NBTR. The Propagation Time Segment and the Phase Buffer Segment 1 are combined to parameter TSeg1, which is defined by the value TSEG1 in the respective CAN Node Bit Timing register NBTR. A minimum of 3 time quanta is requested by the ISO standard. Parameter TSeg2, which is defined by the value of TSEG2 in the CAN Node Bit Timing Register NBTR, covers the Phase Buffer Segment 2. A minimum of 2 time quanta is requested by the ISO standard. According

## XE167xM/XE164xM/XE162xM Derivatives XE166 Family / Base Line

#### Controller Area Network (MultiCAN) Controller

ISO standard, a CAN bit time, calculated as the sum of  $T_{\rm Sync,}$   $T_{\rm Seg1}$  and  $T_{\rm Seg2,}$  must not fall below 8 time quanta.

Calculation of the bit time:

$$\begin{array}{lll} {\rm t_q} & = {\rm (BRP+1)} \, / \, f_{\rm CAN} & {\rm if \, DIV8 = 0} \\ & = 8 \times {\rm (BRP+1)} \, / \, f_{\rm CAN} & {\rm if \, DIV8 = 1} \\ & T_{\rm Sync} & = 1 \, t_{\rm q} & & & \\ & T_{\rm Seg1} & = {\rm (TSEG1+1)} \times t_{\rm q} & {\rm (min. \, 3 \, } t_{\rm q}) \\ & T_{\rm Seg2} & = {\rm (TSEG2+1)} \times t_{\rm q} & {\rm (min. \, 2 \, } t_{\rm q}) \\ {\rm bit \, time} & = T_{\rm Sync} + T_{\rm Seg1} + T_{\rm Seg2} & {\rm (min. \, 8 \, } t_{\rm g}) \\ \end{array}$$

To compensate phase shifts between clocks of different CAN controllers, the CAN controller has to synchronize on any edge from the recessive to the dominant bus level. If the hard synchronization is enabled (at the start of frame), the bit time is restarted at the synchronization segment. Otherwise, the resynchronization jump width  $T_{\text{SJW}}$  defines the maximum number of time quanta a bit time may be shortened or lengthened by one resynchronization. The value of SJW is programmed in the CAN Node Bit Timing Register.

$$T_{SJW}$$

=  $(SJW + 1) \times t_q$

$T_{Seg1}$   $\geq T_{SJW} + T_{prop}$

$T_{Seg2}$   $\geq T_{SJW}$

The maximum relative tolerance for  $f_{\text{CAN}}$  depends on the Phase Buffer Segments and the resynchronization jump width.

dfCAN

$$\leq$$

min (Tb1, Tb2) / 2 × (13 × bit time - Tb2) AND dfCAN  $\leq$  TSJW / 20 × bit time

A valid CAN bit timing must be written to the CAN Node Bit Timing Register NBTR before resetting the INIT bit in the Node Control Register, i.e. before enabling the operation of the CAN node.

The Node Bit Timing Register may be written only if bit CCE (Configuration Change Enable) is set in the corresponding Node Control Register.

## XE167xM/XE164xM/XE162xM Derivatives XE166 Family / Base Line

### Controller Area Network (MultiCAN) Controller

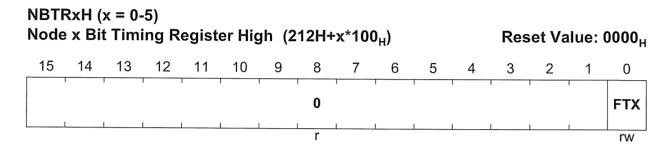

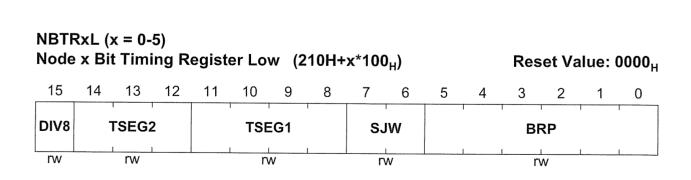

### 22.3.3.5 Node Bit Timing Register

The Node Bit Timing Register contains all parameters to setup the bit timing for the CAN transfer. NBTRx may be written only if bit NCRx.CCE is set.

| Field | Bits   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FTX   | 0      | rw   | Fast Transmit (TTC only) When a message is requested for transmission on the CAN bus, then the start of frame (SOF) symbol is sent with the beginning of a new bit time.  If the CAN bus is in the idle state and bit FTX is set (FTX = 1) then a new bit time is started immediately with the transmit trigger of a new message. This eliminates the variable delay between the transmit trigger of a message and the actual SOF signal on the transmit output. Such a variable delay occurs when transmit triggers occur at different positions within a CAN bit time. |

| 0     | [15:1] | r    | reserved; returns '0' if read; should be written with '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# XE167xM/XE164xM/XE162xM Derivatives XE166 Family / Base Line

### Controller Area Network (MultiCAN) Controller

| Field | Bits    | Type | Description                                                                                                                                                                                                                                                                                                                                               |

|-------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BRP   | [5:0]   | rw   | Baud Rate Prescaler The duration of one time quantum is given by (BRP + 1) clock cycles if DIV8 = 0. The duration of one time quantum is given by 8 × (BRP + 1) clock cycles if DIV8 = 1.                                                                                                                                                                 |

| SJW   | [7:6]   | rw   | (Re)Synchronization Jump Width (SJW + 1) time quanta are allowed for resynchronization.                                                                                                                                                                                                                                                                   |

| TSEG1 | [11:8]  | rw   | Time Segment Before Sample Point (TSEG1 + 1) time quanta is the user defined nominal time between the end of the synchronization segment and the sample point. It includes the propagation segment, which takes into account signal propagation delays. The time segment may be lengthened due to resynchronization.  Valid values for TSEG1 are 2 to 15. |

| TSEG2 | [14:12] | rw   | Time Segment After Sample Point (TSEG2 + 1) time quanta is the user defined nominal time between the sample point and the start of the next synchronization segment. It may be shortened due to resynchronization. Valid values for TSEG2 are 1 to 7.                                                                                                     |

| DIV8  | 15      | rw   | Divide Prescaler Clock by 8 $0_B$ A time quantum lasts (BRP+1) clock cycles. $1_B$ A time quantum lasts 8 × (BRP+1) clock cycles.                                                                                                                                                                                                                         |

### 22.3.3.6 Node Error Counter Register

NECNTxH(x = 0.5)

Node x Error Counter Register High(216H+x\*100<sub>H</sub>) Reset Value: 0060<sub>H</sub>