## UT61256 32K X 8 BIT HIGH SPEED CMOS SRAM

## WRITE CYCLE 1 ( WE Controlled) (1,2,3,5)

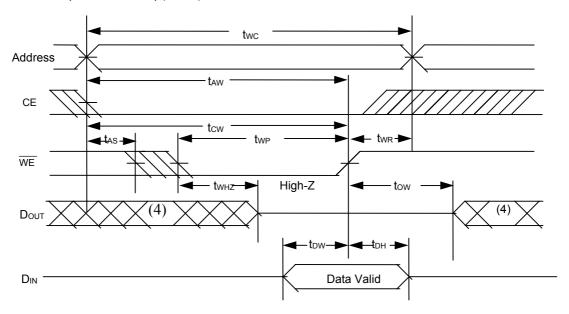

## WRITE CYCLE 2 (CE Controlled) (1,2,5)

## Notes:

- 1. WE or CE must be HIGH during all address transitions.

- 2. A write occurs during the overlap of a low  $\overline{\,\text{CE}\,}$  and a low  $\overline{\,\text{WE}\,}$  .

- 3. During a  $\overline{\text{WE}}$  controlled with write cycle with  $\overline{\text{OE}}$  LOW, twp must be greater than twHz+tpw to allow the drivers to turn off and data to be placed on the bus.

- 4. During this period, I/O pins are in the output state, and input signals must not be applied.

- 5. If the  $\overline{\text{CE}}$  Low transition occurs simultaneously with or after  $\overline{\text{WE}}$  Low transition, the outputs remain in a high impedance state.

- 6.  $t_{\text{OW}}$  and  $t_{\text{WHZ}}$  are specified with CL = 5pF. Transition is measured  $\pm 500 \text{mV}$  from steady state.

UTRON TECHNOLOGY INC. P80020