## MC68488 GPIA USER'S MANUAL

## Including an Introduction to the IEEE-Standard 488-1978 for Instrumentation Interface

Motorola reserves the right to make changes to any product herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the righte of others.

> ©Motorola Inc., 1980 All Rights Reserved

The second second 1-1-2-1-8-18  $g_{a,b,i} \leftarrow \sigma$ 10 Mar # 110 11

.....

. ....

## FOREWORD

The adoption of IEEE Standard 488-1978 is a significant step toward creation of universal instrumentation systems approach. This standard allows easy systems configuration involving instruments produced by different manufacturers. As such, it greatly simplifies the design of production testing, systems control or scientific data recording systems.

Quite naturally, the IEEE-Standard has generated a tremendous amount of interest among both instrument and computer manufacturers and measurement equipment users. Among the restraining factors on 488-1978 implementation have been the complexity of the logic protocol and the inavailability of low-cost ICs to satisfy the required logic control needs.

A multifunctional intelligent LSI device (MC68488) has been developed by Motorola to provide the interface between the IEEE-488 Standard bus (GPIB — General Purpose Interface Bus) and a parallel computer bus. This complex IC chip functions as an entire block allowing easy interaction with the GPIB. It performs many of the interface tasks automatically, reducing the software burden of the processor and improving throughput.

This manual describes the IEEE-488 Standard, and discusses Motorola's MC68488 (GPIA — General Purpose Interface Adapter) for system implementation. The document is intended for the prospective user as well as the experienced instrumentation designer. It can be used as a tutorial presentation, a detailed user's manual, or a reference guide.

This manual does not cover the IEEE Standard 488-1978 in its entirety. Instead it supplements and highlights the standard rather than replacing it. It will be assumed that the reader has access to copies of the complete standard for a detailed technical reference on the subject. Portions of this document have been taken from IEEE STD-1978 Digital Interface for Programmable Instrumentation, with permission of the Institute of Electrical and Electronics Engineers, Inc. Copies of IEEE STD 488-1978 may be purchased from IEEE, 345 East 47th Street, New York, N.Y. 10017, or from the American National Standards Institute, 1430 Broadway, New York, N.Y. 10018.

## TABLE OF CONTENTS

| Paragraph No. | Title Page                               | No  |

|---------------|------------------------------------------|-----|

|               | Chapter 1                                |     |

|               | Introduction                             |     |

| 1.1           | Traditional Approach to Interface Design | 1-1 |

| 1.2           | Purpose of IEEE-488 Standard             |     |

| 1.3           | Overview of the IEEE-488 Standard        | 1-4 |

| 1.4           | Summary                                  |     |

|               | Chapter 2                                |     |

|               | IEEE-488 Standard                        |     |

| 2.1           | Bus Line Callouts                        | 2-1 |

| 2.1.1         | Data Lines                               |     |

| 2.1.2         | Handshake Lines                          |     |

| 2.1.3         | Management Lines                         | 2-3 |

| 2.2           | Definitions                              |     |

| 2.3           | Conventions                              |     |

| 2.4           | Logic Levels 2-                          | -12 |

| 2.5           | Timing                                   |     |

| 2.6           | The Connector                            | 13  |

| 2.7           | Partitioning2-                           |     |

| 2.7,1         | Interface Functions2-                    | 16  |

| 2.7.2         | Message Coding2-                         | 17  |

| 2.7.3         | Drivers and Receivers2-                  |     |

| 2.8           | The Handshake2-                          | 18  |

| 2.8.1         | General Description2-                    | 18  |

| 2.8.2         | Timing of Handshake2-                    |     |

| 2.9           | State Diagrams2-                         | 22  |

| 2.9.1         | Descriptions and Definitions2-           | 22  |

| 2.9.2         | States2-                                 | 23  |

|               |                                          |     |

|               | Chapter 3                                |     |

|               | GPIA Features                            |     |

| 3.1           | Organization                             |     |

| 3.1.1         | Input/Output Functions                   |     |

| 3.1.1.1       | Interface with MPU                       |     |

| 3.1.1.2       | GPIA/GPIB Interface Bus Signals3         | -6  |

# TABLE OF CONTENTS (CONTINUED)

| Paragraph No. | Title                                               | Page No.      |

|---------------|-----------------------------------------------------|---------------|

| 3.1.1.3       | Control Signal                                      | 3-7           |

| 3.1.2         | Logic Conventions                                   | 3-8           |

| 3.1.3         | GPIA Registers                                      |               |

| 3.1.3.1       | Interrupt Status Register                           | 3-9           |

| 3.1.3.2       | Interrupt Mask Register                             | 3-11          |

| 3.1.3.3       | Command Status Register                             | 3-12          |

| 3.1.3.4       | Address Status Register                             | 3-13          |

| 3.1.3.5       | Address Mode Register                               | 3-14          |

| 3.1.3.6       | Auxiliary Command Register                          | 3-15          |

| 3.1.3.7       | Address Switch Register                             | 3-17          |

| 3.1.3.8       | Address Register                                    | 3-17          |

| 3.1.3.9       | Serial Poll Register                                | 3-18          |

| 3.1.3.10      | Command Pass-Through Register                       | 3-18          |

| 3.1.3.11      | Parallel Poll Register                              | 3-19          |

| 3.1.3.12      | Data-In Register                                    |               |

| 3.1.3.13      | Data-Out Register                                   | 3-19          |

| 3.2           | Interface Function — GPIA Recognition and Operation | 3- <b>2</b> 0 |

| 3.2.1         | Listener State                                      | 3-20          |

| 3.2.1.1       | Listener Mode (Primary addressing — apte = 0)       | 3-20          |

| 3.2.1.2       | Dual Primary Address Mode (apte = 0)                |               |

| 3.2.1.3       | Listener Extended Mode (apte = 1)                   | 3-23          |

| 3.2.1.4       | Listen Only Mode (io)                               | 3-25          |

| 3.2.2         | Talker State Diagrams                               |               |

| 3,2,2.1       | Talker Mode (Primary Addressing - apte = 0)         |               |

| 3.2.2.2       | Dual Primary Address Mode (apte = 0)                | 3-28          |

| 3.2.2.3       | Talker Extended Mode (apte = 1)                     | 3-29          |

| 3.2.2.4       | Talker Only (to)                                    | 3-30          |

| 3.2.3         | Service Request State/Serial Poll                   |               |

| 3.2.4         | Parallel Poll State                                 | 3-33          |

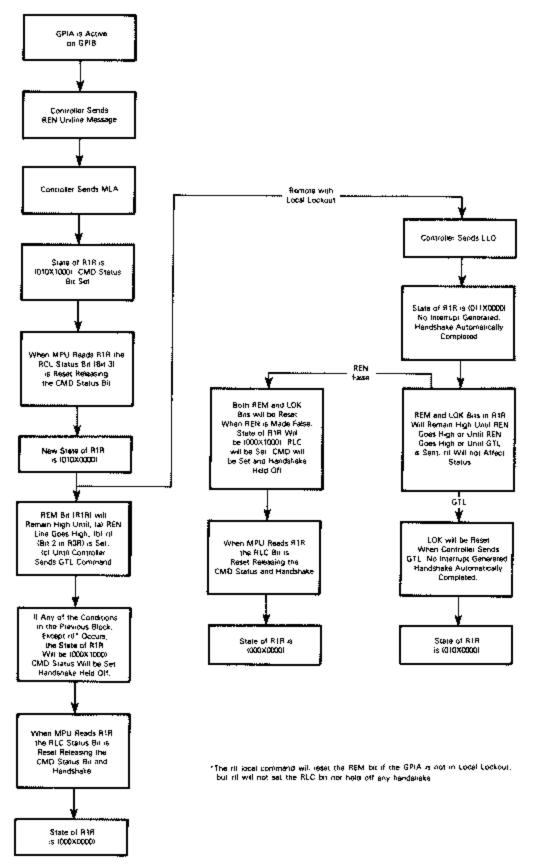

| 3.2.5         | Remote/Local State                                  | 3-34          |

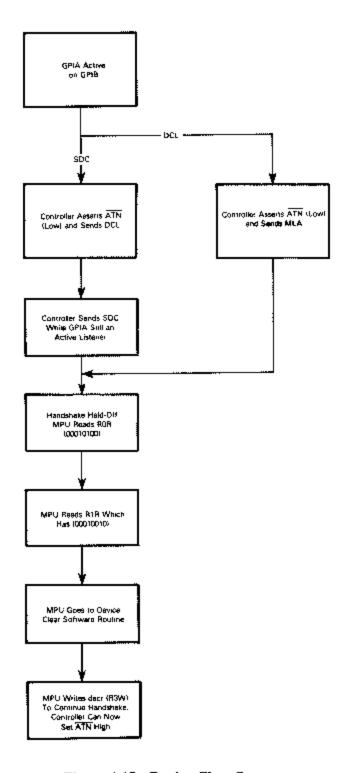

| 3.2.6         | Device Clear State                                  | 3-36          |

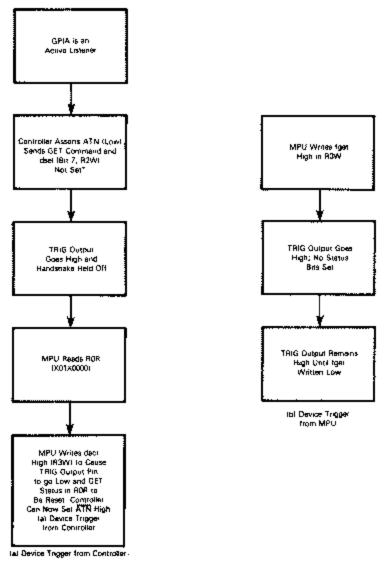

| 3.2.7         | Device Trigger State                                | 3-37          |

| 3.3           | Special Features                                    |               |

| 3.3.1         | Handshake Holdoff                                   | 3-38          |

| 3.3.1.1       | DAC Holdoff                                         | 3-39          |

| 3.3.1.2       | RFD Holdoff                                         |               |

| 3.3.2         | Interrupt Status                                    |               |

| 3.3.3         | DMA (Direct Memory Access)                          |               |

| 3.3.4         | Primary Address Recognition                         |               |

| 3.4           | Response to Remote Multiline Messages               |               |

## TABLE OF CONTENTS (CONCLUDED)

Paragraph No.

Title

Page No.

## Chapter 4 Programming Considerations

| 4.1     | Hardware Configuration               | ,41 |

|---------|--------------------------------------|-----|

| 4.1.1   | MPU Bus                              | 41  |

| 4.1.2   | Bus Transceiver                      | 4-6 |

| 4.1.2.1 | MC3448A                              |     |

| 4.1.2.2 | MC3447                               |     |

| 4.2     | GPIA Operations                      |     |

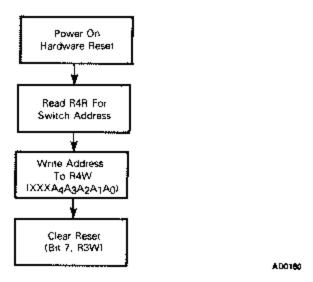

| 4,2,1   | Initialization                       |     |

| 4.2.2   | Interrupt Status Register Monitoring | 4-8 |

| 4.2.3   | Data Handling                        |     |

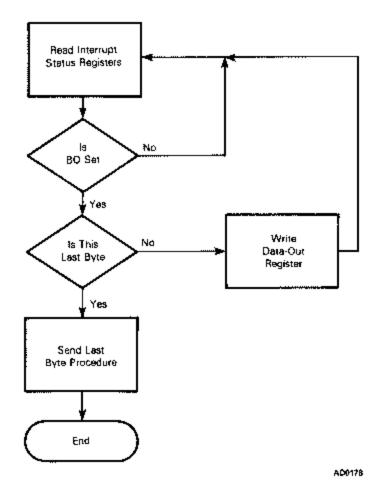

| 4.2.3.1 | Sending Data                         |     |

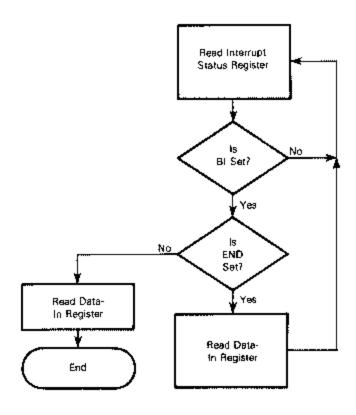

| 4.2.3.2 | Receiving Data                       |     |

| 4.2.4   | GPIA Interface Operation Modes       |     |

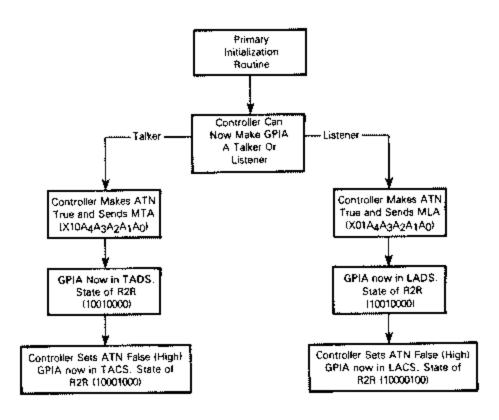

| 4.2.4.1 | Talker/Listener Addressing Modes     |     |

| 4.2,4,2 | Serial Poll With Service Request     |     |

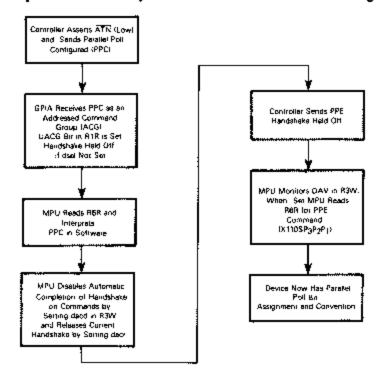

| 4.2.4.3 | Parallel Poll                        |     |

| 4.2.4.4 | Remote/Local                         |     |

| 4.2.4.5 | Device Clear                         |     |

| 4.2.4.6 | Device Trigger                       |     |

| 4.2.5   | DMA Operation                        |     |

| 4.3     | Example Programs                     |     |

| 4.3.1   | Basic Talker Software                |     |

| 4.3.2   | Basic Listener Software              |     |

| 4.4     | A/D-D/A System Example               |     |

| 4.4.1   | A/D System                           |     |

| 4,4,2   | D/A System                           |     |

| 4.5     | GPIA as a Controller                 |     |

| 4.5.1   | Hardware Configuration               |     |

| 452     | Operation                            |     |

# Appendix A IS0-7 Bit Code Representation

Appendix B

Questions and Answers

## LIST OF FIGURES

| Figure No. | Title Pa                                                                  | ge No. |

|------------|---------------------------------------------------------------------------|--------|

| 1-1        | Instrumentation System Prior to Standardization                           | 1-1    |

| 1-2        | System Configuration                                                      | ,,,1-2 |

| 1-3        | GPIB System (Adapters Not Needed)                                         | 1-3    |

| 1-4        | Interface Bus Structure                                                   | 1-5    |

| 1-5        | Typical Instrument Configuration                                          | 1-8    |

| 2-1        | A Possible Interface Bus Structure                                        | 2-2    |

| 2-2        | Typical TTL Implementation                                                | .2-12  |

| 2-3        | Typical Bus Load Line                                                     | .2-13  |

| 2-4        | Device Connector Mounting                                                 | ,2-14  |

| 2-5        | Cable and Connectors                                                      | .2-14  |

| 2-6        | Device Mounted Connector                                                  | .2-14  |

| 2-7        | Functional Partition Within A Device                                      | .2-15  |

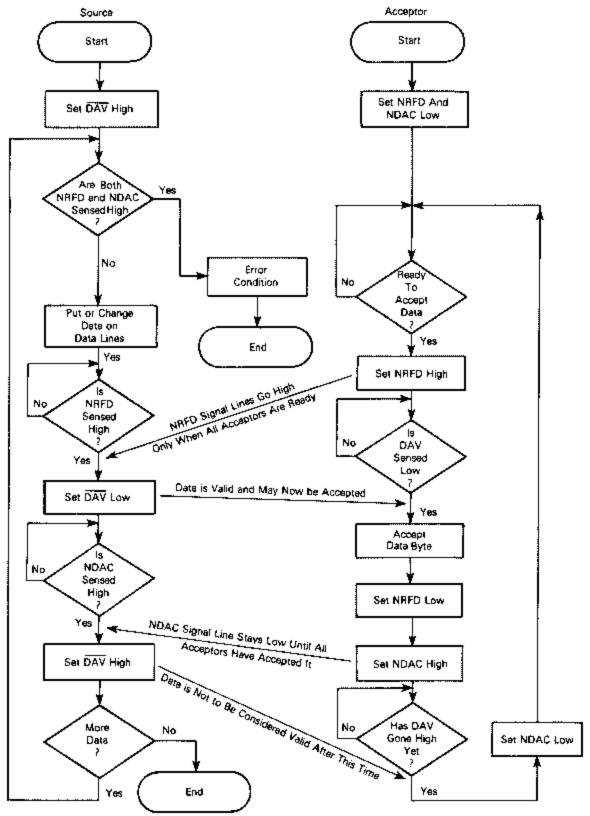

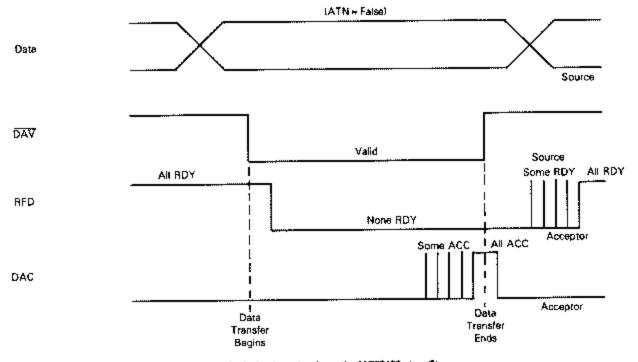

| 2-8        | Data Transfer                                                             | .2-21  |

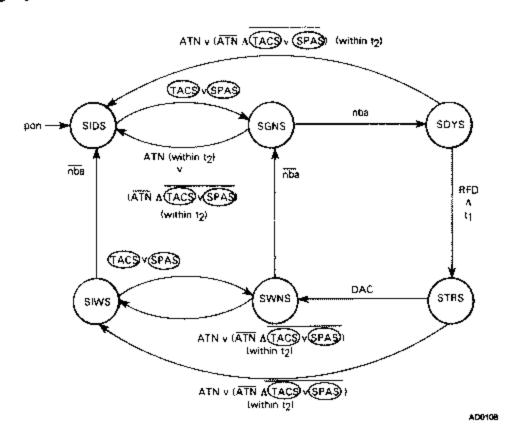

| 2-9        | Source and Acceptor Handshake Functions                                   | .,2-22 |

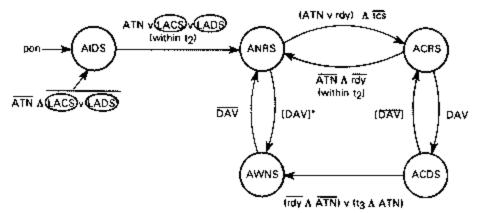

| 2-10       | State Diagram                                                             | 2-23   |

| 2-11       | Source Handshake State Diagram                                            | .Z-24  |

| 2-12       | Acceptor Handshake State Diagram                                          | .2-25  |

| 2-13       | Talker State Diagram (apte = $0$ , dat = $0$ )                            | 2-25   |

| 2-14       | Talker Extended Diagram (apte = 1, dat = 0)                               | 2-26   |

| 2-15       | Listener State Diagram (apte = 0, dat = 0)                                | .2-26  |

| 2-16       | Listener Extended State Diagram (apte = 1, dat = 0)                       | 2-27   |

| 2-17       | Service Request State Diagram                                             | 2-27   |

| 2-18       | Remote Local State Diagram                                                | 2-28   |

| 2-19       | Parallel Poll State Diagram                                               | 2-28   |

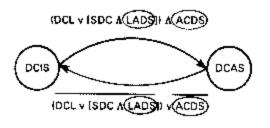

| 2-20       | Device Clear State Diagram                                                | 2-29   |

| 2-21       | Device Trigger State Diagram                                              | 2-29   |

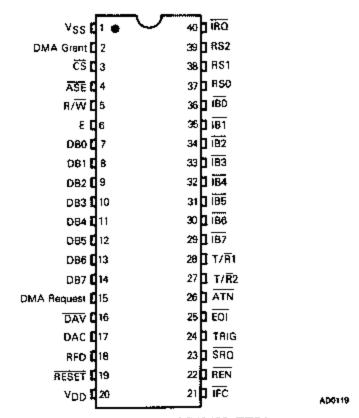

| 3-1        | Pinouts for MC68488 GPIA                                                  | 3-2    |

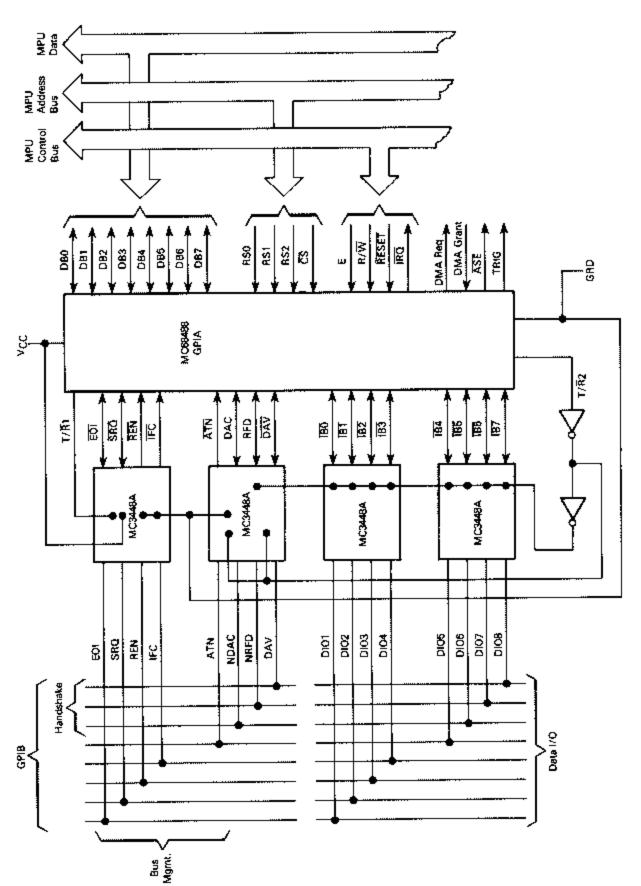

| 3-2        | MC68488 Interface Configuration                                           | 3-4    |

| 3-3        | Logic Notation Comparison Between MPU and GPIB                            | 3-8    |

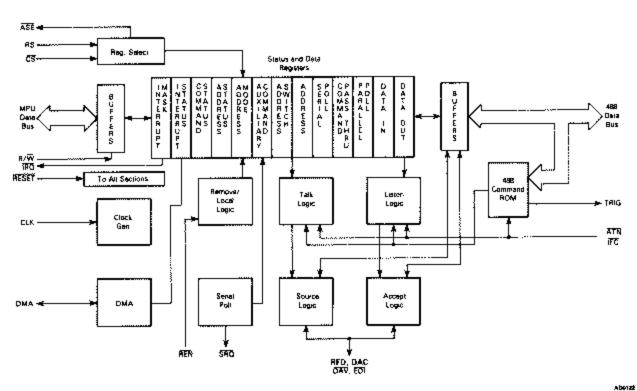

| 3-4        | Block Diagram of MC68488                                                  | 3-9    |

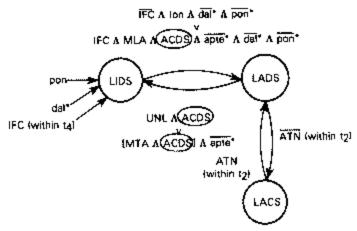

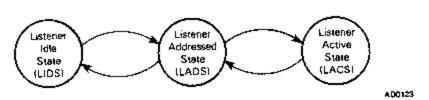

| 3-5        | Listen State Diagram                                                      | 3-20   |

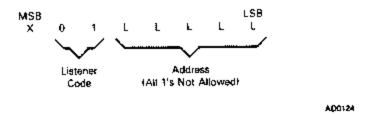

| 3-6        | MLA From Controller                                                       | 3-20   |

| 3-7        | Address Status Register (aote = 0)                                        | 3-21   |

| 3-8        | Interrupt Status Register For Listener                                    | 3-21   |

| 3-9        | Hold On End Option                                                        | 3-21   |

| 3-10       | Release of RFD Hold Off                                                   | 3-22   |

| 3-11       | Dual Primary Address Enable                                               | 3-22   |

| 3-12       | Acceptor MLAs from Controller in Dual Address Mode (R4W) Address = 00010. | 3-22   |

| 3-13       | Dual Primary Addressing (LSB Recognition)                                 | 3-23   |

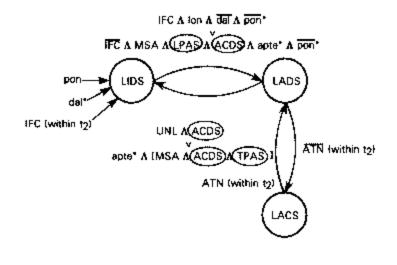

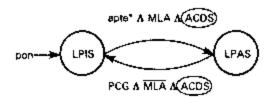

| 3-14       | LPAS State Diagram                                                        | 3-23   |

# LIST OF FIGURES (CONTINUED)

| Figure No. | Title                                                             | Page No.         |

|------------|-------------------------------------------------------------------|------------------|

| 3-15       | Secondary Address Command                                         | 3-24             |

| 3-16       | Interrupt Status For APT                                          |                  |

| 3-17       | Contents of Command Pass Through Register                         |                  |

| 3-18       | Listener Extended Mode                                            |                  |

| 3-19       | MPU Response to Secondary Address                                 | 3-25             |

| 3-20       | Listener Only Mode                                                | 3-25             |

| 3-21       | Removing GPIA From Listen Only Mode                               |                  |

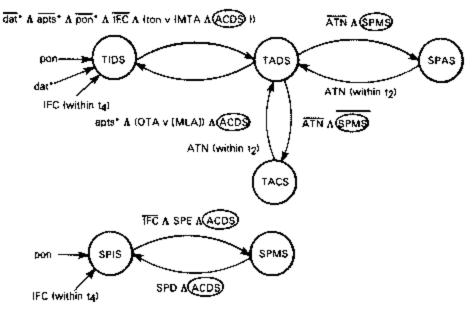

| 3-22       | Talker State Diagram                                              | 3-27             |

| 3-23       | MTA Sent by Controller                                            | 3-27             |

| 3-24       | Address Status Register After MTA Placed on GPIB (apte = 0)       |                  |

| 3-25       | Interrupt Status Register for BO                                  |                  |

| 3-26       | EIO Activation By Setting feei                                    | 3-28             |

| 3-27       | Accepted MTA(s) from Controller In Dual Address Mode (R4W Address | = 00010).3-29    |

| 3-28       | TPAS State Diagram (Talker Extended)                              | 3-29             |

| 3-29       | Talker Extended Mode                                              | 3-29             |

| 3-30       | Talker Only Mode                                                  | 3-30             |

| 3-31       | Removing GPIA From the Talk Only Mode                             | 3-31             |

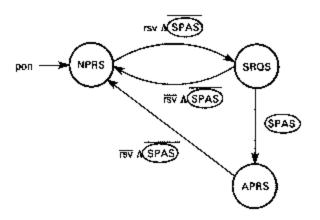

| 3-32       | Service Request State Diagram                                     |                  |

| 3-33       | Request for Service                                               | ,,,3- <b>3</b> 2 |

| 3-34       | Serial Poll Enable                                                | 3-32             |

| 3-35       | Serial Poll Active State                                          | 3-32             |

| 3-36       | Serial Poll Disable                                               | 3-33             |

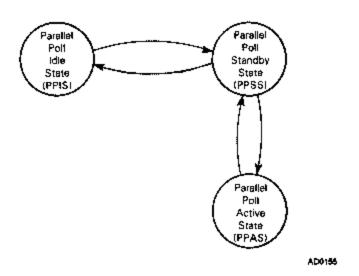

| 3-37       | Parallel Poll State Diagram ,                                     | 3-33             |

| 3-38       | Parallel Poli Register                                            |                  |

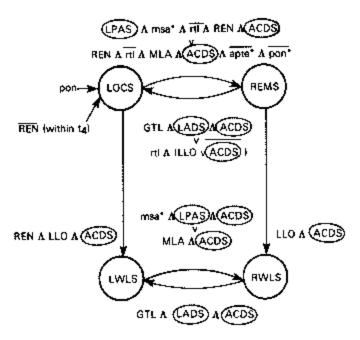

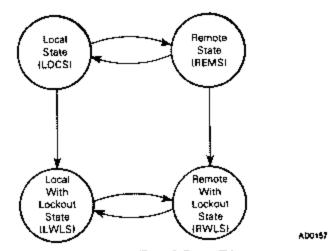

| 3-39       | Remote/Local State Diagram                                        | 3-34             |

| 3-40       | REMS Indication                                                   | 3-35             |

| 3-41       | RWLS Indication                                                   | 3-35             |

| 3-42       | LWLS Indication                                                   | 3-36             |

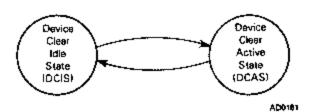

| 3-43       | Device Clear State Diagram                                        | 3-36             |

| 3-44       | DCAS Indication                                                   | 3-37             |

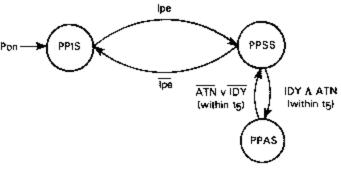

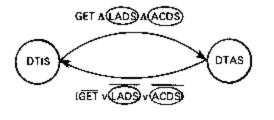

| 3-45       | Device Trigger State Diagram                                      |                  |

| 3-46       | DTAS Indication                                                   | 3-37             |

| 3-47       | fget Local Command                                                | 3-38             |

| 3-48       | DAC Handshake Release (hex 10)                                    | 3-39             |

| 3-49       | DAC Release with dacd Activated (hex 12)                          | 3-39             |

| 3-50       | RFD Holdoff                                                       | 3-40             |

| 3-51       | Ready for Data Release (rfdr hex 40)                              | 3-40             |

| 3-52       | VACG Interrupt (Effects of dsel and Mask Bits)                    | 3-41             |

| 3-53       | Address Register                                                  | 3-43             |

| 3-54       | Address Switches for Device Addresses                             | 3-44             |

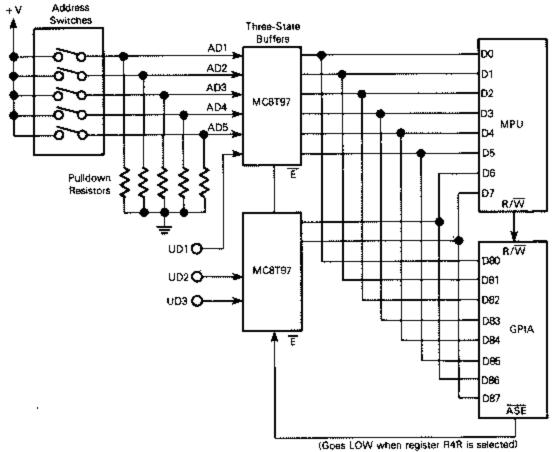

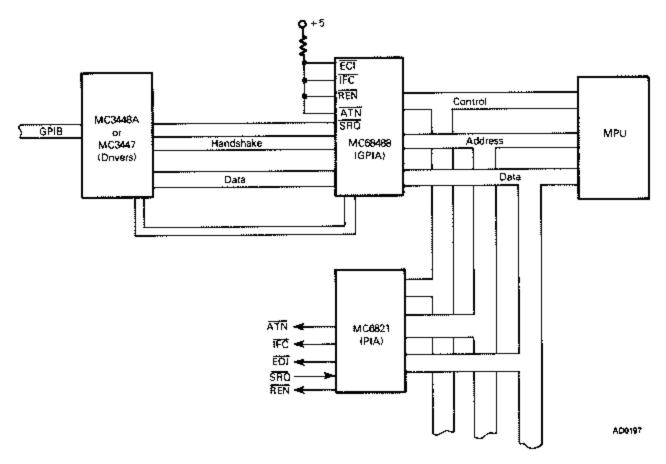

| 4-1        | Expanded GPIA/MPU System                                          | 4-2              |

| 4-2        | Device Address Connections                                        | 4-3              |

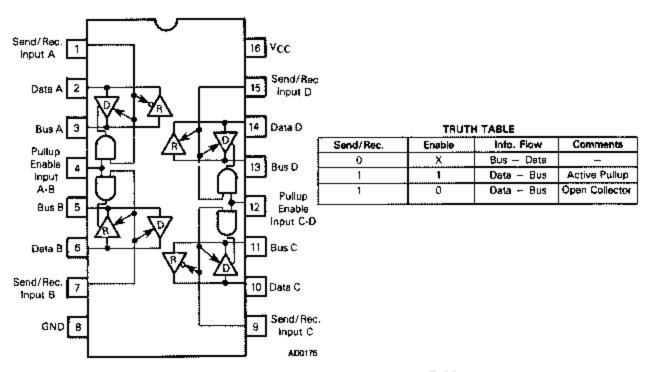

| 4-3        | MC3448A Pinouts and Truth Tables                                  | 4-5              |

| 4-4        | MC3448A Direction Control and Pullup Enable                       | 4-5              |

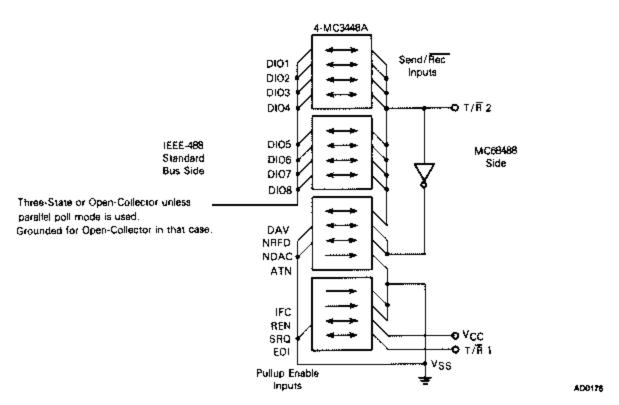

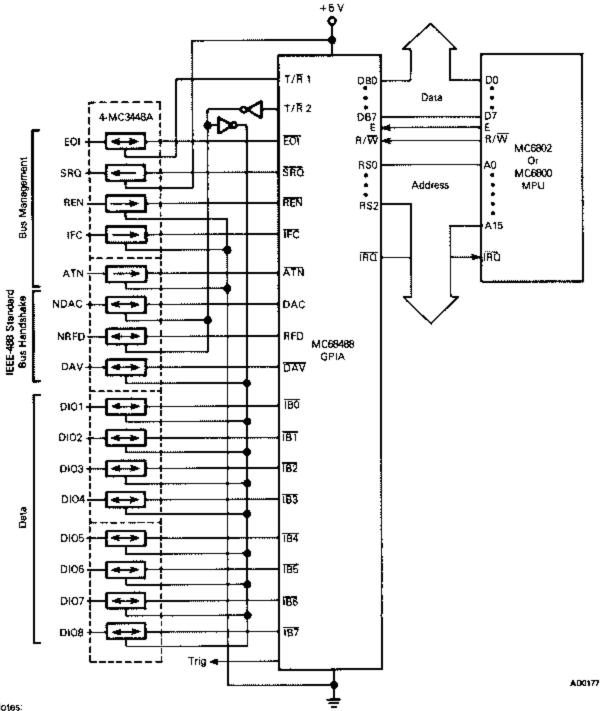

| 4-5        | Drivers/GPIA Configuration Using MC3448A Devices                  | 4-6              |

# LIST OF FIGURES (CONCLUDED)

| Figure No. | Title                                     | Page No.                              |

|------------|-------------------------------------------|---------------------------------------|

| 4-6        | Basic Talker Routine                      | 4-11                                  |

| 4-7        | Basic Listener Routine                    | 4-12                                  |

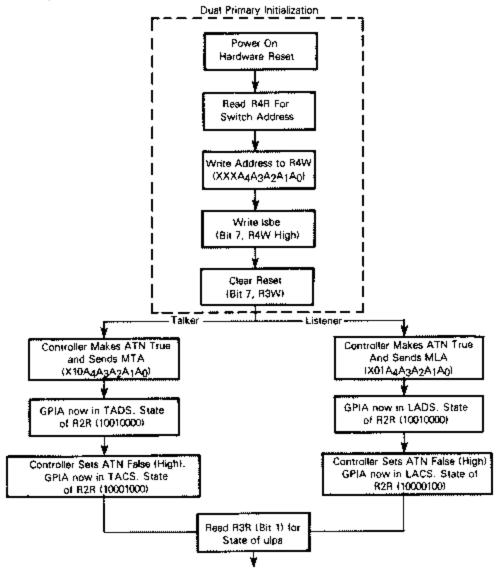

| 4-8        | Primary Initialization Routine            | 4-13                                  |

| 4-9        | Primary Talker/Listener Sequence          | 4-14                                  |

| 4-10       | Dual Primary Talker/Listener Sequence     | 4-15                                  |

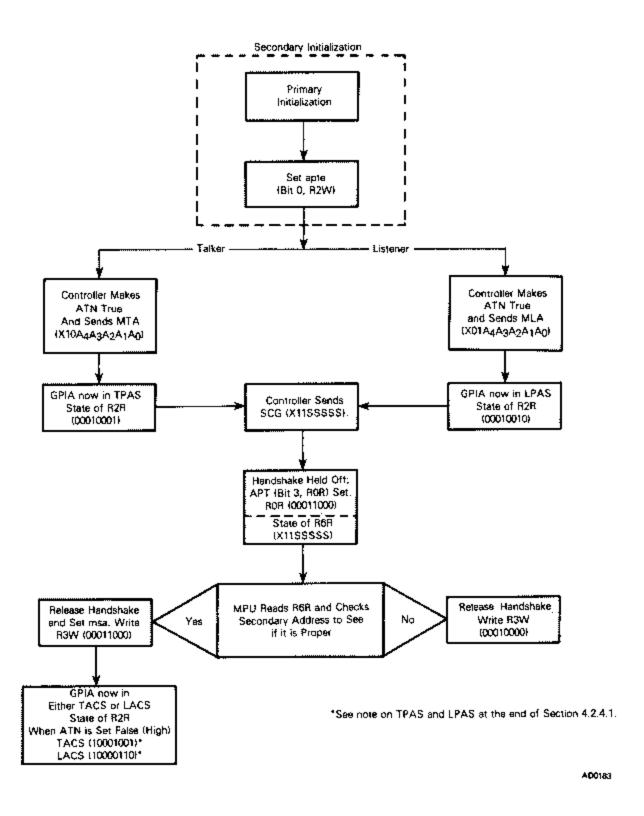

| 4-11       | Secondary Addressing Sequence             | ,,,,,4-17                             |

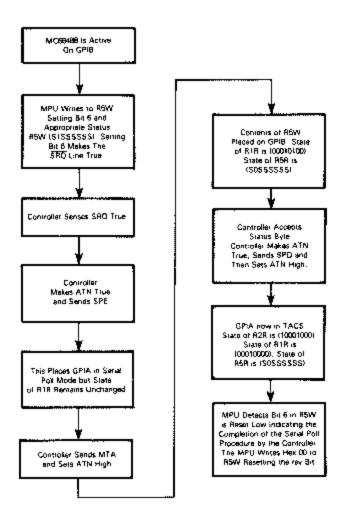

| 4-12       | Serial Poll Procedure                     | 4-19                                  |

| 4-13       | Serial Poll Sequence                      | 4-20                                  |

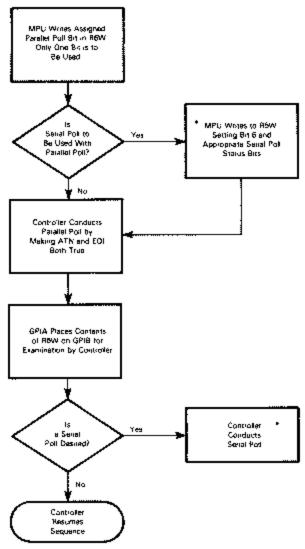

| 4-14       | Parallel Poll Sequence                    | 4-22                                  |

| 4-15       | Parallel Poll Assignment Sequence         | 4-23                                  |

| 4-16       | Remote/Remote-With-Local-Lockout Sequence | 4-25                                  |

| 4-17       | Device Clear Sequence                     | 4-26                                  |

| 4-18       | Device Trigger Sequence                   | 4-27                                  |

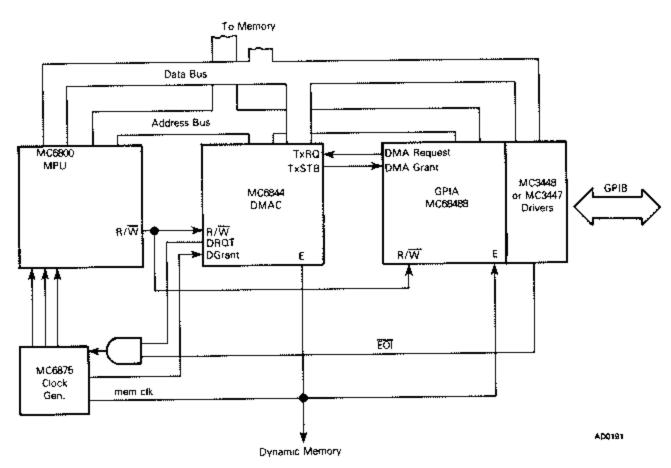

| 4-19       | DMA TSC Steal Block Diagram               | 4-28                                  |

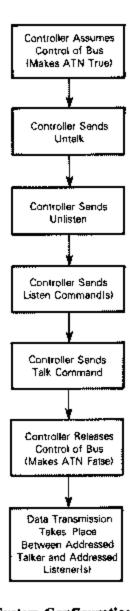

| 4-20       | System Configuration By Controller        | 4-33                                  |

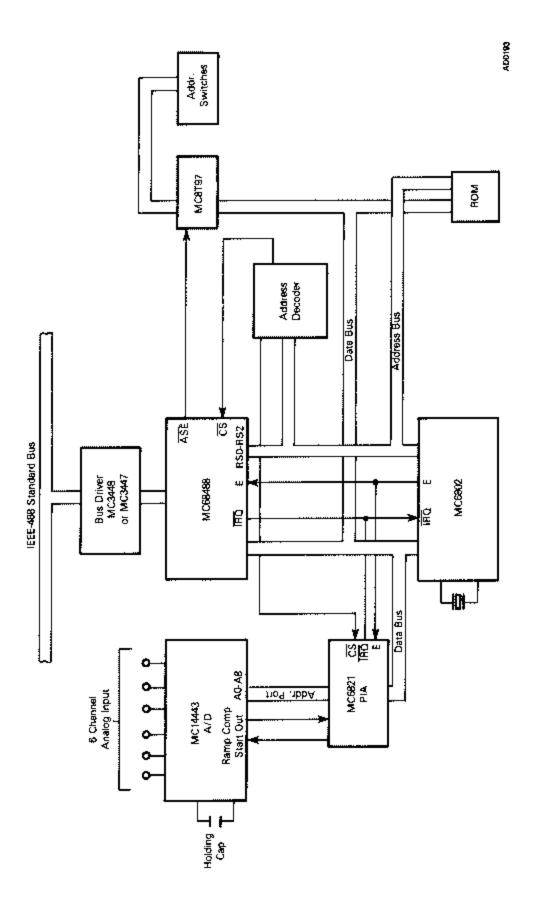

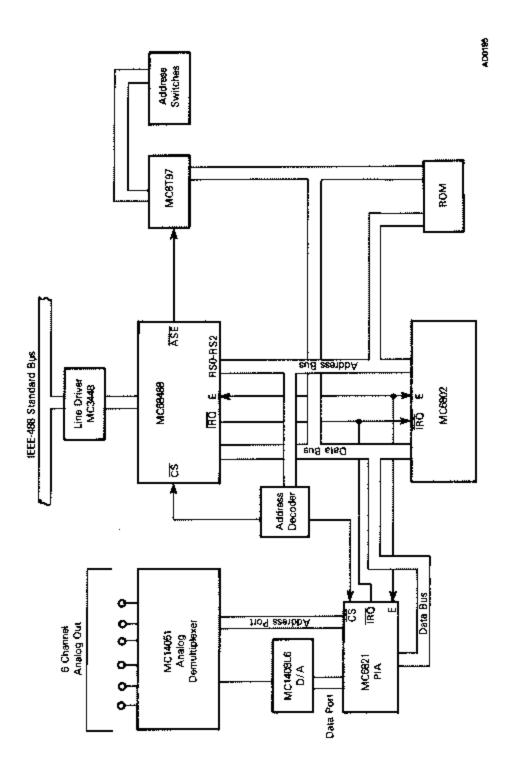

| 4-21       | Block Diagram of A/D-GPIB System          | 4-35                                  |

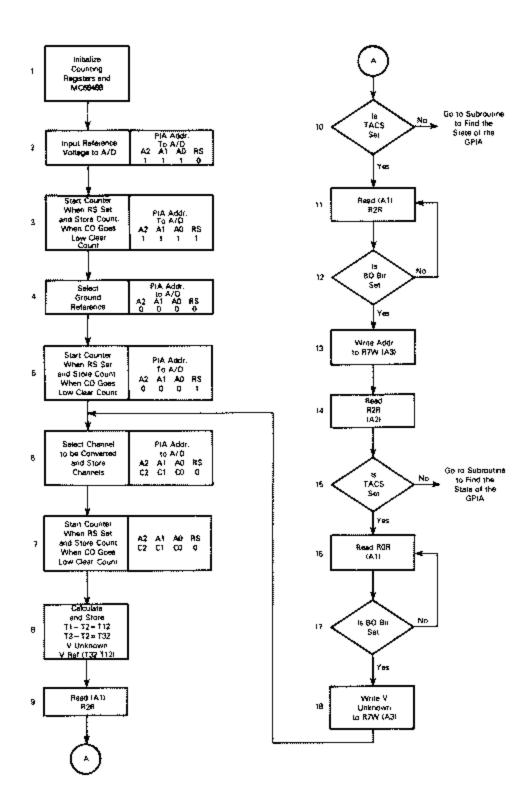

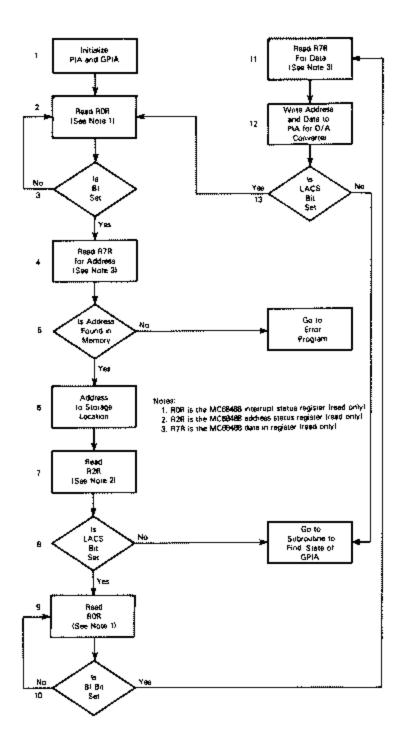

| 4-22       | Software Flow Chart for A/D System        | 4.37                                  |

|            | Block Diagram of D/A GPIA System          | 4_30                                  |

| 4-23       | Slock Diagram of D/A GFTA System          | 4_46                                  |

| 4-24       | Software Flow Chart for D/A System        | 4 41                                  |

| 4-25       | GPIA In a Controller Configuration        | <del>۱</del> ۱۰۰۰۰۰۰۹ <del>۹۹</del> ۱ |

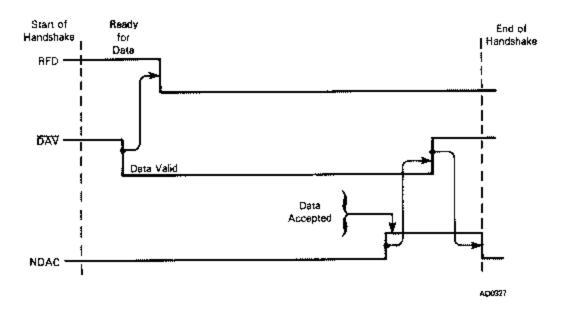

| B-1        | GPIA Handshake Sequence                   | B-3                                   |

## LIST OF TABLES

| Table No. | Title                                                       | Page No. |

|-----------|-------------------------------------------------------------|----------|

| 2-1       | Interface Specification                                     | 2-1      |

| 2-2       | Local Message Mnemonics                                     | 2-7      |

| 2-3       | Remote Message Mnemonics                                    |          |

| 2-4       | Interface State Mnemonics                                   |          |

| 2-5       | State Linkages                                              |          |

| 2-6       | Time Values                                                 |          |

| 2-7       | Connector Pin Assignments                                   |          |

| 2-8       | Basic Interface Functions                                   |          |

| 2-9       | Supplementary Interface Functions                           |          |

| 2-10      | Command Group Coding                                        |          |

| 2-11      | Remote Message Coding                                       |          |

| 3-1       | Description of MC68488 Pinouts                              | 3-2      |

| 3-2       | Register Access                                             |          |

| 3-3       | GPIA Register Contents                                      |          |

| 3-4       | Remote/Local State Indication                               |          |

| 3-5       | MC68488 Response to IEEE-488 Standard Multiline Messages    |          |

| 4-1       | MPU Address Map for GPIA                                    | 4-30     |

| A-1       | Multiline Interface Messages: ISO-7 Bit Code Representation |          |

| A-2       | Command and Address Formats                                 |          |

| A-3       | ASCII and Hexadecimal Equivalents                           |          |

| A-4       | ASCII Codes for Talk/Listen Commands                        |          |

## CHAPTER 1 INTRODUCTION

Communications between instruments, terminals, mass storage devices, etc., in an instrumentation system is accomplished by interconnecting these devices to a common bus. This means each device needs to be interfaced so its logic convention, signal levels, timing protocols, etc. are compatible with those of the other instruments in the system.

## 1.1 TRADITIONAL APPROACH TO INTERFACE DESIGN

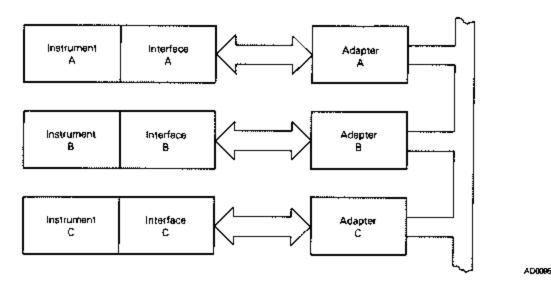

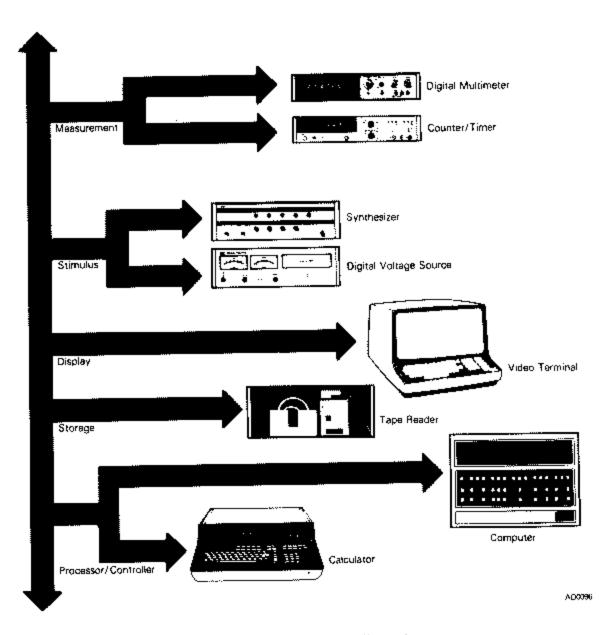

The traditional approach to interface design has been to provide each device (instrument) with a set of specialized controls, data, and status signals. A fairly easy straight-forward design was provided to achieve direct control of an instrument's programmable features; however, a problem resulted. The choice of signal lines, status lines, etc., which were to be made available, and the types of timing transitions between these lines were decided upon by the individual design engineer. Thus, there were about as many different interfacing techniques as design engineers. The net result was a dedicated interface structure for each instrument used in a system. Not only were interface structures for different manufacturers incompatible, but many instruments from the same manufacturer were incompatible. To accommodate all of the different structures (logic levels, signal levels, timing, etc.) many different adapters were built (Figure 1-1). This created a system with a mass of interconnecting cables and black boxes. As the sophistication of instrumentation systems increased — due mainly to the increase of highly programmable instruments — so did the complexity of the interface adapters. The resulting interface cost and complexity to achieve required performance levels, became unmanageable. The effort put into the wide variety of hardware design and the implementation of the necessary software was enormous — an interface standard was definitely needed.

Figure 1-1. Instrumentation System Prior to Standardization

## 1.2 PURPOSE OF IEEE-488 STANDARD

The purpose of the IEEE-488 Standard is to allow for interconnection of programmable instruments with minimum engineering. Its intent is to remove the need for adapters and numerous types of patching cables. The IEEE-488 Standard allows system configurations using programmable instruments, calculators, and other types of peripheral devices produced by different manufacturers (Figure 1-2). The IEEE-488 Standard provides a set of rules for establishing an unambiguous communications link, producing a high degree of compatibility and yet maintaining flexibility between independently manufactured products.

Figure 1-2. System Configuration

The IEEE-488 Standard defines the:

- Electrical Characteristics driver and receiver circuit parameters, logical and electrical signal levels, loading requirements, and ground requirements;

- Mechanical Characteristics connector type, contact assignments, and cable assembly;

- Functional Characteristics the complete repertoire and precise definition of each of the signal

lines, the protocol and timing relationships used to transfer all messages across the interface and

the response expected as a result of receiving these messages. There are ten defined functions

to be performed by the interface. These will be covered in Chapter 2.

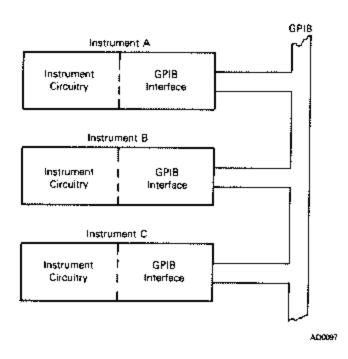

The IEEE-488 Standard defines a special bus structure known as the GPIB (General Purpose Interface Bus). Any device meeting the specifications described in the IEEE-488 Standard will be directly compatible with the GPIB without the need of an adapter (Figure 1-3). Motorola's MC68488 General Purpose Interface Adapter (GPIA) meets these requirements.

The standard applies to interface systems used to interconnect both programmable and non-programmable electronic measuring apparatus with other apparatus and accessories necessary to assemble instrumentation systems.

It applies to the interface of instrumentation systems or portions of them, in which the:

- 1. Data exchange between the interconnecting apparatus is digital (as distinct from analog);

- 2. Number of devices that may be interconnected by any contiguous bus does not exceed 15;

- 3. Total transmission path length over the interconnecting cables does not exceed 20 meters;

- 4. Data rate across the interface on any signal line does not exceed one Mega byte/second.

Figure 1-3. GPIB System (Adapters Not Needed)

The basic functional specifications of the IEEE-488 Standard may be used in digital interface applications which require longer distance, more devices, environments requiring increased noise immunity, or combinations of these parameters. Different electrical and mechanical specifications may be required (for example, symmetrical circuit configurations, high threshold logic, special connectors, or cable configurations) for those extended applications. However, applications of this type are not covered and are beyond the scope of the IEEE-488 Standard.

The IEEE-488 Standard is also applicable to other instrumentation system elements such as processors, stimulus units, display units, terminal units or mass storage devices. It applies generally to laboratory and production test or any other test environment which is both electrically quiet and restricted as to physical dimensions (distance between the system components).

The IEEE-488 Standard only specifies the operation of the GPIB and interface. It assures that data and control information will be transferred without error between the communication instruments. It does not specify the way this information will be interpreted by the instrument. It is up to the user to choose the type of data format and instrument control messages.

## 1.3 OVERVIEW OF THE IEEE-488 STANDARD

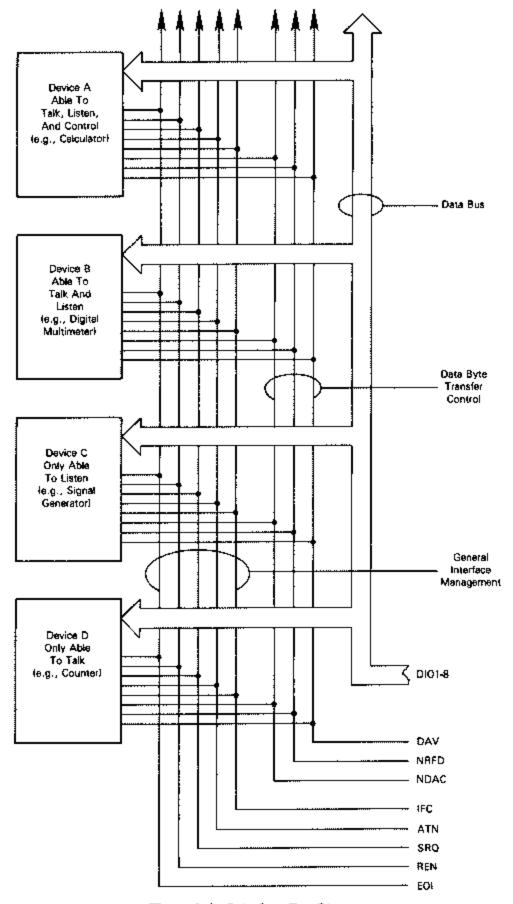

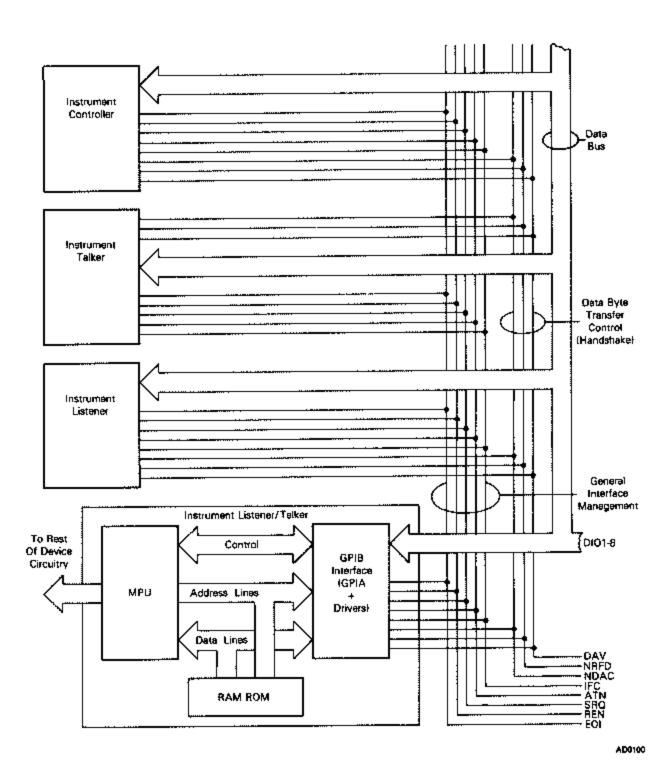

The GPIB can be thought of as the communications link between two or more instruments (Figure 1-4). This communications link is a parallel bus as opposed to the serial links associated with most other types of data communications. The transmission is that of a bit-parallel, byte-serial format, Bit-parallel refers to a set of concurrent data bits being transmitted simultaneously, and the byte-serial refers to consecutive bytes carried over the data link in a serial fashion. The GPIB consists of 16 transmission lines which are catagorized into:

- 1. eight data lines;

- 2. three data byte transfer control lines (handshake lines);

- 3. five general interface management signal lines.

The eight data lines are used to transfer data from the talkers to listeners. They are also used to transfer interface commands from the controller to various instruments. All transmission is asynchronous and all transmissions except parallel poll occurs according to a specialized 3-wire handshake (DAV, NRFD, and NDAC). It is with this handshake that the talker or controller synchronizes its readiness to transmit data to the listener's readiness to receive data.

At any point in time, an individual device on the bus will be idle monitoring the bus activity, a talker sending data to listeners on the bus, a listener receiving data from the talker on the bus, or a controller controlling the activity of the bus.

#### NOTE

Confusion sometimes arises in the meaning of the word controller. In the context of the IEEE-488 Standard and this manual, the word controller refers to a special device that connects to the GPIB. It is a complete unit in itself. The controller directs the flow of data by assigning devices to be either listeners or talkers. It can also interrupt the data flow and command specific actions within devices. The word controller does not refer to an MPU on the instrument side of the GPIB.

Figure 1-4. Interface Bus Structure

AD0098

Many devices are both talkers and listeners. A programmable multimeter, for instance, will be a listener when receiving its programmed instructions and a talker when sending its data to another device such as a printer or disk. There can be more than one listener at one time, but only one talker. A minimum system need not contain a controller but may consist of just one talker and one listener. For example, a dedicated voltmeter could be outputting data to a dedicated printer. In such a system, it will be necessary for the two devices to have interfacing options that will allow local messages from the device MPU to assign them as either a talker or a listener. The assignment will most likely be made during power-up and will not change. Controllers can only be omitted from such dedicated systems, i.e., systems where the functions of talker and listener are not automatically reassigned.

The controller alters activity on the bus by sending interface commands. The controller (currently active controller if more than one exists on the bus at the same time) is the only device capable of sending commands. It does this in one of two ways:

- Uniline Messages The controller can send a command over one of the five management lines, e.g., Interface Clear (IFC) or Remote Enable (REN).

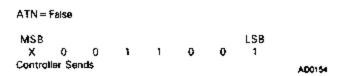

- 2. Multiline Messages The controller can send a command over the eight data lines. It does this by first asserting the ATN (Attention) management line signifying to all instruments on the bus that the eight data lines contain a multiline command or address rather than data.

These messages are interface commands which do not interact directly with the measurement process of an instrument. They interact only with the interface logic within connected devices. The primary purpose of these messages is to carry out the proper protocol in setting up, maintaining, and terminating an orderly flow of device dependent messages (device dependent messages refer to the information being sent by the addressed talker device to the addressed listener devices and not the messages used to control the interface). The multiline and uniline messages are used to address devices as either talkers or listeners, to signal an instrument to ignore or not ignore front panel settings, to inquire about any problem the device has, to reset the interface circuitry, to begin making a measurement, etc. Commands can be categorized as Universal Commands, Addressed Commands, Universal Addressed Commands, and Secondary Address or Commands. The command repertoire of the IEEE-488 Standard is covered in detail in Chapter 2.

Addresses are assigned to each device so it can respond to addressed commands. Using this address the controller can pick out a specific device and instruct it to be a talker or listener. The controller does not assign addresses; this must come from an external means such as a set of switches attached to the back panel of an instrument or a subroutine resident in the device software. The address is placed in the instrument GPIB interface during an initialization sequence. Once resident in the interface circuitry, the device can respond to addressed commands. The address is a 5-bit binary number that allows the controller to talk to a particular instrument.

A talker sends a data byte over the GPIB to a listener or listeners using the asynchronous 3-wire handshake. The transfer begins when the talker makes data available (DAV is asserted) and is completed when the slowest listener accepts the data byte (DAC is asserted). The third handshake line, RFD (Ready For Data), is used to signal the talker that the listeners are ready for data. There actually are four states in a data transfer.

- 1. The talker generates a new byte;

- 2. The states of the data bus signal lines settle;

- 3. The listeners accept the data;

- 4. The listeners become ready for the next byte.

Since there can be many listeners (maximum of 14; 14 listeners + 1 talker = 15 devices) it is possible to have some that respond very quickly (e.g., a disk) and some that respond slowly (e.g., a mechanical teletype) to the same data byte. Thus, the overall speed of transmission over the bus will be governed by, and will not exceed, the response rate of the slowest listener.

There is no restriction to data format on the GPIB. The only functional restriction is that the data be transmitted in 8-bit byte lengths. The choice of code and convention is up to the system designer. It should be pointed out, however, that many commercially available calculators used as system controllers have established codes and data formats. The development task will, in many instances, be simpler if the data formatting convention of all devices in the system is compatible. The IEEE-488 Standard, even though it doesn't restrict itself to any particular convention, is set up up to accommodate standard 7-bit ASCII code with ease. Because of this, many controllers have adapted the ASCII code. A table is given in Appendix A correlating the ISO-7 code convention to the IEEE-488 Standard multiline command codes.

The objective of the IEEE-488 Standard is to provide a set of rules which insure compatibility and yet are flexible enough to allow a designer freedom to tailor an instrument to his particular needs. To do this, the IEEE-488 Standard was developed in terms of interface functions (as distinct from instrument functions), messages to and from the interface functions, and state diagrams describing the behavior of each of these functions. Thus, an instrument operation is divided into two sets of functions, interface functions (which insures the instrument behaves correctly with respect to the GPIB signal lines) and device functions (which are used for specific instrument control, e.g., performing a voltmeter function). The device functions are beyond the scope of the IEEE-488 Standard. Note that the theoretical separation of device and interface functions does not imply a physical separation. The interface is partitioned (see Chapter 2 for further details) into ten interface functions. Five of these — Source and Acceptor Handshake, Talker, Listener, and Controller — provide the primary communications capability. The other five interface functions, Device Clear, Device Trigger, Service Request, Parallel Poll, and Remote/Local add special purpose capabilities. In turn, these interface functions interact with the device functions to form a complete operational unit.

### 1.4 SUMMARY

The IEEE-488 Standard is a much needed and internationally recognized standard. It is universal and encompasses many types of applications. As such, it is also a very complex interface standard. Among the restraining factors causing its slow adoption has been the complexity of the logic protocol and the unavailability of low cost LSI ICs to satisfy the required logic needs. Implementing the interface standard discretely could involve up to 190 TTL small scale integrated circuit packages. The number of packages would of course depend upon the number of interface functions to be implemented: not all of the interface functions are required for every application.

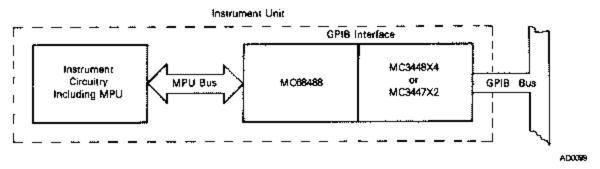

Motorola's MC68488 General Purpose Interface Adapter (GPIA) provides an easy, low cost interface to the IEEE-488 Standard instrumentation bus. The GPIA completely implements all of the IEEE-488 Standard interface functions (except that of the controller) as well as provides extra special purpose features. When used in conjunction with the MC3448 or MC3447 high current bus drivers, a set is formed which interfaces any 8-bit MPU standard bus to the IEEE-488 Standard instrumention bus (Figure 1-5).

Figure 1-5. Typical Instrument Configuration

This manual describes the IEEE-488 Standard and shows how the MC68488 is used to implement this standard, including application examples.

## CHAPTER 2 IEEE-488 STANDARD

The IEEE-488 Standard has become a recognized and accepted standard in the field of instrumentation. It is, however, not restricted to instrumentation and can be used in other areas that require an asynchronous parallel bus. This chapter highlights the standard, its system architecture and characteristics. The intent is to provide a working knowledge of the standard. For a more detailed description, a copy of the IEEE-488 Standard can be purchased from the IEEE headquarters in New York.

The general system defines all circuits, cables, connectors, control protocol, and message repertoire. Table 2-1 briefly outlines the general specifications for the interface system; the overall interface bus structure is illustrated in Figure 2-1.

Interconnected Devices Up to 15 maximum on one Contiguous bus Interconnection Path Ster or lineer bus network under 20 meters total transmission path length Signal Lines Sixteen total; eight data lines and eight lines for critical control and status messages Byte-serial bit-parallel asynchronous data transfer using interlocked Message Transfer Scheme three-wide handshake technique Data Rate One megabyte per second maximum over limited distances; 250-500 kilobytes per second typical over full transmission path Ten total; five primary communication functions and five special-Interface Function purpose functions Primary addresses, 31 talk and 31 listen; secondary (2-byte) address-Address Capability es, 961 talk and 961 listen Control Shift May be delegated, never assumed, with a maximum of one talker tup to 14 listeners) at a time Interface Circuits Oriver and receiver circuits TTL-compatible

Table 2-1. Interface Specification

### 2.1 BUS LINE CALLOUTS

The IEEE-488 Standard bus consists of a 24 line passive cable of which 8 lines are used for ground connection and the remaining 16 are signal lines categorized as:

- eight data bus signal lines;

- three handshake lines;

- five management lines.

The following is a description of each of these lines. Since the bus has a negative logic convention, a less positive voltage level is referred to as TRUE (binary 1) and a more positive voltage level is FALSE (binary 0).

Figure 2-1. A Possible Interface Bus Structure

#### 2.1.1 Data Lines

These are the message lines for carrying data in a bit-parallel, byte-serial form. Data is asynchronous and generally bidirectional. These lines carry either data or address/command information, depending upon the condition of the ATN management line.

#### 2.1.2 Handshake Lines

The three handshake lines (NRFD, DAV and NDAC) form a unique three-wire handshake for transferring information on the GPIB. The handshake lines provide the means to asynchronously transfer data between devices.

NRFD — The NRFD (Not Ready for Data) line is used to indicate the condition of readiness of devices to accept data. All instruments must drive NRFD passively High when ATN is Low. The NRFD line and the NDAC line are monitored by the controller when ATN is Low and by the Addressed Talker when ATN is High. The NRFD line is Low when any listener is not ready for data.

DAV — The DAV line (Data Valid) is used to indicate the validity of data on the data lines. DAV is driven by the Controller when ATN is Low and by the Addressed Talker when ATN is High. The DAV line is monitored by all instruments if ATN is Low and by Addressed Listeners when ATN is High. The DAV line is Low when data is valid.

NDAC — The NDAC (Not Data Accepted) line is used to indicate acceptance of data by Addressed Listeners. Listeners indicate acceptance of data by setting NDAC passively High. When NDAC is Low, one or more Listeners have not accepted the data.

## 2.1.3 Management Lines

The five bus management lines are IFC, ATN, SRQ, REN and EOI. IFC and ATN are used by all instruments while the remaining three may or may not be used by a particular instrument.

ATN — The ATN (Attention) line is used by the Active Controller to indicate how information on the data lines is to be interpreted. The ATN line must be monitored by all instruments other than the Active Controller at all times. When the ATN line is Low, the Active Controller can send interface messages and addresses to instruments on the bus. Data can be sent by the Active Talker to Active Listeners when the ATN line is high.

IFC — The IFC (Interface Clear) line is used by the System Controller to place the bus in a known quiescent state. The IFC line can only be driven low by the current System Controller and must be monitored by all other instruments. In order to clear an interface, the IFC line must be set low for at least 100 microseconds. IFC may be set by the current System Controller at any time. IFC puts talkers and listeners into their idle states.

REN — The REN (Remote Enable) line is used to operate an instrument under remote mode, e.g., interface control rather than front panel control. A Low level for the Remote Enable line is one of the conditions for operation of an instrument in remote mode. The REN line is driven by the current System Controller and may be changed at any time. Instruments which use the REN line must monitor it at all times and return to local control whenever it becomes High. The use of the remote function is optional.

SRQ — The SRQ (Service Request) line is used by an instrument to asynchronously request service from the Controller in charge of the GPIB. The SRQ line is sensed by the currently addressed Controller.

EOI — The EOI (End or Identify) line is used to indicate the end of a data string provided the ATN signal is High. When the ATN line is High, the Addressed Talker may indicate the end of its data by setting EOI Low at the same time it places the last byte on the data lines. The currently addressed Active Controller may initiate a Parallel Poll of all instruments with Parallel Polling capability by setting ATN and EOI Low simultaneously.

### 2.2 DEFINITIONS

A number of definitions or terminology are presented here to aid in understanding subsequent discussions of bus concepts. Unless otherwise noted with an asterisk (\*), these definitions are directly from the IEEE-488 Standard.

Active Transfer — A technique for resolving conflicts between two devices simultaneously sending opposite remote message values, whereby, the interface is so structured that the active value overrides the passive value.

Bidirectional Bus — A bus used by an individual device for two-way transmission of messages, that is, both input and output.

Bit-Parallel — Refers to a set of concurrent data bits present on a like number of signal lines used to carry information. Bit-parallel data bits may be acted upon concurrently as a group (byte) or independently as individual data bits.

Bus — A signal line or a set of signal lines used by an interface system to which several devices can be connected and over which messages are carried.

Byte - A group of eight adjacent binary digits operated on as a unit.

Byte-Serial — A sequence of bit-parallel data bytes used to carry information over a common bus.

Compatibility — The degree to which devices may be interconnected and used, without modification, when designed as defined throughout Section 2.3 and 4 of the IEEE-488 Standard.

Controller — A device that can address other devices to listen or to talk. In addition, this device can send interface messages to command specified actions within other devices. A device with only this capability neither sends nor receives device dependent messages.

#### NOTE

The use of the word controller throughout the IEEE-488 Standard applies strictly to the management (control) of the interface system and does not imply the broad capabilities typically associated with the word in the data processing context. Further classification of the controller is made in Section 2 of the IEEE-488 Standard to distinguish between different types of controller capabilities related to the interface system. Listener, talkers, and controller capabilities occur individually and collectively in devices interconnected via the interface system, as shown in Figure 2-1.

Device Dependent Messages — Messages used by the devices interconnected via the interface system, that are carried by but not used or processed by, the interface system directly. Device dependent messages are passed between the device functions and the message coding logic via specified interface functions. These will cause no state transitions within the interface functions. Examples of device dependent messages include device programming data, device measurement data, and device status data (see Figure 2-7, message route 3).

An Expression — Consists of one or more local messages, remote messages, state linkages, or minimum time limits used in conjunction with the operators AND, OR, or NOT.

Handshake Cycle — The process whereby digital signals affect the transfer of each data byte across the interface by means of an interlocked sequence of status and control signals. Interlocked denotes a fixed sequence of events in which one event in the sequence must occur before the next event may occur.

**High State** — The relatively more positive signal level used to assert a specific message content associated with one of two binary logic states.

Interface — A shared boundary between a considered system and another system, or between parts of a system, through which information is conveyed.

Interface Messages — Messages used to manage the interface system itself. Each interface message is sent to cause a state transition within another interface function. An interface message will not be passed along to the device when received by an interface function (see Figure 2-7, message route 2).

Interface System — The device-independent mechanical, electrical and functional elements of an interface necessary to effect communication among a set of devices. Cables, connector, driver and receiver circuits, signal line descriptions, timing and control conventions, and functional logic circuits are typical interface system elements.

Listener — A device that can be addressed by an interface message to receive device dependent messages from another device connected to the interface system. Listener, talker, and controller capabilities occur individually and collectively in devices interconnected via the interface system, as shown in Figure 2-1.

Local Control — A method whereby a device is programmable by means of its local (front or rear panel) controls in order to enable the device to perform different tasks. (Also referred to as manual control.)

Local Messages — Local messages flow between device functions and interface functions (see Figure 2-7, message route 5).

### NOTE

Certain local messages are conveyed as remote messages and vice versa.

The designer is not allowed to introduce new local messages to interface functions.

The designer is allowed to introduce a local message derived from any state of any interface functions to device function(s).

Local messages sent by device functions must exist for enough time to cause the required state transitions.

Low State — The relatively less positive signal level used to assert a specific message content associated with one of two binary logic states (a logic true).

Messages — Quantities of information carried by the interface system. A message will be received either true or false at any specific time.

All communication between an interface function and its environment is accomplished through message sent or received.

Message Coding — Message coding is the act of translating remote messages to or from interface signal lines values.

\*Mnemonic — Refers to a technique of abbreviations that has some easily remembered relationship to the name of the state or message; i.e., NY for New York, JFK for New York's John F. Kennedy Airport.

Multiline Message — A message that shares a group of signal lines with other messages, in some mutually exclusive set. Only one multiline message (message byte) can be sent at one time.

Passive Transfer — A technique for resolving conflicts between two devices simultaneously sending opposite remote message values. A passive value is not guaranteed to be the value received as it can be overridden by an active transfer.

**Programmable** — That characteristic of a device that makes it capable of accepting data to alter the state of its internal circuitry to perform two or more specific tasks.

**Programmable Measuring Apparatus** — A measuring apparatus that performs specified operations on command from the system and, if it is a measuring apparatus proper, may transmit the results of the measurement(s) to the system.

Remote Messages — Messages sent via the interface between interface functions of different devices are called remote messages.

Each remote message is either an interface message or a device dependent message.

Signal — The physical representation which conveys data from one point to another.

#### NOTE

For the purpose of the IEEE-488 Standard, this is a restricted definition of what is often called "signal" in more general sense, and is hereinafter referring to digital electrical signals only.

Signal Level — The magnitude of a signal when considered in relation to an arbitrary reference magnitude (voltage in the case of the IEEE-488 Standard).

Signal Line — One of a set of signal conductors in an interface system used to transfer messages among interconnected devices.

Signal Parameter — That parameter of an electrical quantity in which the values or sequence of values convey information.

State Linkage — The logical interconnection of two interface functions where the transition to an active state of one interface function is dependent upon the existence of a specified active state of another interface function (see Figure 2-7, message route 4).

System — A set of interconnected elements constituted to achieve a given objective by performing a specified function.

Talker — A device that can be addressed by an interface message to send device dependent messages to another device connected to the interface system.

Listener, talker, and controller capabilities occur individually and collectively in devices interconnected via the interface system, as shown in Figure 2-1.

Terminal Unit — An apparatus by means of which a connection (and translation, if required) is made between the considered interface system and another external interface system.

Unidirectional Bus — A bus used by any individual device for one-way transmission of messages only, that is, either input only or output only.

Uniline Message — A message sent over a single signal line. Two or more of these messages can be sent concurrently.

## 2.3 CONVENTIONS

Following the lead of IEEE-488 Standard, certain conventions will be followed throughout the remaining text and in all figures and diagrams.

Local Messages — All local messages to an interface function defined by the IEEE-488 Standard will be represented by three-letter lower case mnemonic. Example: rdy. Local messages are tabulated in Table 2-2.

Table 2-2. Local Message Mnemonics

| Mnemonic | Message Title                     |

|----------|-----------------------------------|

| gts      | go to standby                     |

| ISR      | individual service request (qual) |

| łon      | tisten only                       |

| lpe      | tocal poli enable                 |

| สเก      | listen                            |

| Ìμπ      | local unlisten                    |

| nba      | new byte available                |

| pon      | power on                          |

| rdγ      | ready                             |

| rpp      | request parallel poll             |

| гэс      | request system control            |

| 184      | request service                   |

| rtl      | return to local                   |

| sic      | send interface clear              |

| SI##     | send remote enable                |

| tca      | take control asynchronously       |

| tes      | take control synchronously        |

| ion      | talk only                         |

(a) IEEE-488 Standard specified local messages.

| apte | address pass through enable                     |

|------|-------------------------------------------------|

| daco | DAC disable Idisables automatic command mode)   |

| dacr | DAC release                                     |

| dal  | disable (intener                                |

| dat  | disable talker                                  |

| dsel | disable interrupt for GET, UACG, DUCG, SDC, DLC |

| leoi | force EOI line true                             |

| fget | force group execute trigger                     |

| hida | hold RFD on all data                            |

| hide | hold RFD on end of data                         |

| Isbe | least significent bit enable                    |

| má   | my address                                      |

| msa  | my secondary address                            |

| rfdr | RFD release                                     |

|      |                                                 |

<sup>(</sup>b) Non IEEE-488 Standard specified local messages. These 3 and 4 letter mnemonics represent additional local messages used by the MC68489 and are not part of the standard.

Remote Messages — All remote messages received via the interface will be represented by threeletter upper case mnemonic, Example: ATN. Remote messages are given in Table 2-3.

Table 2-3. Remote Message Macmonics

| Mnamonic     | Message Title             |

|--------------|---------------------------|

| ATN          | Attention                 |

| DAB          | Data Byte                 |

| DAC          | Data Accepted             |

| DAV          | Data Valid                |

| DCL          | Device Clear              |

| END          | End                       |

| GET          | Group Execute Trigger     |

| GTL          | Go To Local               |

| IDY          | Identify                  |

| IFC          | Interface Clear           |

| LLO          | Local Lock Out            |

| MLA or (MLA) | My Listen Address         |

| MSA or [MSA] | My Secondary Address      |

| MTA or [MTA] | My Talk Address           |

| OSA          | Other Secondary Address   |

| ATO          | Other Talk Address        |

| PCG          | Primary Command Group     |

| PPC          | Perellel Poll Configure   |

| [PPD]        | Parallel Poll Disable     |

| [PPE]        | Parallel Poli Enable      |

| PPRn         | Parallel Poll Response n  |

| PPU          | Parallel Poll Unconfigure |

| REN          | Remote Enable             |

| RFD          | Ready For Date            |

| RQ\$         | Request Service           |

| (SDC)        | Selected Device Clear     |

| SPD          | Serial Poll Disable       |

| SPE          | Serial Poll Enable        |

| SRO          | Service Request           |

| \$18         | Status Byte               |

| TCT or (TCT) | Take Control              |

| UNL          | Unfișten                  |

State Notation — Each state that an interface function can assume will be represented by a four-ietter upper case mnemonic with an S being the final letter. The mnemonic will be enclosed in a circle and all permissible transitions between states of the interface function will be represented by arrows between the circles. States are summarized in Table 2-4.

Linkage — A linkage from another state diagram will be represented by a four-letter mnemonic enclosed in an oval. Example: (LACS). Linkages are listed in Table 2-5.

Table 2-4. Interface State Mnemonics

| Mnemonic     | Message Title                                                                             |

|--------------|-------------------------------------------------------------------------------------------|

| ACDS         | Accept Data State                                                                         |

| ACRS         | Acceptor Ready State                                                                      |

| AIDS         | Acceptor Idle State                                                                       |

| ANRS         | Acceptor Not Ready State                                                                  |

| APRS         | Affirmative Poll Response State                                                           |

| AWNS         | Acceptor Weit For New Cycle State                                                         |

| CACS         | Controller Active State                                                                   |

| CADS         | Controller Addressed State                                                                |

| CAWS         | Controller Active Wait State                                                              |

| CIDS         | Controller Idle State                                                                     |

| CPPS         | Controller Perallel Poli State                                                            |

| CPWS         | Controller Parallel Poli Wait State                                                       |

| CSBS         | Controller Standby State                                                                  |

| CSNS         | Controller Service Not Requested State                                                    |

| CSRS         | Controller Service Requested State                                                        |

| CSWS         | Controller Synchronous Wait State                                                         |

| CTRS         | Controller Transfer State                                                                 |

| DCAS         | Device Clear Active State                                                                 |

| DCI\$        | Device Clear Idle State                                                                   |

| DTAS         | Device Trigger Active State                                                               |

| DTI\$        | Device Trigger Idle State                                                                 |

| LACS         | Listener Active State                                                                     |

| LADS         | Listener Addressed State                                                                  |

| LIDS         | Listener (die State                                                                       |

| LOGS         | Local State                                                                               |

| LPA\$        | Listener Primary Addressed State                                                          |

| LPIS         | Listener Primary Idle State                                                               |

| LWLS         | Local With Lockout State                                                                  |

| NPRS         | Negative Poll Response State                                                              |

| PACS         | Parallel Poll Addressed To Configure State                                                |

| PPAS         | Parallel Poll Active State                                                                |

| PPIS         | Parallel Poli Idle State                                                                  |

| PPSS         | Parallel Poli Standby State                                                               |

| PUC5         | Parallel Poll Unaddressed To Configure State                                              |

| REMS         | Remote State                                                                              |

| RWLS         | Remote With Lockout State                                                                 |

| SACS         | System Control Active State                                                               |

| SDYS         | Source Delay State                                                                        |

| SGNS         | Source Generate State                                                                     |

| SIAS         | System Control Interface Clear Active State                                               |

| SIDS         | Source Idle State                                                                         |

| SIIS         | System Control Interface Clear Idle State System Control Interface Clear Not Active State |

| SINS<br>SIWS | Source Idle Weit State                                                                    |

|              | System Control Not Active State                                                           |

| SNAS<br>SPAS | Serial Poll Active State                                                                  |

| SPIS         | Serial Poll Idle State                                                                    |

| SPMS         | Serial Poll Mode State                                                                    |

| SRAS         | System Control Remote Enable Active State                                                 |

| SRIS         | System Control Remote Enable Idle State                                                   |

| SRNS         | System Control Remote Enable Not Active State                                             |

| SRQS         | Service Request State                                                                     |

| STRS         | Source Trensfer State                                                                     |

| SWNS         | Source Walt For New Cycle State                                                           |

| TACS         | Talker Active State                                                                       |

| TADS         | Telker Addressed State                                                                    |

| TIOS         | Talker idle State                                                                         |

| TPAS         | Telker Primary Addressed State                                                            |

| TPIS         | Talker Primary Idle State                                                                 |

|              |                                                                                           |

Table 2-5. State Linkages

| State<br>Diagram | Mnemonic | Interface State                               |

|------------------|----------|-----------------------------------------------|

| SH               | TACE     | Talker Active State (T function)              |

| 5H               | SPAS     | Serial Poll Active State (T function)         |

| SH               | CACS     | Controller Active State (C function)          |

| \$H              | CTRS     | Controller Transfer State (C function)        |

| АН               | (IADS)   | Listener Addressed State (L function)         |

| AH               | (ACS)    | Listener Active State (L function)            |

| Т                | ACDS     | Accept Data State (AH function)               |

| TE               | (ACDS)   | Accept Data State (AH function)               |

| TE               | (IPAS)   | Listener Primary Addressed State (L function) |

| Ł                | (ACDS)   | Accept Data State (AH function)               |

| Ł                | CACS     | Controller Active State (C function)          |

| LE               | (ACDS)   | Accept Data State (AH function)               |

| LE               | CACS     | Controller Active State (C function)          |

| L€               | (IPAS)   | Telker Primary Addressed State (T function)   |

| SR               | SPAS     | Serial Poll Active State (T function)         |

| ŘL               | (ACDS)   | Accept Data State (AH function)               |

| RL               | (LADS)   | Listener Addressed State (L. function)        |

| PP               | (ACDS)   | Accept Data State (AH function)               |

| PP               | (LADS)   | Listener Addressed State (L function)         |

| DC               | (ACDS)   | Accept Data State (AH function)               |

| DC               | (LADS)   | Listener Addressed State (L function)         |

| DΤ               | ACDS     | Accept Data State (AH function)               |

| DΤ               | (ADS)    | Listener Addressed State (L. function)        |

| c                | (ACDS)   | Accept Date State (AH function)               |

| c                | (ANRS)   | Accept Not Ready State (AH function)          |

| C                | (SDYS)   | Source Delay State ISH function)              |

| c                | (STRS)   | Source Transfer State (SH function)           |

| c                | TADS     | Talker Addressed State (T function)           |

**Maximum Time** — If a transition has a maximum time limit, it will be indicated by the symbol t<sub>n</sub>. Thus the state pointed to, must be entered within a specified amount of time after the expression becomes true. See Table 2-6.

Minimum Time — A minimum time limit is represented by the symbol  $T_n$ . This symbol achieves a true value only after the interface has been in the state originating the transition for the time value specified. It will remain true until the state is exited. See Table 2-6 for these time limits.

- AND The AND operator is represented by the symbol A.

- OR The OR operator is represented by symbol v. (The AND operator takes precedence over the OR operator unless specified by parenthesis.)

- NOT The NOT operator is represented by a horizontal bar above the portion of the expression to be negated.

Active/Passive — The interface is so structured that conflicts, which may arise when opposite remote message values are simultaneously transmitted by two devices, are resolved. In such cases one message must always be made to override the other. Thus an active value will override a passive value when conflicts occur.

- T indicates active true.

- F indicates active false.

- (T) indicates passive true.

- (F) indicates passive false.

Optional True — If a portion of an expression is optional in that its true value is not required for the complete expression to be true, then it will be enclosed with square brackets [.....].

Time **Function** Value Description Value (Applies To) identifier\* Ti \$H Setting time for multiline messages ≥2 <u>д</u>91 SH, AH, T, L ≤ 200 ns Response to ATN t2 >05 Тз ΑH Interface message accept time\$ T, TE, L, LE, C Response to IFC or REN false < 100 µs 14 PΡ ≤ 200 ns Response to ATN A EOI 15 ¢ ≥ 2 ±5 Τ6 Parallel poli execution time ¢ Controller delay to allow current talker to see ATN message ≥ 600 ns ₹7 С Length of IFC or REN felse > 100 µs ₹ŝ C Delay for EOI\*\* ±1.5 ±s††

Table 2-6. Time Values

- (1) ≥ 1100 ns

- (2) Or ≥700 ns if it is known that within the controller ATN is driven by a three-state driver

- (3) Or ≥ 600 ns for all subsequent bytes following the first sent after each false transition of ATN lithe first byte must be sent in accordance with (1) or (2).

<sup>\*</sup>Time values specified by a lower case t indicate the maximum time allowed to make a state transition. Time values specified by an upper case T indicate the minimum time that a function must remain in a state before spition.

till three-state drivers are used on the DIO, DAV, and EOI lines, T<sub>1</sub> must be:

<sup>#</sup>Time required for interface functions to accept, not necessarily respond to, interface messages. Implementation dependent.

<sup>\*\*</sup>Delay required for EOI, NDAC, and NRFD signal lines to indicate valid states.

<sup>†1600</sup> ns for three-state drivers.

### 2.4 LOGIC LEVELS

Throughout the IEEE-488 Standard document the coded logical states 0 and 1 are utilized. A negative logic convention is defined as follows:

| Coding Logical State | Electrical Signal Level      |  |

|----------------------|------------------------------|--|

| 0 = False            | ≥2.0 V called the high state |  |

| 1 = True             | ≤0.8 V called the low state  |  |

Either open-collector or three-state drivers may be utilized with the following constraints:

- Open collector types are required on the following lines: SRQ, NRFD, and NDAC. In addition, if parallel polling is used, DIO1-DIO8 must also be open collector types.

- Three-state drivers are recommended for higher speed systems and especially in a controller ATN signal line, if used with other devices employing three-state drivers on the DAV, EOI and DIO1-DIO8 lines.

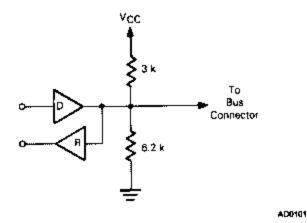

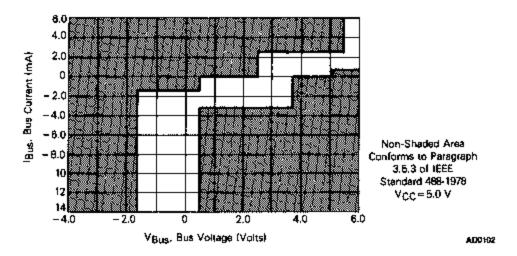

Drivers of either open-collector or three-state configuration must be capable of sinking +48 mA without exceeding 0.5 V. Three-state drivers must maintain 2.4 V, or greater, when sourcing 5.2 mA. Typical specifications for both open-collector and three-state drivers and receivers are given in the IEEE-488 Standard. When implemented with standard TTL logical elements and with a 3 k $\Omega$  resistor to VCC and a 6.2 k $\Omega$  resistor to ground at each common node, the typical suggested configuration is met (see Figure 2-2). The actual dc load requirement which must be met, however, is a function of driver, receiver, and resistive terminations. This load requirement is given in Figure 2-3.

Figure 2-2. Typical TTL Implementation

Figure 2-3. Typical Bus Load Line

The recievers may be standard TTL gates with 2.0 V high state input voltages or Schmitt trigger types employing hysteresis.

If hysteresis is utilized for improved noise immunity, it is recommended that at least 0.4 V be employed. It is also recommended that the lower threshold be greater than 0.8 V and the upper threshold less than +2.0 V. Negative voltage clamping is also required within the receiver.

#### 2.5 TIMING

All specified timing constraints are summarized in Table 2-6.

## 2.6 THE CONNECTOR

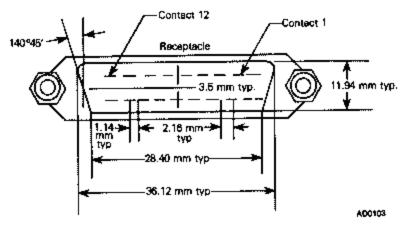

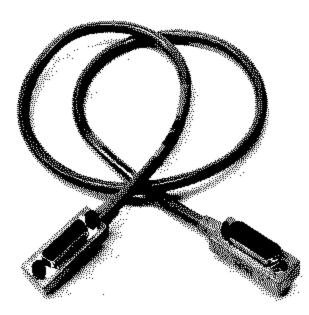

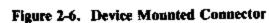

Both the dimensions and the actual pin locations of the connector are prescribed in the IEEE-488 Standard. Recommended connectors include MICRORIBBON (Amphenol or Cinch Series 57) or CHAMP (AMP). Illustrations of the connector, cables and pin connections are presented in Table 2-7 and Figures 2-4 through 2-6.

| Contact | Signal Line | Contact | Signal Line |

|---------|-------------|---------|-------------|

| 1       | DI01        | 13      | Ð105        |

| 2       | 0102        | 14      | DI06        |

| 3       | DI03        | 15      | DI07        |

| 4       | 0104        | 16      | DIOS        |

| 5       | EOI         | 17      | REN         |

| 6       | DAV         | 18      | Gnd. (6)    |

| 7       | NRFD        | 19      | Gnd. (7)    |

| 8       | NDAC        | 20      | Gnd. (8)    |

| 9       | IFC         | 21      | Gnd. (9)    |

| 10      | SRQ         | 22      | Gnd. (10)   |

| 11      | ATN         | 23      | Gnd. (11)   |

| 12      | SHIELD      | 24      | Gnd. ŁOGIC  |

Table 2-7. Connector Pin Assignments

Note: Gnd. (n) refers to the signal ground return of the referenced contact.

Figure 2-4. Device Connector Mounting

Figure 2-5. Cable and Connectors

Photos courtesy of Hewlett-Packard.

### 2.7 PARTITIONING

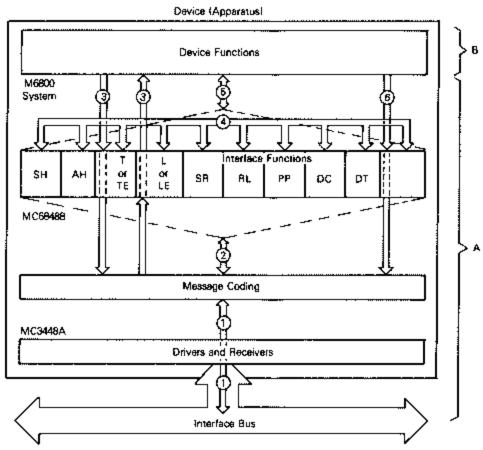

An IEEE-488 Standard compatible device can be divided into three major functional parts:

- 1. The device function;

- 2. The interface functions (5 basic and 5 supplementary);

- 3. The message coding logic.

Figure 2-7 shows the way the IEEE-488 Standard system is partitioned. The device functions, as mentioned earlier, are simply the application which the device has been designed to perform, e.g., voltmeter, signal generator, logic analyzer, etc.

- A Capability defined by the IEEE-488 Standard

- B Capability defined by the designer

- 1 Interface bus signal lines

- 2 Remote interface messages to and from interface functions

- 3 Device dependent messages to and from device functions

- 4 State linkages between interface functions

- 5 Local messages between device functions and interface functions (messages to interface functions are defined; messages from interface functions exist according to the designer's choice)

- Remote interface messages sent by device functions within a controller

AD0104

Figure 2-7. Functional Partition Within A Device

## 2.7.1 Interface Functions

The interface function is that part of the system which allows for the basic link through which a device can receive, process, and transmit messages. Table 2-8 and 2-9 list the ten interface functions defined by the standard.

Table 2-8. Basic Interface Functions

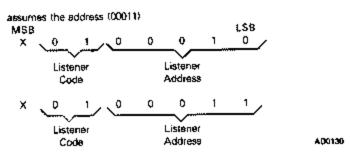

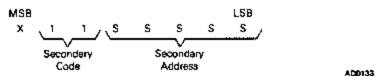

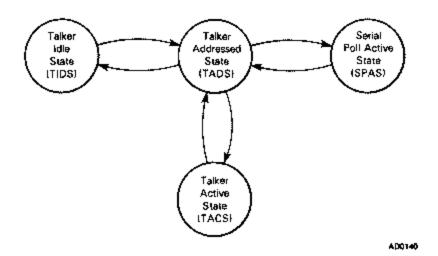

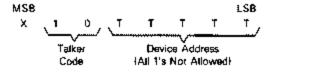

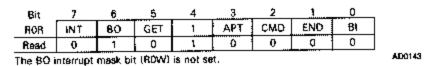

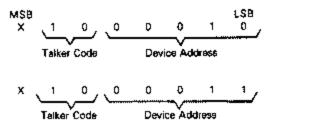

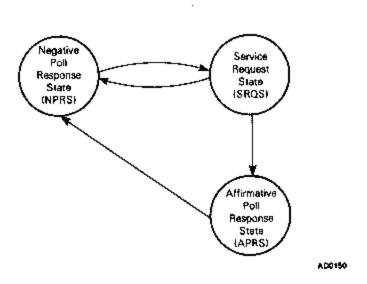

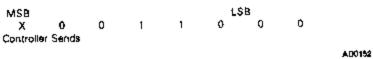

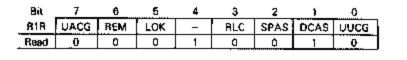

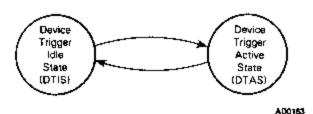

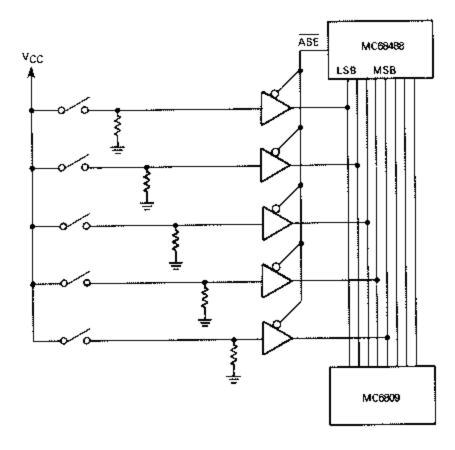

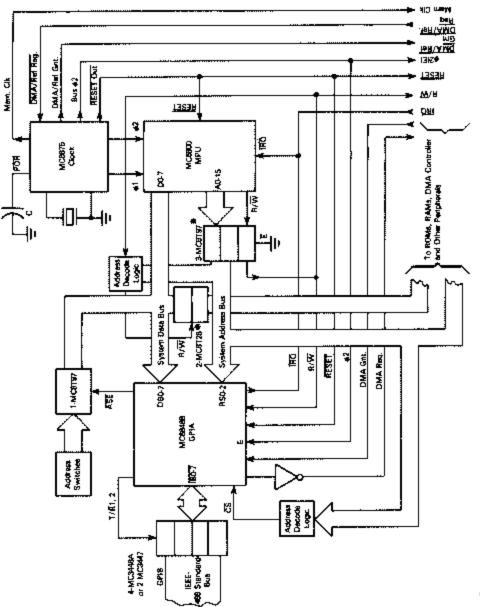

| Function                                | Description                                                                                                                                                                                   |  |