# DIGITAL ALARM CLOCK CIRCUIT

EA 5316 CONSUMER PRODUCTS

SEPTEMBER 1975

#### GENERAL DESCRIPTION

The EA5316 is a monolithic digital alarm clock circuit utilizing low voltage MOS P-channel enhancement mode and ion-implanted integrated circuit technology. The EA5316 utilizes line frequency (50 or 60 Hz) as its timing base, and provides a variety of timing functions suitable for a digital alarm clock, digital clock radio, and other applications. Four display modes are provided (hours and minutes, minutes and seconds, alarm, and sleep). The EA5316 drives seven segment clock displays and provides either a 12-hour or 24-hour format. Outputs consist of display drive, sleep (timed radio or event turn-off), and alarm enable. The EA5316 requires only a single unregulated power supply (-7 to -30 volts) and incorporates a power failure indication.

#### **FEATURES**

- 12 or 24 hour display format

- 24 hour alarm setting

- 9 minute snooze alarm

- Presettable 59 minute sleep timer

- AM/PM outputs (12 hr. format)

- Leading zero blanking (12 hr. format)

- Flashing colon for seconds indication

- Fast and slow set controls

- All counters resettable

- Elimination of illegal time display at turn-on

- Blanking/brightness control capability

- Power failure indication

- Direct interface to fluorescent tubes or liquid crystal displays. Also operates with LED's

- 50 or 60 Hz operation

- Single unregulated power supply

- Low power dissipation (32 mW @ 7V)

- Low input impedance for high noise margins

- Push-pull outputs on sleep and alarm buffers

- Alternate to NSC 5316 or AMI 1998

© 1975. Electronic Arrays, Inc.

## electronic arrays, inc.

550 east middlefield road, mountain view, california 94043 • telephone (415) 964-4321 • TWX 910-379-6985

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage at any Pin +0.3V to -31V

Operating Temperature Range (Ambient) 0°C to +70°C

Storage Temperature -55°C to +150°C

Stresses more severe than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and operation of the device at any condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### STANDARD TEST CONDITIONS

The characteristics below apply for the following standard test conditions unless otherwise noted. All voltages are referenced with respect to VSS.

$-30V \le V_{DD} \le -7V$

$0^{\circ}\text{C} \le \text{T}_{\text{A}} \le +70^{\circ}\text{C}$

$V_{SS} = 0V$

Common Sources = 0V

| Parameter                 | Condition                      | Min.                | Тур.     | Max.                | Units |

|---------------------------|--------------------------------|---------------------|----------|---------------------|-------|

| Power Supply Voltage VDD  | V <sub>SS</sub> = 0V           | -30                 |          | -7                  | Volts |

| Power Supply Current, IDD | $V_{SS} = 0V$ . No loads.      |                     |          |                     |       |

|                           | V <sub>DD</sub> = -7V          | 2                   |          | 4                   | mΑ    |

|                           | V <sub>DD</sub> = -30V         | 3                   | ļ        | 5                   | mΑ    |

| 50/60 Hz Inputs:          |                                |                     | 50 or 60 | ļ                   |       |

| Frequency                 |                                | DC                  | 00 0. 00 | 15K                 | Hz    |

| Voltage                   | (Note 1)                       |                     | †        |                     |       |

| VIH Logical High Level    |                                | V <sub>SS</sub> - 1 | 1        | VSS                 | Volts |

| VIL Logical Low Level     |                                | VDD                 |          | V <sub>DD</sub> + 1 | Volts |

| Blanking Input Voltage:   | (Note 1)                       |                     |          |                     |       |

| VIH Logical High Level    |                                | V <sub>SS</sub> - 2 |          | VSS                 | Volts |

| VIL Logical Low Level     |                                | VDD                 |          | V <sub>SS</sub> - 4 | Volts |

| All Other Input Voltages: | With active pulldown (Note 2). |                     |          |                     |       |

| VIH Logical High Level    |                                | V <sub>SS</sub> - 1 |          | VSS                 | Volts |

| VIL Logical Low Level     |                                | VDD                 |          | V <sub>DD</sub> + 2 | Volts |

| Parameter                        | Condition                                | Min. | Тур. | Max. | Units |

|----------------------------------|------------------------------------------|------|------|------|-------|

| Input Capacitance                | Except 50/60 Input                       |      |      | 6    | рF    |

| 50/60 Hz Input Capacitance       | 0 Volt Bias                              |      | 1    | 7.5  | pF    |

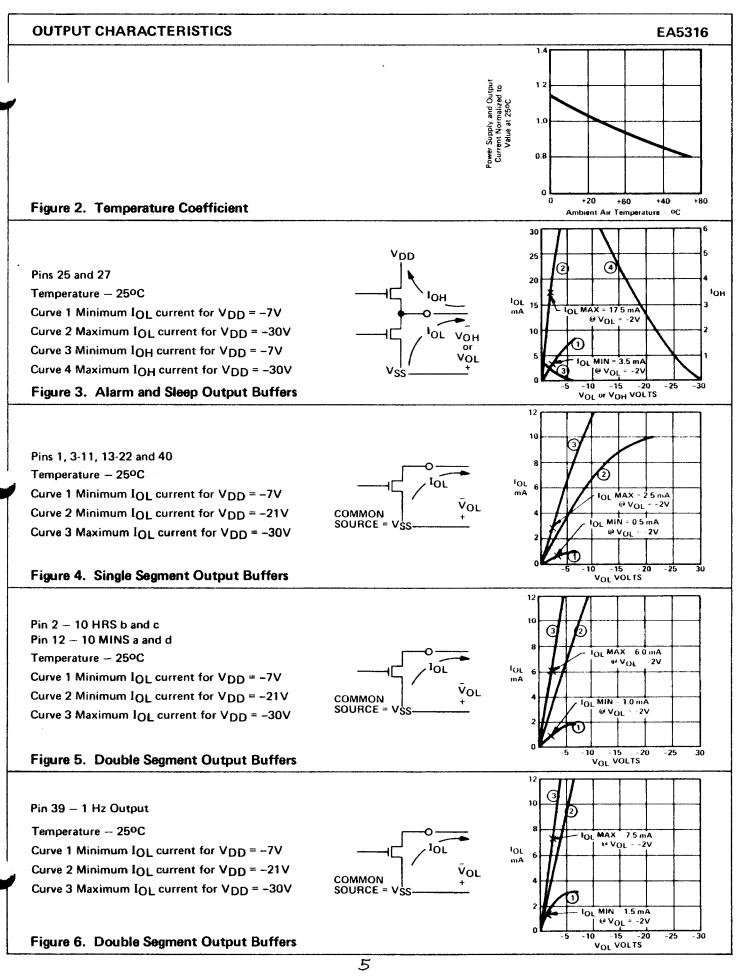

| Output Currents:                 | T <sub>A</sub> = +25°C                   |      |      |      |       |

| 1 Hz Display Outputs             |                                          |      |      |      |       |

| Logical High Level               | @ VOH = VSS - 2V                         | 1500 | 1    |      | μΑ    |

| Logical Low Level                | @ VOL = VDD = -30V                       |      | ,    | 1    | μΑ    |

| 10's of Hours (b and c), 10's of |                                          |      |      |      |       |

| Minutes (a and d) Outputs        |                                          | ļ    | İ    |      |       |

| Logical High Level               | @ VOH = VSS - 2V                         | 1000 | 1    |      | μΑ    |

| Logical Low Level                | @ VOL = VDD = -30V                       |      |      | 1    | μΑ    |

| Alarm and Sleep Outputs:         |                                          |      |      |      |       |

| Logical High Level               | @ V <sub>OH</sub> = V <sub>SS</sub> - 2V | 3500 |      |      | μΑ    |

| Logical Low Level                | @ VOL = VDD + 0.6V                       |      |      | 10   | μΑ    |

| All Other Display Outputs:       |                                          |      |      |      |       |

| Logical High Level               | @ V <sub>OH</sub> = V <sub>SS</sub> - 2V | 500  |      |      | μΑ    |

| Logical Low Level                | @ VOL = VDD = -30V                       |      |      | 1    | μΑ    |

| Power Fail Detect Voltage        | A.M. or P.M. flash                       | -20  |      | -8   | Volts |

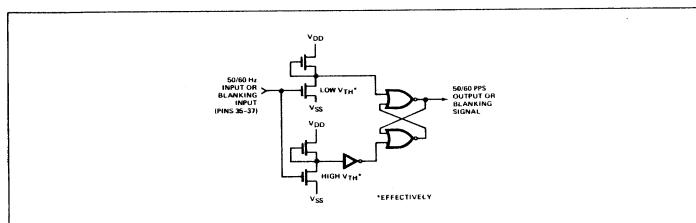

Note 1: Standard MOS input with leakage current of 1µA max. at V<sub>IN</sub> = -30 volts, all other pins at GND, and T<sub>A</sub> = +25°C. Input also contains Schmitt trigger circuit to provide hysteresis. (See Figure 1.)

Note 2: Inputs contain active pulldown resistor.  $30 \text{K}\Omega \leq \text{R}_{1\text{N}} \leq 150 \text{K}\Omega$ , @  $\text{V}_{1\text{N}} = \text{V}_{SS}$ .

### **FUNCTIONAL DESCRIPTION**

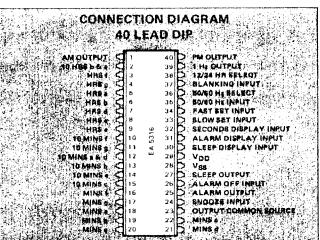

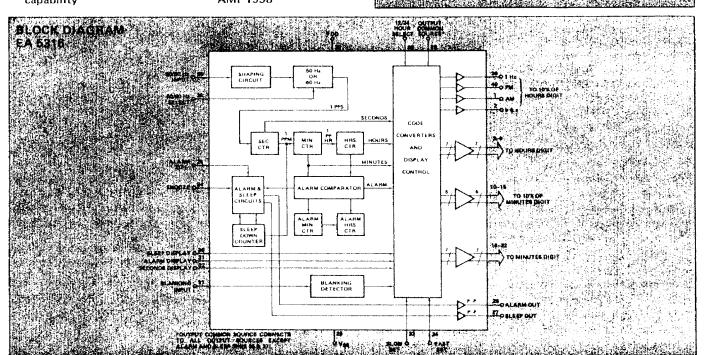

A block diagram of the EA 5316 digital alarm clock is shown on page 1. The various display modes provided by this clock are listed in Table 1. The functions of setting controls are listed in Table 2. The following discussions are based on the Block Diagram.

50 or 60 Hz Input (pin 35): A shaping circuit is provided to square the 50 or 60 Hz input (see Figure 1). This circuit allows use of a filtered sinewave input. The circuit is a Schmitt trigger that is designed to provide about 6V of hystersis. A simple RC filter should be used to remove possible linevoltage transients that could either cause the clock to gain time or damage the device. The input should swing between VSS and VDD. The shaper output drives a counter chain which performs the timekeeping function.

50 or 60 Hz Select Input (pin 36): A programmable prescale counter divides the input line frequency by either 50 or 60 to obtain a 1-pps time base. This counter is programmed to divide by 60 simply by leaving pin 36 unconnected; pull-down to VDD is provided by an internal  $150 \mathrm{K}\Omega$  resistor. Operation at 50 Hz is programmed by connecting pin 36 to VSS.

Display Mode Select Inputs (pins 30 through 32): In the absence of any of these three inputs, the display drivers present time-of-day information to the appropriate display digits. Internal  $150 \mathrm{K}\Omega$  pull-down resistors allow use of simple SPST switches to select the display mode. If more than one mode is selected, the priorities are as noted in Table 1. Alternate display modes are selected by applying VSS to the appropriate pin. As shown in the Block Diagram, the code converters receive time, seconds, alarm and sleep information from appropriate points in the clock circuitry. The display mode select inputs control the gating of the desired data to the code converter inputs and ultimately (via output drivers) to the display digits.

Time Setting Inputs (pins 33 and 34): Both fast and slow setting inputs are provided. These inputs are applied either singly or in combination to obtain the control functions listed in Table 2. Again, internal  $150 \mathrm{K}\Omega$  pull-down resistors are provided; application of VSS to these pins effects the control functions. Note that the control functions proper are dependent on the selected display mode. For example, a hold-time control function is obtained by selecting seconds display and actuating the slow set input. As another example, the clock time may be reset to 12:00:00 A.M., in the 12-hour format (00:00:00 in the 24-hour format), by selecting seconds display and actuating both slow and fast set inputs.

Blanking Control Input (pin 37): Connecting this Schmitt trigger input to VDD places all display drivers in a non-conducting, high-impedance state, thereby inhibiting the display. (See Figure 1.) Conversely, VSS applied to this input enables the display.

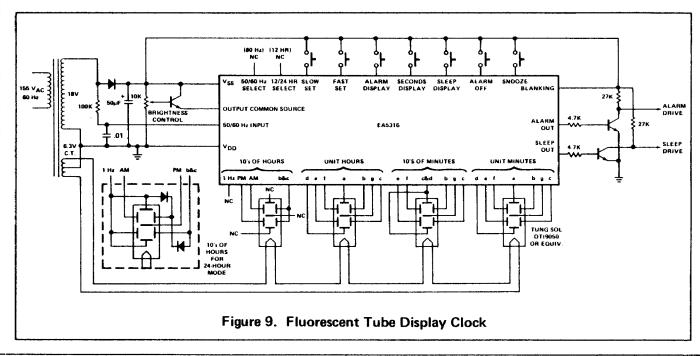

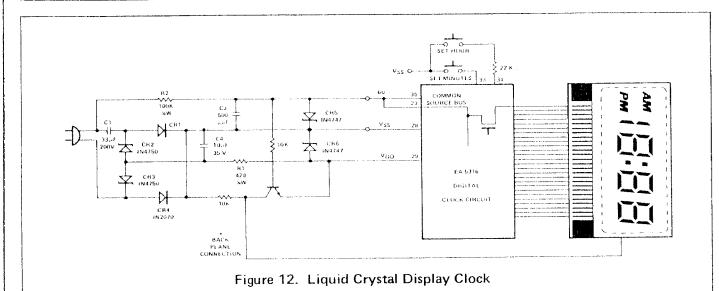

Output Common Source Connection (pin 23): All display output drivers are open-drain devices with all sources common to pin 23 (Figures 4, 5 and 6). When using fluorescent tube displays, VSS or a display brightness control voltage is permanently connected to this pin. Since the brightness of a fluorescent tube display is dependent on the anode (segment) voltage, applying a variable voltage to pin 23 results in a dis-

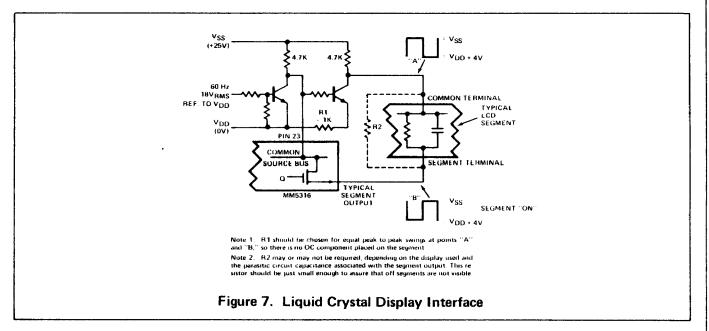

play brightness control. This control is shown in Figure 9. However, when using liquid crystal displays, the lifetime of the display device is optimized when AC drive voltages are provided. The common source connection of the EA 5316 output drivers facilitates generating AC drive voltages. An interface circuit for driving liquid crystal displays is shown in Figure 7.

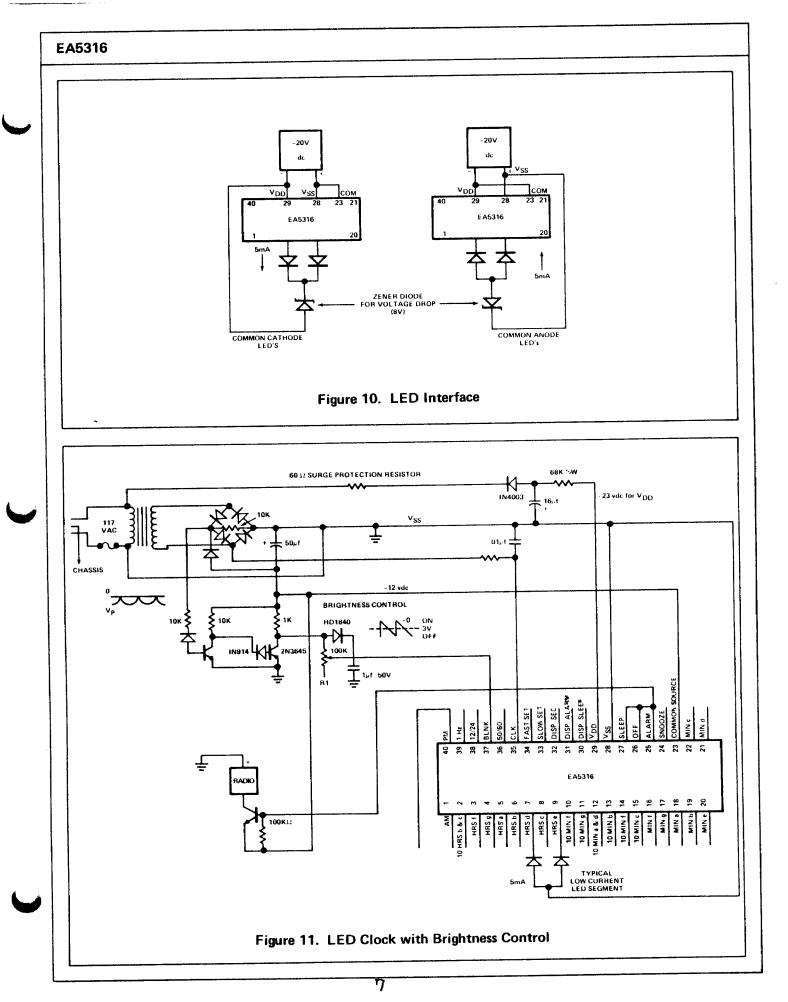

When using low current LED displays, the EA 5316 is connected as shown in Figure 10 to provide direct drive to the display. The 20V supply insures low output ON resistance. The zener diode provides a 12V drop across output drivers which limits internal power dissipation to less than 60 mW per driver.

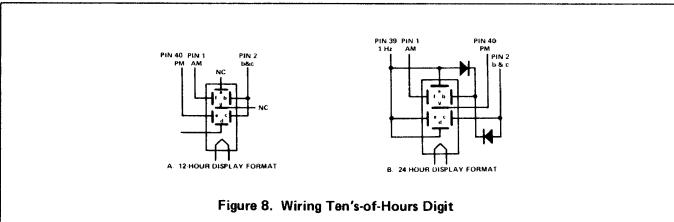

12 or 24 Hour Select Input (pin 38): By leaving this pin unconnected, the outputs for the most-significant display digit (10's of hours) are programmed to provide a 12-hour display format. An internal 150K $\Omega$  pull-down resistor is again provided. Connecting this pin to VSS programs the 24-hour display format. Also, the output connections (pins 1, 2, 39 and 40) are different for each format. Figure 8 illustrates these differences. In addition to displaying 10's of hours, this digit provides an A.M./P.M. indication (12-hour format only) and the power failure indication. In the 12-hour format, A.M. indication is provided by segment "f"; P.M. indication by segment "e." The power failure indication consists of a flashing of the A.M. or P.M. indicator at a 1 Hz rate. A fast or slow set input resets an internal power failure latch and returns the display to normal. In the 24-hour format, the power failure indication consists of flashing segments "c" and "f" for times less than 10 hours, and of a flashing segment "c" for times equal to or greater than 10 hours but less than 20 hours; and a flashing segment "g" for times equal to or greater than 20 hours.

Alarm Operation and Output (pin 25): The alarm comparator senses coincidence between the alarm counter (the alarm setting) and the time counters (real time). The comparator output is used to set a latch in the alarm and sleep circuits. The latch output enables the alarm output driver (Figure 3), the EA 5316 output that is used to control the external alarm sound generator. The alarm latch remains set for 59 minutes, during which the alarm will therefore sound if the latch output is not temporarily inhibited by another latch set by the snooze alarm input (pin 24) or reset by the alarm off input (pin 26). Note in Figure 3 that this and the sleep output are push-pull outputs that can supply 3.5 mA minimum of output current.

Snooze Alarm Input (pin 24): Momentarily connecting pin 24 to VSS inhibits the alarm output for between 8 and 9 minutes, after which the alarm will again be sounded. This input is pulled-down to VDD by an internal 150K $\Omega$  resistor. The snooze alarm feature may be repeatedly used during the 59 minutes in which the alarm latch remains set.

Alarm Off Input (pin 26): Momentarily connecting pin 26 to VSS resets the alarm latch and thereby silences the alarm. This input is also returned to VDD by an internal  $150 \text{K}\Omega$  resistor. The momentary alarm off input also readies the alarm latch for the next comparator output, and the alarm will automatically sound again in 24 hours (or at a new alarm setting). If it is desired to silence the alarm for a day or more, the alarm off input should remain at VSS.

Sleep Timer and Output (pin 27): The sleep output at pin 27 can be used to turn off a radio after a desired time interval of up to 59 minutes. The time interval is chosen by selecting the sleep display mode (Table 1) and setting the desired time interval (Table 2). This automatically results in a current-source output via pin 27, which can be used to turn on a radio (or other appliance). When the sleep counter, which

counts downwards, reaches 00 minutes, a latch is reset and the sleep output current drive is removed, thereby turning off the radio. This turn-off may also be manually controlled (at any time in the countdown) by momentary VSS connection to the snooze input (pin 24). The output circuitry is the same as the alarm output (Figure 3), which is push-pull in order to supply a minimum of 3.5 mA of output current.

Table 1. EA 5316 Display Modes

| *Selected Display Mode | Digit No. 1           | Digit No. 2 | Digit No. 3     | Digit No. 4 |

|------------------------|-----------------------|-------------|-----------------|-------------|

| Time Display           | 10's of Hours & AM/PM | Hours       | 10's of Minutes | Minutes     |

| Seconds Display        | Blanked               | Minutes     | 10's of Seconds | Seconds     |

| Alarm Display          | 10's of Hours & AM/PM | Hours       | 10's of Minutes | Minutes     |

| Sleep Display          | Blanked               | Blanked     | 10's of Minutes | Minutes     |

<sup>\*</sup>If more than one display mode input is applied, the display priorities are in the order of Sleep (overrides all others), Alarm, Seconds, Time (no other mode selected).

Table 2. EA 5316 Setting Control Functions

| Selected Display Mode | Control<br>Input | Control Function                                                      |  |  |

|-----------------------|------------------|-----------------------------------------------------------------------|--|--|

| *Time                 | Slow             | Minutes advance at 2 Hz rate.                                         |  |  |

|                       | Fast             | Minutes advance at 60 Hz rate.                                        |  |  |

|                       | Both             | Minutes advance at 60 Hz rate.                                        |  |  |

| Alarm                 | Slow             | Alarm minutes advance at 2 Hz rate.                                   |  |  |

|                       | Fast             | Alarm minutes advance at 60 Hz rate.                                  |  |  |

|                       | Both             | Alarm resets to 12:00 A.M. (12-hour format).                          |  |  |

|                       | Both             | Alarm resets to 00:00 (24-hour format).                               |  |  |

| Seconds               | Slow             | Input to entire time counter is inhibited (Hold).                     |  |  |

|                       | Fast             | Seconds and 10's of seconds reset to zero without a carry to minutes. |  |  |

| 1                     | Both             | Time resets to 12:00:00 A.M. (12-hour format).                        |  |  |

|                       | Both             | Time resets to 00:00:00 (24-hour format).                             |  |  |

| Sleep                 | Slow             | Subtracts count at 2 Hz.                                              |  |  |

|                       | Fast             | Subtracts count at 60 Hz.                                             |  |  |

|                       | Both             | Subtracts count at 60 Hz.                                             |  |  |

<sup>\*</sup>When setting time sleep, minutes will decrement at rate of time counter, until the sleep counter reaches 00 minutes (sleep counter will not recycle).

Figure 1. 50/60 Hz or Blanking Input Shaping Circuits

## EA5316

EA RESERVES THE RIGHT TO MAKE CHANGES IN THESE SPECIFICATIONS AT ANY TIME AND WITHOUT NOTICE

1-B-0975-10

Electronic Arrays, Inc., 550 East Middlefield Road, Mountain View, CA 94043, telephone (415) 964-4321, TWX 910-379-6985