# 13 Analog-to-Digital Converter (ADC)

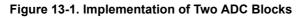

An analog-to-digital converter (ADC) is a peripheral that converts a continuous analog voltage to a discrete digital number. Two identical converter modules are included, which share 12 input channels.

The TM4C123GH6PM ADC module features 12-bit conversion resolution and supports 12 input channels, plus an internal temperature sensor. Each ADC module contains four programmable sequencers allowing the sampling of multiple analog input sources without controller intervention. Each sample sequencer provides flexible programming with fully configurable input source, trigger events, interrupt generation, and sequencer priority. In addition, the conversion value can optionally be diverted to a digital comparator module. Each ADC module provides eight digital comparators. Each digital comparator evaluates the ADC conversion value against its two user-defined values to determine the operational range of the signal. The trigger source for ADC0 and ADC1 may be independent or the two ADC modules may operate from the same trigger source and operate on the same or different inputs. A phase shifter can delay the start of sampling by a specified phase angle. When using both ADC modules, it is possible to configure the converters to start the conversions coincidentally or within a relative phase from each other, see "Sample Phase Control" on page 804.

The TM4C123GH6PM microcontroller provides two ADC modules with each having the following features:

- 12 shared analog input channels

- 12-bit precision ADC

- Single-ended and differential-input configurations

- On-chip internal temperature sensor

- Maximum sample rate of one million samples/second

- Optional phase shift in sample time programmable from 22.5° to 337.5°

- Four programmable sample conversion sequencers from one to eight entries long, with corresponding conversion result FIFOs

- Flexible trigger control

- Controller (software)

- Timers

- Analog Comparators

- PWM

- GPIO

- Hardware averaging of up to 64 samples

- Eight digital comparators

- Power and ground for the analog circuitry is separate from the digital power and ground

- Efficient transfers using Micro Direct Memory Access Controller (µDMA)

- Dedicated channel for each sample sequencer

- ADC module uses burst requests for DMA

### 13.1 Block Diagram

The TM4C123GH6PM microcontroller contains two identical Analog-to-Digital Converter modules. These two modules, ADC0 and ADC1, share the same 12 analog input channels. Each ADC module operates independently and can therefore execute different sample sequences, sample any of the analog input channels at any time, and generate different interrupts and triggers. Figure 13-1 on page 800 shows how the two modules are connected to analog inputs and the system bus.

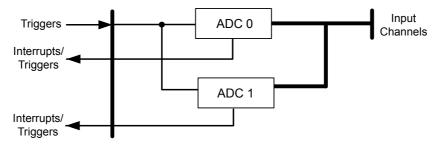

Figure 13-2 on page 801 provides details on the internal configuration of the ADC controls and data registers.

#### Figure 13-2. ADC Module Block Diagram

### 13.2 Signal Description

The following table lists the external signals of the ADC module and describes the function of each. The AINx signals are analog functions for some GPIO signals. The column in the table below titled "Pin Mux/Pin Assignment" lists the GPIO pin placement for the ADC signals. These signals are configured by clearing the corresponding DEN bit in the **GPIO Digital Enable (GPIODEN)** register and setting the corresponding AMSEL bit in the **GPIO Analog Mode Select (GPIOAMSEL)** register. For more information on configuring GPIOs, see "General-Purpose Input/Outputs (GPIOs)" on page 649.

#### Table 13-1. ADC Signals (64LQFP)

| Pin Name | Pin Number | Pin Mux / Pin<br>Assignment | Pin Type | Buffer Type <sup>a</sup> | Description                          |

|----------|------------|-----------------------------|----------|--------------------------|--------------------------------------|

| AINO     | 6          | PE3                         | I        | Analog                   | Analog-to-digital converter input 0. |

| AIN1     | 7          | PE2                         | ļ        | Analog                   | Analog-to-digital converter input 1. |

| AIN2     | 8          | PE1                         | I        | Analog                   | Analog-to-digital converter input 2. |

| AIN3     | 9          | PE0                         | I        | Analog                   | Analog-to-digital converter input 3. |

| AIN4     | 64         | PD3                         | I        | Analog                   | Analog-to-digital converter input 4. |

| AIN5     | 63         | PD2                         | I        | Analog                   | Analog-to-digital converter input 5. |

| AIN6     | 62         | PD1                         | I        | Analog                   | Analog-to-digital converter input 6. |

| AIN7     | 61         | PD0                         | I        | Analog                   | Analog-to-digital converter input 7. |

| AIN8     | 60         | PE5                         | I        | Analog                   | Analog-to-digital converter input 8. |

| Pin Name | Pin Number | Pin Mux / Pin<br>Assignment | Pin Type | Buffer Type <sup>a</sup> | Description                           |

|----------|------------|-----------------------------|----------|--------------------------|---------------------------------------|

| AIN9     | 59         | PE4                         | I        | Analog                   | Analog-to-digital converter input 9.  |

| AIN10    | 58         | PB4                         | I        | Analog                   | Analog-to-digital converter input 10. |

| AIN11    | 57         | PB5                         | I        | Analog                   | Analog-to-digital converter input 11. |

#### Table 13-1. ADC Signals (64LQFP) (continued)

a. The TTL designation indicates the pin has TTL-compatible voltage levels.

## **13.3** Functional Description

The TM4C123GH6PM ADC collects sample data by using a programmable sequence-based approach instead of the traditional single or double-sampling approaches found on many ADC modules. Each *sample sequence* is a fully programmed series of consecutive (back-to-back) samples, allowing the ADC to collect data from multiple input sources without having to be re-configured or serviced by the processor. The programming of each sample in the sample sequence includes parameters such as the input source and mode (differential versus single-ended input), interrupt generation on sample completion, and the indicator for the last sample in the sequence. In addition, the  $\mu$ DMA can be used to more efficiently move data from the sample sequencers without CPU intervention.

### 13.3.1 Sample Sequencers

The sampling control and data capture is handled by the sample sequencers. All of the sequencers are identical in implementation except for the number of samples that can be captured and the depth of the FIFO. Table 13-2 on page 802 shows the maximum number of samples that each sequencer can capture and its corresponding FIFO depth. Each sample that is captured is stored in the FIFO. In this implementation, each FIFO entry is a 32-bit word, with the lower 12 bits containing the conversion result.

| Sequencer | Number of Samples | Depth of FIFO |

|-----------|-------------------|---------------|

| SS3       | 1                 | 1             |

| SS2       | 4                 | 4             |

| SS1       | 4                 | 4             |

| SS0       | 8                 | 8             |

#### Table 13-2. Samples and FIFO Depth of Sequencers

For a given sample sequence, each sample is defined by bit fields in the ADC Sample Sequence Input Multiplexer Select (ADCSSMUXn) and ADC Sample Sequence Control (ADCSSCTLn) registers, where "n" corresponds to the sequence number. The ADCSSMUXn fields select the input pin, while the ADCSSCTLn fields contain the sample control bits corresponding to parameters such as temperature sensor selection, interrupt enable, end of sequence, and differential input mode. Sample sequencers are enabled by setting the respective ASENn bit in the ADC Active Sample Sequencer (ADCACTSS) register and should be configured before being enabled. Sampling is then initiated by setting the SSn bit in the ADC Processor Sample Sequence Initiate (ADCPSSI) register. In addition, sample sequences may be initiated on multiple ADC modules simultaneously using the GSYNC and SYNCWAIT bits in the ADCPSSI register during the configuration of each ADC module. For more information on using these bits, refer to page 845.

When configuring a sample sequence, multiple uses of the same input pin within the same sequence are allowed. In the **ADCSSCTLn** register, the IEn bits can be set for any combination of samples, allowing interrupts to be generated after every sample in the sequence if necessary. Also, the END