SEMICONDUCTORS

# SP8634 SP8635 SP8637

700/600/400MHz ÷ 10 (BCD OUTPUTS)

The SP8634/5 and 7 are ECL decade counters with TTL compatible BCD outputs. They require an AC coupled input of 600mV p-p and have an ECL 10K compatible inhibit input which inhibits the device when in the high state. Both ECL and TTL 'carry' outputs are provided and there is a TTL reset.

# **FEATURES**

- BCD Outputs TTL Compatible

- Reset Input TTL Compatible

- AC Coupled Input (Internal Bias)

- TTL and ECL Compatible Carry Outputs

- Clock Inhibit Input ECL Compatible

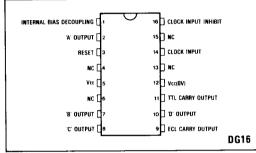

Fig.1 Pin connections - top view

#### QUICK REFERENCE DATA

Supply Voltage: 5.2V

Power Consumption: 400mW

■ Temperature Range: 0°C to +70°C

# **ABSOLUTE MAXIMUM RATINGS**

Supply voltage BCD outputs voltage Storage temperature range Max. junction temperature Max. clock I/P voltage -8V VEE +11V -55°C to +150°C +175°C 2.5V p-p **ORDERING INFORMATION**

SP8634 B DG SP8635 B DG SP8637 B DG

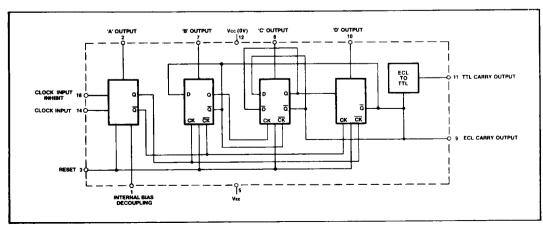

Fig.2 Functional diagram

# SP8634/5/7

#### **ELECTRICAL CHARACTERISTICS**

Supply Voltage:  $V_{CC} = 0V$   $V_{EE} = -5.2V \pm 0.25V$ Temperature: Tamb = 0°C to +70°C

| Characteristics                  | Symbol       | Value |       |       |         |                         |        |

|----------------------------------|--------------|-------|-------|-------|---------|-------------------------|--------|

|                                  |              | Min.  | Max.  | Units | Grade   | Conditions              | Notes  |

| Maximum frequency                | fmax         | 700   |       | MHz   | SP8634B | Input = 400-800mV       | )      |

| sinewave input                   |              | 600   |       | MHz   | SP8635B | 1 '                     | Note 5 |

|                                  |              | 400   |       | MHz   | SP8637B | l' '                    | []     |

| Minimum frequency                | <b>f</b> min |       | 40    | MHz   | All     | Input = 400-800mV       | Note 7 |

| sinewave input                   |              |       |       |       |         | p-p                     |        |

| Power supply current             | lee          |       | 90    | mA    | All     | V <sub>EE</sub> = -5.2V | Note 6 |

| Clock inhibit high               | VINH         | -0.96 |       | V     | All     | VEE = -5.2V (25°C)      | 110.00 |

| voltage                          |              | ļ     |       |       |         | ,                       |        |

| Clock inhibit low                | VINL         |       | -1.65 | V     | All     | VEE = -5.2V (25°C)      |        |

| voltage                          |              |       |       |       |         | (== = /                 |        |

| TTL output high voltage          | Von .        | 2.4   |       | V     | All     | 10kΩ from TTL           | Note 6 |

| (pin 2,7,8,10)                   |              |       |       |       |         | output too +5V          |        |

| TTL output low voltage           | Vol          |       | 0.4   | V     | All     | 10kΩ from TTL           | Note 6 |

| (pin 2,7,8,10)                   |              |       |       |       |         | output to +5V           |        |

| TTL output voltage (pin 11)      | Vон          | 2.4   |       | V     | All     | 5kΩ from TTL            | Note 6 |

|                                  |              |       |       |       |         | output to +5V           |        |

| TTL output low voltage (pin 11)  | Vol          |       | 0.4   | V     | All     | 5k Ω from TTL           | Note 6 |

| 1                                |              |       |       |       |         | output to +5V           |        |

| ECL output high voltage (pin 9)  | Vон          | -0.9  | -0.7  | V     | All     | VEE = -5.2V (25°C)      |        |

| ECL output low voltage (pin 9)   | Vol          | -1.8  | -1.5  | V     | All     | VEE = -5.2V (25°C)      |        |

| Edge speed for correct operation | te           |       | 2.5   | ns    | Ali     | 10% to 90%              | Note 7 |

| at maximum frequency             |              |       |       |       |         |                         |        |

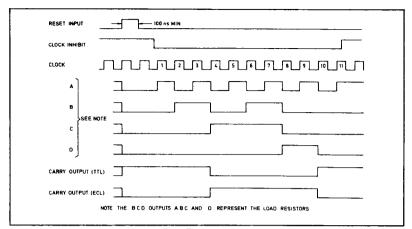

| Reset on time for correct        | ton          | 100   |       | ns    | All     |                         | Note 7 |

| operation                        |              |       |       |       |         |                         |        |

| Reset input high voltage         | VINH         | 2.4   |       | V     | All     |                         | Note 6 |

| Reset input low voltage          | VINL         |       | 0.5   | V     | Ali     |                         | Note 6 |

#### **NOTES**

- Unless otherwise stated the electrical characteristics are guaranteed over full specified supply, frequency and temperature range.

The temperature coefficient of Vo<sub>H</sub> (ECL) = +1.3mV/°C and Vo<sub>L</sub> = +0.5mV/°C but these are not tested.

The temperature coefficient of inhibit threshold voltage = +0.24mV/°C but this is not tested.

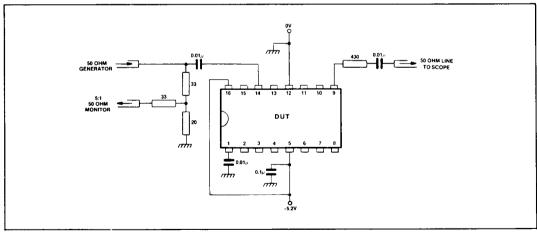

- The test configuration for dynamic testing is shown in Fig.5. Tested at 0°C and +70°C only.

Tested at +25°C only.

- 5.

- Guaranteed but not tested.

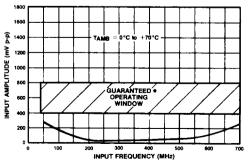

Fig.3 Typical input characteristics SP8634

\*Tested as specified in table of Electrical Characteristics

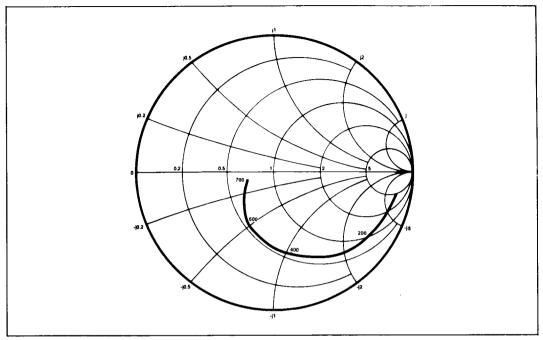

Fig.4 Typical input impedance. Test conditions: supply voltage 5.2V, ambient temperature 25°C. Frequencies in MHz, impedances normalised to 50 ohms.

Fig.5 SP8634/5/7 high frequency test circuit

### **OPERATING NOTES**

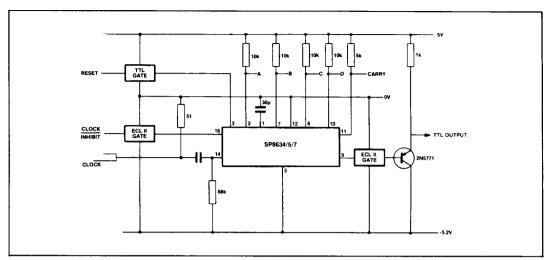

- The clock input (pin 14) should be capacitively coupled to the signal source. The input signal path is completed by connecting a capacitor from the internal bias decoupling, pin 1, to ground.

- In the absence of a signal the devices will self-oscillate. This can be prevented by connecting a 68k resistor between the clock input, pin 14, and the negative supply (pin 5).

- 3. The device will operate down to DC but the input slew rate must be better than 100V/us.

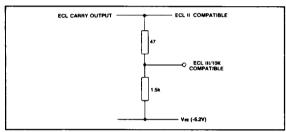

- 4. The Carry O/P is ECL II compatible but can be interfaced ECL III/10K by the inclusion of two resistors. See Fig. 7.

- 5. The clock inhibit is compatible with ECL III/10K

throughout the temperature range.

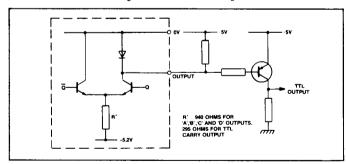

6. The output (pins 2, 7, 8, 10 and 11) are current sources and can be made TTL compatible by addition of 10k and 5k (pin 11) to +5V. See Fig.6. This gives a fan-out of 1. This can be increased by buffering the output with a PNP emitter follower. See Fig.8.

7. The device is clocked on the positive transition of the clock input on pin 14, provided that the clock inhibit input (pin 16) is in the low state. It is important to note that the positive transition of clock inhibit must occur while the clock is in the high state to avoid spurious counting.

Fig.6 Typical application configuration

Fig.7 ECL III/10K interfacing

Fig.8 TTL output buffering for increased fan-out

Fig.9 Timing diagram