# HA-4920/4925

### High Speed Quad Comparator

#### **FEATURES** DESCRIPTION FAST RESPONSE TIME HA-4920/4925 are monolithic, quad, high speed comparators offering LOW OFFSET VOLTAGE a combination of speed, precision, and flexibility never before available in a quad comparator. 40ns response time and 2.0mV offset voltage STANDARD POWER SUPPLIES makes these comparators ideally suited for precise signal level detection and fast response times to large and small input signal levels. These ACTIVE PULL-UP/PULL-DOWN OUTPUT dielectrically isolated devices employ unique input/output stages which CIRCUIT - NO EXTERNAL RESISTORS REQUIRED prevent troublesome ground coupling inherent in combined analog/ digital systems. TTL AND ECL COMPATIBLE The flexibility/speed of HA-4920/4925 assures easy application in fast **APPLICATIONS** data acquisition systems, analog to logic interface networks, and test equipment. A/D CONVERTERS THRESHOLD DETECTOR Both devices are available in 16 pin dual-in-line ceramic packages. The HA-4920 operates from -55°C to +125°C and the HA-4925 oper- ZERO-CROSSING DETECTOR ates over a 0°C to +75°C temperature range. LOGIC SYSTEM INTERFACES HIGH FREQUENCY OSCILLATORS PINOUT **SCHEMATIC** Package Code 4Z QUAD COMPARATOR POSITIVE R18 12.5K VLOGIC(+) Vincin(+) 11 10 LOGIC(-) VLOGIC(-) NEGATIVE **TOP VIEW**

2-98

#### ABSOLUTE MAXIMUM RATINGS (Note 1)

Voltage between V+ and V-

40V

Voltage between VLogic(+) and VLogic(-)

7V

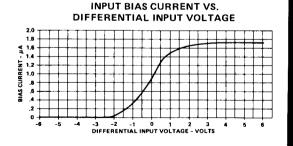

Differential Input Voltage Peak Ouput Current

±6V

Internal Power Dissipation (Note 2)

50mA

850mW

Storage Temperature Range

-65°C≤TA <150°C

Positive and Negative Voltage Clamp 5V below Supply Voltage

#### **ELECTRICAL CHARACTERISTICS**

V + = +15.0V

$V_{Logic}(+) = 5.0V$

V = -15.0V

VLogic(-) = GND

|                                   |       | HA-4920: -55°C/+125°C |     |     | HA-4925: 0°C/+75°C |     |      |       |

|-----------------------------------|-------|-----------------------|-----|-----|--------------------|-----|------|-------|

| PARAMETER                         | TEMP  | MIN                   | TYP | MAX | MIN                | TYP | MAX  | UNITS |

| Input Offset Voltage (Note 3)     | +25°C |                       | 2.0 | 3.0 | 7.4.4              | 4.0 | 6.0  | mV    |

|                                   | Full  | i                     |     | 4.0 |                    |     | 8.0  | mV    |

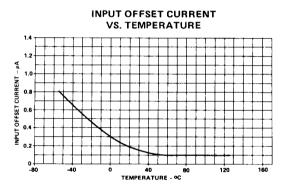

| Input Offset Current              | +25°C |                       | .5  | 1.5 |                    | 1.5 | 2.0  | μa    |

|                                   | Full  |                       |     | 2.0 |                    |     | 3.0  |       |

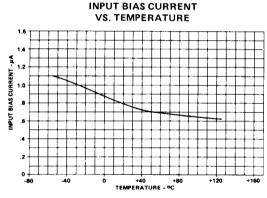

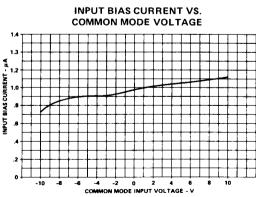

| Input Bias Current                | +25°C |                       | .8  | 6.0 |                    | 2.0 | 8.0  | μa    |

|                                   | Full  |                       |     | 8.0 |                    |     | 10.0 | μa    |

| Input Sensitivity (Note 4)        | Ful!  |                       | .4  | .6  |                    | .7  | .8   | mV    |

| Common Mode Range (CMR)           | Full  | ±10                   |     |     | ±10                |     |      | V     |

| Large Signal Voltage Gain         | +25°C |                       | 25K |     |                    | 25K |      | V/V   |

| Response Time Tpd0 (Note 5)       | +25°C |                       | 35  | 50  |                    | 35  | 50   | ns    |

| Response Time Tpd1 (Note 5)       | +25°C |                       | 30  | 50  |                    | 30  | 50   | ns    |

| Output Voltage Level (Note 6) VOL | Full  |                       | .15 | .4  |                    | .15 | .4   | V     |

| Output Voltage Level (Note 6) VOH | Full  | 3.5                   | 4.2 |     | 3.5                | 4.2 |      | V     |

| Output Current ISink (Note 7)     | Full  | 3.2                   |     |     | 3.2                |     |      | mA    |

| Output Current ISource (Note 7)   | Full  | 3.2                   |     |     | 3.2                |     |      | mA    |

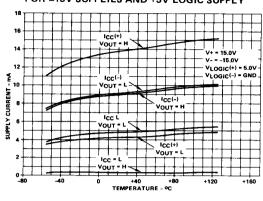

| Power Supply Current ICC+         | +25°C |                       | 14  | 20  |                    | 14  | 20   | mA    |

| Power Supply Current ICC-         | +25°C |                       | 10  | 20  |                    | 10  | 20   | mA    |

| Power Supply Current I Logic+     | +25°C |                       | 4.8 | 8.0 |                    | 4.8 | 8.0  | mA    |

#### NOTES:

- Absolute maximum ratings are limiting values, applied individually, beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied.

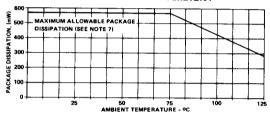

- 2. Derate by 5.8 mW/°C above +75°C.

- Minimum differential input voltage required to ensure a defined output state.

- R<sub>S</sub> ≤ 200 ohms; V<sub>in</sub> ≤ Common Mode Range. Input sensitivity is the worst case minimum differential input voltage required to guarantee a given output logic state, after offset voltage is nulled. This parameter includes

- the effects of offset current, common mode rejection, and voltage gain.

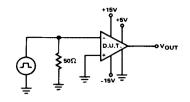

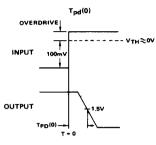

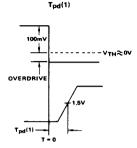

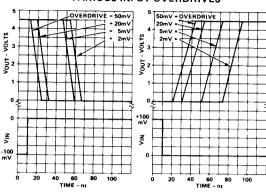

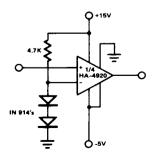

- 5. For Tpd(1); 100mV input step, -5mV overdrive. For T<sub>pd</sub>(0); -100mV input step, +5mV overdrive. Frequency ≈ 100Hz; Duty Cycle ≈ 50%; Inverting input driven. See Test Circuit below.

- 6. For  $V_{OH}$  and  $V_{OL}$ :  $I_{Sink} = 3.5 \text{mA}$ ,  $I_{Source} = 3.0 \text{mA}$ . For other values of VLogic; VOH (min.) = VLogic + -1.5V.

- 7. Per Comparator.

2-99

Input and output voltage waveforms for various input overdrives are shown on the following page.

#### **PERFORMANCE CURVES**

V+ = 15V, V- = -15V,  $V_{Logic}(+) = 5.0V$ ,  $V_{Logic}(-) = 0V$ ,  $T_A = +25^{\circ}C$ , Unless Otherwise Stated.

2-100

### SUPPLY CURRENT VS. TEMPERATURE FOR ±15V SUPPLIES AND +5V LOGIC SUPPLY

## RESPONSE TIME FOR VARIOUS INPUT OVERDRIVES

### MAXIMUM PACKAGE DISSIPATION VS. TAMBIENT

#### APPLYING THE HA-4920/25

- 1. SUPPLY CONNECTIONS: This device is exceptionally versatile in working with most available power supplies. The voltage applied to the V+ and V- terminals determines the allowable input signal range; while the voltage applied to the VI+ and VI- determines the output swing. In systems where dual analog supplies are available, these would be connected to V+ and V-, while the logic supply and return would be connected to VLogic+ and V<sub>Logic</sub>-. The analog and logic supply commons can be connected together at one point in the system. since the comparator is immune to noise on the logic supply ground. A negative output swing may be obtained by connecting VL+ to ground and VL- to a negative supply. Bipolar output swings (5V P-P, max.) may be obtained using dual supplies. Applied input signals should not exceed V<sub>Supply</sub> and the maximum differential input voltage values.

- UNUSED INPUTS: Inputs of unused comparator sections should be tied to a differential voltage source to prevent output "chatter". Differential voltage values should exceed the offset voltage plus input sensitivity voltage values for a particular device.

- 3. CROSSTALK: Simultaneous high frequency operation of all other channels in the package will not affect the output logic state of a given channel, provided that its differential input voltage is sufficient to define a given logic state ( $\Delta V_{IN} \geq \pm v_{OS}$ ). Low level or high impedance input lines should be shielded from other signal sources to reduce crosstalk and interference.

- POWER SUPPLY DECOUPLING: Decouple all power supply lines with .01 µF ceramic capacitors to a ground line located near the package to reduce coupling between channels or from external sources.

- 5. R.F.I.: High speed comparators may generate high frequency oscillations when the applied differential input voltage is less that the offset voltage plus input sensitivity value. This can be minimized by adding positive feedback hysteresis networks (see Harris App. Nate 505). Alternately, ferrite beads surrounding the input and output lines will help reduce RF interference to other circuitry.

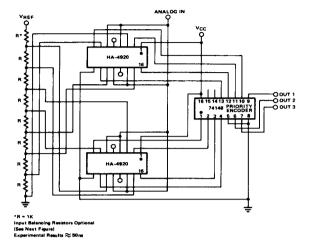

### 3 BIT PARALLEL COMPARATOR A/D CONVERTER USING TTL LOGIC

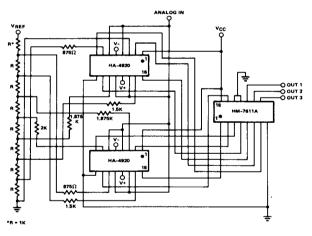

3 BIT PARALLEL COMPARATOR A/D CONVERTER USING 256 x 4 PROM

LOGIC LEVEL TRANSLATOR

TTL TO ECL

TRUTH TABLE FOR 3 BIT PARALLEL COMPARATOR A/D CONVERTER

| ENCODER/PROM INPUTS |   |   |   |   |   | O | OUTPUTS |   |   |  |

|---------------------|---|---|---|---|---|---|---------|---|---|--|

| 1                   | 2 | 3 | 4 | 5 | 6 | 7 | 0       | 1 | 2 |  |

| 0                   | 0 | 0 | 0 | 0 | 0 | 0 | 0       | 0 | 0 |  |

| 1                   | 0 | 0 | 0 | 0 | 0 | 0 | 1       | 0 | 0 |  |

| 1                   | 1 | 0 | 0 | 0 | 0 | 0 | 0       | 1 | 0 |  |

| 1                   | 1 | 1 | 0 | 0 | 0 | 0 | 1       | 1 | 0 |  |

| 1                   | 1 | 1 | 1 | 0 | 0 | 0 | 0       | 0 | 1 |  |

| 1                   | 1 | 1 | 1 | 1 | 0 | 0 | 1       | 0 | 1 |  |

| 1                   | 1 | 1 | 1 | 1 | 1 | 0 | 0       | 1 | 1 |  |

| 1                   | 1 | 1 | 1 | 1 | 1 | 1 | 1       | 1 | 1 |  |