# CESSO CENTRA CALENCE AND FRANCE A

# Add margining capability to a dc/dc converter

Brian Vasquez, Maxim Integrated Products, Dallas, TX

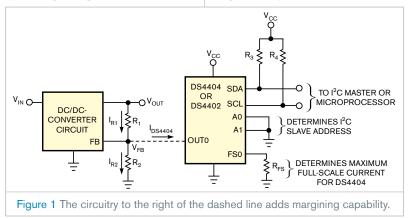

You can easily add margining capability—that is, the ability to digitally adjust the output voltage to a dc/dc converter by making a single connection to the circuit (**Figure 1**). The dashed line in the **figure** shows the connection. The extra IC is a twoor four-channel, I<sup>2</sup>C (inter-integratedcircuit)-adjustable-current DS4402 or DS4404 DAC. Because each DAC output is 0 mA at power-up, the extra circuitry is essentially transparent to the system until you write a command using the I<sup>2</sup>C bus.

For example, assume that the input voltage is 3 to 5.5V; the output voltage is 1.8V, which is the desired nominal output voltage; and the feedback voltage is 0.6V. You can obtain the feedback voltage from the dc/dc converter's data sheet; be sure to verify that it is within the output-voltage range that the current DAC's data sheet specifies as sinking or sourcing voltage depending on whether you are sinking or sourcing current. You should also verify the input impedance of the dc/dc

converter's feedback pin. The circuit in **Figure 1** assumes a high impedance.

Assume that you want to add a  $\pm 20\%$  margining capability to the dc/dc converter's output so that the maximum, nominal, and minimum output voltages would be 2.16, 1.8, and 1.44V, respectively. First, determine the necessary relationship between R<sub>1</sub> and R<sub>2</sub>, which yields the nominal output when the current of the DS4404 DAC is 0 mA:

$$V_{FB} = V_{OUTNOM} \left( \frac{R_2}{R_2 + R_1} \right), \quad (1)$$

where  $V_{FB}$  is the feedback voltage and  $V_{OUTNOM}$  is the nominal output voltage. Solving for  $R_1$ ,

$$R_1 = R_2 \left( \frac{V_{OUTNOM}}{V_{FB}} - 1 \right).$$

(2)

For this example,

$$R_1 = R_2 \left( \frac{1.8V}{0.6V} - 1 \right) = 2 \times R_2.$$

(3)

Summing the currents at the feedback node derives the current to make the output voltage increase to the maxi-

#### **DIs Inside**

56 A better approach to designing an RTD interface with a spreadsheet

58 Shunt regulator monitors battery voltage

60 Power supply meets automotive-transient-voltage specs

60 Locked-sync sine generator covers three decades with low distortion

What are your design problems and solutions? Publish them here and receive \$150! Send your Design Ideas to edndesignideas@ reedbusiness.com.

► To see all of *EDN*'s Design Ideas, visit www.edn.com/design ideas.

mum output voltage:

$$I_{R1} = I_{R2} + I_{DS4404},$$

(4)

where  $I_{R1}$  is the current through  $R_1$ ,  $I_{R2}$  is the current through  $R_2$ , and  $I_{DS4404}$  is the current into the DAC.

$$I_{DS4404} = I_{R1} - I_{R2}.$$

(5)

$\left(V_{OUTMAX} - V_{FB}\right)_{I}$   $\left(V_{FB}\right)_{(5)}$

$I_{R1} = \left(\frac{v_{OUTMAX} - v_{FB}}{R_1}\right); I_{R2} = \left(\frac{v_{FB}}{R_2}\right); (6)$

where  $V_{\text{OUTMAX}}$  is the maximum output voltage.

$$I_{DS4404} = \left(\frac{V_{OUTMAX} - V_{FB}}{R_1}\right) - \left(\frac{V_{FB}}{R_2}\right).$$

(7)

You can simplify **Equation 7** by solving **Equation 1** for  $R_2$  and then substituting, which yields:

$$I_{DS4404} = \frac{V_{OUTMAX} - V_{OUTNOM}}{R_1}.$$

(8)

In margin percentage, you can express **Equation 8** as:

### designideas

$$I_{DS4404} = \frac{V_{OUTNOM} \times MARGIN}{R_1}, \textbf{(9)}$$

where the margin is 0.2 to implement  $\pm 20\%$  margining in this case. Before you can use this relationship to calculate R<sub>1</sub> and R<sub>2</sub>, you must select the full-scale current.

According to the DS4404's data sheet, the full-scale current must be 0.5 to 2 mA to guarantee the specifications for accuracy and linearity. Unfortunately, no formula is available for calculating the ideal full-scale current. The desired number of steps, the step size, and the values for  $R_1$  and  $R_2$  influence that value. Another factor affecting the full-scale current value is whether there is a requirement that a particular register setting corresponds to a particular margin percentage.

In any case, your selection of a fullscale current will likely require several iterations, in which you select an arbitrary value within the range and then calculate  $R_1$ ,  $R_2$ ,  $R_{FS}$  (full-scale resistance), and step size. When you've determined an acceptable full-scale-current value, you may want to further adjust it or some of the resistor values to ensure that the resistor values you finally specify are commonly available.

To calculate  $R_1$  for the original example, make the full-scale current equal to the current of the DS4404. This step gives you 31 equal increments, or steps, from the nominal output voltage to the maximum output voltage, as well as 31 steps from the nominal output voltage to the mini-

mum output voltage. This resolution is more than adequate for this example.

You could, for instance, begin by arbitrarily choosing the full-scale current in the center, or 1.25 mA, of the specified range and then performing all the calculations. Instead, for illustrative purposes, the calculations are shown for the endpoints of the range: 0.5 and 2 mA. Analyzing the 0.5-mA case first, you perform the following calculations and then repeat for the 2-mA case.

Using **Equation 9** and solving for R<sub>1</sub> yields:

$$R_{1} = \frac{V_{OUTNOM} \times MARGIN}{I_{DS4404}} = (10)$$

$$\frac{1.8 \times 0.2}{0.5 \times 10^{-3}} = 720\Omega.$$

$$R_{2} = \frac{R_{1}}{2} = \frac{720}{2} = 360\Omega. \quad (11)$$

To calculate the full-scale resistance, use the formula and the reference voltage in the DS4404's data sheet:

$$R_{FS} = \frac{V_{REF}}{I_{FS}} \times \frac{31}{4} = \frac{1.23}{0.5 \times 10^{-3}} \times_{(12)}$$

$$\frac{31}{4} = 19,065\Omega \approx 19 \text{ k}\Omega.$$

$$STEP \text{ SIZE} = \frac{I_{FS}}{\text{NO. OF STEPS}} = \frac{0.5 \times 10^{-3}}{31} = 16.1 \text{ }\mu\text{A/STEP},$$

where  $R_{\rm FS}$  is the full-scale resistance,  $V_{\rm REF}$  is the reference voltage, and  $I_{\rm FS}$  is the full-scale current.

Finally, for completeness, you deter-

mine the DS4404's output current as a function of register setting:

I<sub>OUT</sub>(REGISTER SETTING)= (14)

#### STEP SIZE $\times$ REGISTER SETTING.

Note that this register setting does not include the sign bit, which selects sink or source. The DS4404 sinks current when the sign bit is zero, making the output voltage increase to the maximum output voltage. It sources current when the sign bit is one, making the output voltage decrease toward the minimum output voltage.

Now, you can repeat the calculations for the 2-mA case.

$$R_{1} = \frac{V_{OUTNOM} \times MARGIN}{I_{DS4404}} = \frac{1.8 \times 0.2}{2 \times 10^{-3}} = 180\Omega.$$

(15)

$$R_2 = \frac{R_1}{2} = \frac{180}{2} = 90\Omega.$$

(16)

$$R_{FS} = \frac{V_{REF}}{I_{FS}} \times \frac{31}{4} = \frac{1.23}{2 \times 10^{-3}} \times$$

$$\frac{31}{4} = 4766\Omega \approx 4.7 \text{ k}\Omega.$$

$$STEP \text{ SIZE} = \frac{I_{FS}}{\text{NO. OF STEPS}} =$$

$$\frac{2 \times 10^{-3}}{31} = 64.5 \text{ }\mu\text{A/STEP}.$$

(17)

Comparing  $R_1$  and  $R_2$  for the two cases—with a full-scale current of 0.5 or 2 mA—0.5 mA is the more attractive value because the resistances are higher.EDN

#### A better approach to designing an RTD interface with a spreadsheet

Aubrey Kagan, Emphatec, Markham, ON, Canada

An earlier Design Idea described how to linearize the output of an RTD (resistance-temperature-detector) sensor and how to calculate the resistor values using a spreadsheet (**Reference 1**). That idea limited the use of Microsoft (www.microsoft.com) Excel to calculating the coefficients you need for the polynomial expression and stopped short of using Excel to calculate the resistor values. You can generalize this proposed approach such that you can select any type of RTD and any temperature range, but this Design Idea limits the details to the following example.

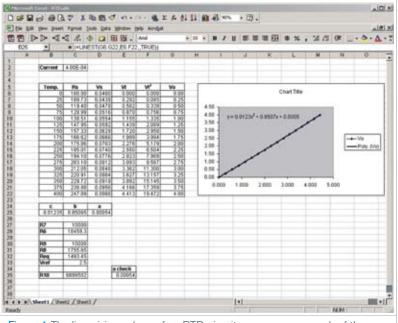

You can download the worksheet (Figure 1) from the Web version of

this Design Idea at www.edn.com/ 080918di1. You plot the chart as an XY diagram, and you create the trend line on the chart using a second-order polynomial, which will appear on the chart. The original Design Idea included this information. Unfortunately, you cannot access the coefficients you generate in this way from the worksheet, so you cannot directly calculate the resistor values.

To access the polynomial coefficients, you can use Excel's LINEST

## designideas

array formula. It prescribes a specific way of entering data; without that protocol, Excel will not provide the desired results. LINEST returns a number of regression statistics; to allow for these statistics, you must first highlight the range on the worksheet on which you want the regression results. Only the polynomial coefficients are important in this example, so this Design Idea limits the returned results by selecting block B24:D24 for those three values. You then enter the following line into the formula bar at the top of the worksheet:=LINEST(G5:G21,E5: F21,,TRUE).

Simultaneously press the Control, Shift, and Enter keys rather than just Enter to terminate this command. The coefficients will then drop into the selected range. Excel will add the braces, { }, to indicate the array formula. The input range of the function in the formula above includes the Vt<sup>2</sup> column, allowing LINEST to create a secondorder polynomial equation.

You can enter user-selected values as set numbers, providing easy and quick modification and an immediate update of the calculated values. These values include the current source through the RTD, the reference volt-

Figure 1 The linearizing values of an RTD circuit accompany a graph of the output voltage.

age, and the value of  $R_7$  and  $R_9$ , all of which are "named" cells that the formulas refer to. The idea rewrites the original formulas to isolate the desired variable. You will find each in the associated cells for  $R_6$ ,  $R_8$ , and  $R_{10}$  on the worksheet. You could also complete the model by creating an automatic look-up of standard resistor values (**Reference 2**).EDN

#### REFERENCES

■ Villanucci, Robert S, "Design an RTD interface with a spreadsheet," *EDN*, Feb 7, 2008, pg 57, www.edn. com/article/CA6526816.

Kagan, Aubrey, Excel by Example: A Microsoft Excel Cookbook for Electronics Engineers, Elsevier/Newnes, May 2004, ISBN 0750677562.

## Shunt regulator monitors battery voltage

Vladimir Rentyuk, Modul-98 Ltd, Zaporozhye, Ukraine

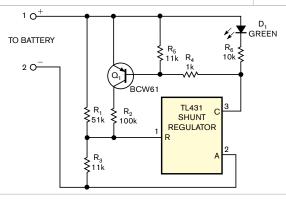

A TL431 shunt regulator is a perfect choice for many applications. You can use it as a comparator with hysteresis by taking advantage of its inner voltage reference along with few additional components. You can use this comparator with hysteresis, like a Schmitt trigger, as a simple battery monitor (Figure 1). You calculate the threshold voltage,  $V_{T+}$ , of this comparator as  $V_{T+}^{1+2} = V_{REF} \times (1 + R_1/R_3),$ where  $V_{REF}$  the internal

**Figure 1** A shunt regulator and associated circuitry function as a Schmitt trigger, lighting LED<sub>1</sub> when the battery is fully charged.

reference voltage of shunt-regulator TL431, is 2.5V.

When the battery voltage is higher than the threshold voltage, the cath-

ode voltage of the TL431 is at its low level of approximately 2V, and transistor Q<sub>1</sub> turns on, lighting LED<sub>1</sub>. You calculate the release voltage,  $V_{T-}$ , of the trigger as  $V_{T-} = V_{REF} \times (1 + R_1 \times R_2 / (R_1 + R_2) \times 1/R_3)$ .

When the battery voltage is less than the release voltage, the cathode voltage of the TL431 goes to its high level to the battery voltage. Transistor  $Q_1$  turns off, and LED<sub>1</sub> does not shine. LED<sub>1</sub> turns on again when the battery voltage, after recharging, exceeds the threshold voltage.EDN

## designideas

#### Power supply meets automotive-transient-voltage specs

Francesc Casanellas, Aiguafreda, Spain

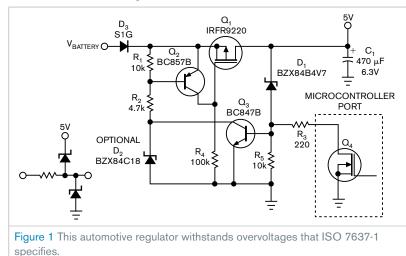

**Figure 1** shows a power supply that delivers 5V from a 12V battery. With only a few components, the supply copes with all the automotive transients that ISO (International Organization for Standardization) 7637-1 lists without the need for a bulky transient-voltage suppressor. In normal operation, R<sub>3</sub> connects to the common through a microcontroller port. In standby mode, R<sub>3</sub> stays open,

and the quiescent current of the supply decreases from approximately 2.8 mA to approximately 160  $\mu$ A, and the output voltage then drops to approximately 3.5V. If your application doesn't require a standby mode, suppress R<sub>3</sub> and set R<sub>5</sub> to 220 $\Omega$ . With most common zener diodes, you would then set R<sub>5</sub> to 120 $\Omega$  and D<sub>1</sub> to 4.3V. You can use the circuit in 24V systems if D<sub>2</sub> is 36V.

If the voltage increases, the current

through  $D_1$  and the base of  $Q_3$  increases, so  $Q_3$  increases the current of  $Q_2$ , which lowers the gate-to-source voltage of  $Q_1$ . If the input voltage surpasses 19V,  $D_2$  starts to conduct and makes  $Q_2$  switch off  $Q_1$ , so permanent overvoltages as high as 200V cannot damage the circuit. The Miller capacitance of  $Q_1$  makes it act as a fast integrator, which keeps the system stable. If you remove  $D_2$ , you must replace  $Q_3$  with a high-voltage transistor, such as an MMBTA42.

If you omit  $D_2$ , the circuit cannot withstand permanent overvoltages without  $Q_1$ 's overheating. In this case, however, the circuit can cope with all the impulses, including the load-dump pulse, of ISO 7637-1. You should remove  $D_2$  only if  $C_1$  cannot maintain the voltage during long overvoltages, such as the load-dump pulse, and keeping the voltage is critical.

An added advantage of this circuit over most IC-voltage regulators is that it can sink current through  $D_1$  and  $Q_3$ . This feature allows the use of diodes to fully protect the microprocessor's inputs. Soldering the D-Pack package to a couple of 1-cm<sup>2</sup> copper pads allows the circuit to source 300 mA at 10 to 16V or 150 mA at 20 to 32V. More dissipation area allows for higher currents.**EDN**

# Locked-sync sine generator covers

three decades with low distortion

Alfredo H Saab and Tina Alikahi, Maxim Integrated Products, Sunnyvale, CA

Analog applications, such as testing, calibration, and general system operation, often require a sine waveform of accurate amplitude and frequency, with low THD (total harmonic distortion). Some applications demand that the generator of such waveforms have the ability to accurately synchronize the output with an external timing signal. Simple sinewave generators can offer various degrees of this performance, but maintaining low THD with constant amplitude is a problem, particularly if the output and the synchronization signal must remain locked through an extended range of frequencies.

The circuit in **Figure 1** can synchronize a sine-wave output through three decades of frequency—20 Hz to 20 kHz—and maintain low THD and constant amplitude (**Table 1**). The synchronizer IC, an NXP Semiconductors (www.nxp.com) 74HC4046, is a PLL (phase-locked loop) with a VCO (voltage-controlled oscillator) and a phase/ frequency detector. It has three internal phase detectors, but this design uses the one with a frequency-capture range equal to that of the VCO-frequency range (the maximum frequency minus the minimum frequency).

The circuit's general-purpose binary frequency divider, the 74HC4060, connects between the VCO output and the 74HC4046 feedback (phase/ frequency-comparator) input and has a division ratio of 64. When the PLL is locked, therefore, the Q6 output of the 74HC4060 generates a square wave equal to 1/64th of the VCOoutput frequency. The components that determine the 74HC4046 center frequency,  $C_1$  and  $R_1$ , determine the VCO-frequency range from 20×64 to 20,000×64 from the minimum to the maximum level of the VCO's input-voltage range.

A switched-capacitor lowpass filter, the Maxim (www.maxim-ic.com) MAX297, whose cut-off frequency by design equals 1/50th of the clock frequency you apply to it, has for signal input the same square wave it uses for the PLL feedback, and its clock input attaches to the VCO output. Because the clock and signal inputs always have a frequency ratio of 64, the input signal always falls within the filter bandpass. No input harmonics fall within this bandpass because the ratio of the clock frequency to frequency is less than 50 for all of them. (For the lowest second

5V O-VCC ססע Q11 Q6 -0 0 COMPIN PHC 1 OUT SYNCHRONOUS Q12 Q5 -0 PHC 2 OUT 0 PULSE INPUT -0 0-Q13 Q4 -0 PHC 3 OUT SIG IN 5V 0\_\_\_\_ Q9 -0 -0 03 Π 220k 0-DEM OUT SINE-WAVE PH PULSE -0 0-Q8 C1A MAX297 OUTPUT 0-Q7 OU. 74HC4046 0 RTC C1B VCO IN  $C_2$ 74HC4060 1.5 μF FILM OP OUT OPIN 0-R2 СТС 0 RS R1 VCO OUT CLK R<sub>1</sub> 100 MR INH C<sub>3</sub> 1 μF R₃ 5.1k vss ş GND v GND  $C_4$ 1 u F COMMON

Figure 1 This three-IC sine-wave generator covers three frequency decades, provides low distortion, and allows you to synchronize it with an external signal.

harmonic, the ratio is 32.) The THD, up to the 32nd harmonic, is lower than 0.1%.

The fact that the filter's input signal is a square wave with a 50% duty cycle helps in this application because a square wave contains only odd harmonics of the fundamental, and the lowest-frequency harmonic is the third, which is well within the filter's deep-attenuation range.

You can frequency-modulate the synchronization signal, but that task entails a compromise between the synchronization-tracking speed (or maximum modulation frequency and depth) and the frequency-locking range, which the PLL's lowpass filter components,  $R_2$ ,  $R_3$ , and  $C_2$ , set. Modulation speed is limited for the values the **figure** shows because those values are optimized for an extended-frequency locking range. You can download more information, including a full data sheet for the MAX297, from www.maxim-ic.com (**Reference 1**).EDN

| TABLE 1 AMPLITUDE VERSUS FREQUENCY |                      |

|------------------------------------|----------------------|

| Frequency<br>(Hz)                  | Amplitude<br>(V rms) |

| 20                                 | 1.470                |

| 50                                 | 1.472                |

| 100                                | 1.472                |

| 200                                | 1.473                |

| 500                                | 1.473                |

| 1000                               | 1.473                |

| 2000                               | 1.472                |

| 5000                               | 1.473                |

| 10,000                             | 1.473                |

| 20,000                             | 1.472                |

#### REFERENCE

"MAX293/MAX294/MAX297 8th-Order, Lowpass, Elliptic, Switched-Capacitor Filters, Revision 2," June 2008, Maxim, http://datasheets.maxim-ic.com/en/ds/ MAX293-MAX297.pdf.