# **AVR302: Software TWI Slave Implementation**

### Features

- Interrupt Based

- Device Can Be Given any 7-bit Address (Expandable to 10-bit)

- Supports Normal and Fast Mode (400 kbps)

- Easy Insertion of "Wait States"

- Supports Wake-up from Idle Mode

- Code Size 160 Words (Maximum)

## Introduction

The need for a simple and cost effective inter-IC bus for use in consumer, telecommunications and industrial electronics, led to the developing of the TWI bus. Today the TWI bus is implemented in a large number of peripheral and microcontrollers, making it a good choice in low speed applications. The AT90S1200 does not have dedicated hardware for the TWI, but because of the high processing speed and flexible I/O ports, an effective software TWI slave implementation, can easily be done. The AT90S1200 is the only 8-bit MCU known to date that can perform fast (400 kbps) TWI slave operations in software.

# **Theory of Operation**

The TWI bus is a Two-wire synchronous serial interface consisting of one data (SDA) and one clock (SCL) line. By using open drain/collector outputs the TWI bus supports any fabrication process (CMOS, bipolar and more).

The TWI bus is a multi-master bus where one or more devices, capable of taking control of the bus, can be connected. Only Master devices can drive both the SCL and SDA lines while a Slave device is only allowed to issue data on the SDA line.

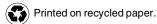

Figure 1. START and STOP Conditions

# Application Note

Rev. 0951B-AVR-05/02

Data transfer is always initiated by a Bus Master device. A **high** to **low** transition on the SDA line while SCL is high is defined to be a START condition (or a repeated start condition). A START condition is always followed by the (unique) 7-bit slave address and then by a Data Direction bit. The Slave device addressed now acknowledges to the Master by holding SDA low for one clock cycle. If the Master does not receives any acknowledge, the transfer is terminated. Depending of the Data Direction bit, the Master or Slave now transmits 8-bit of data on the SDA line. The receiving device then acknowledges the data. Multiple bytes can be transferred in one direction before a repeated START or a STOP condition is issued by the Master. The transfer is terminated when the Master issues a STOP condition. A STOP condition is defined by a **low** to **high** transition on the SDA line while the SCL is high.

If a Slave device cannot handle incoming data until it has performed some other function, it can hold SCL low to force the Master into a wait-state.

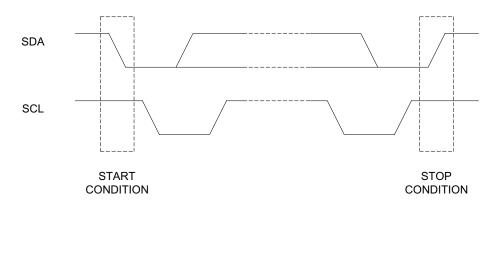

Figure 2. Bit Transfer on the TWI Bus

Change of <u>data</u> on the SDA line is only allowed during the low period of SCL as shown in Figure 2. This is a direct consequence of the definition of the START and STOP conditions. A more detailed description and timing specifications, can be found in [1].

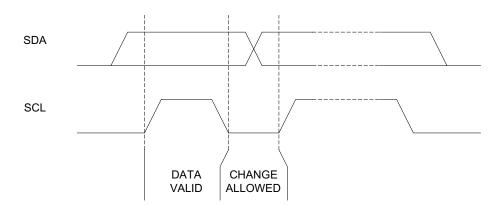

### Connection

Both TWI lines (SDA and SCL) are bi-directional, therefore outputs must be of an opendrain or an open-collector type. Each line must be connected to the supply voltage via a pull-up resistor. A line is then logic high when none of the connected devices drives the line, and logic low if one or more is drives the line low.

Figure 3 shows how to connect the Microcontroller to the TWI bus. The value of  $R_{\rm P}$  depends on  $V_{\rm DD}$  and the bus capacitance (typically 4.7 k). Since SDA is connected to INTO, a falling edge on the SDA will cause an interrupt when a START condition is detected.

### Implementation

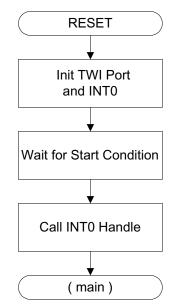

The implementation of the TWI Slave device presented in this application note is divided into two main parts. These are a special initialization sequence executed directly after a reset and the interrupt handling routine. Flow charts is shown in Figure 4 and Figure 5.

Figure 4. Initialization Flow Chart

The initialization routine "TWI\_init" (Figure 4) perform the necessary initialization of PORTD and External Interrupt 0. Note that the port initialization shown in the program code really has no effect since both DDRD and PORTD Registers are zero after Reset. However if other pins on port D needs to be initialized, this could be done here.

When initialization is done, the routine enters into a busy-loop which waits for the first START condition. This is done because a high to low transition on SDA not necessarily indicates a START condition if the bus is not free (no activity). Hence, both SDA and SCL must be monitored.

When a START condition is detected, a call to the interrupt service routine handles the first transfer and enables the interrupts.

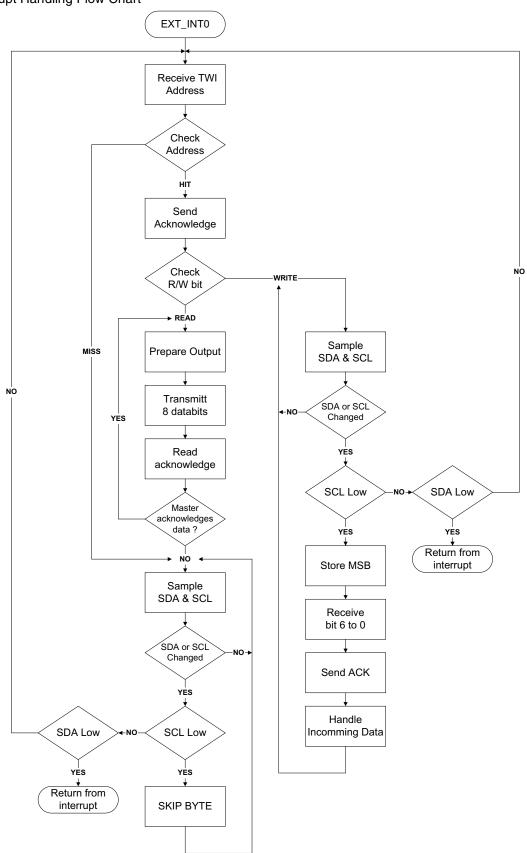

The interrupt handling routine (flow chart shown in Figure 5) is a combination of two routines "TWI\_wakeup" and "TWI\_skip". The combining of routines keeps the code size down.

"TWI\_wakeup" detects start condition (edge interrupt on EXT\_INT0) and handles the data transfer on the TWI bus. There are two important locations in this routine where the user can add own code. One part handles incoming data and the other handles outgoing data. In the program code these parts are commented with "INSERT USER CODE HERE". Received data or data to be send must be placed in the "TWIdata" Register.

"TWI\_skip" handles situations where data transfer on the TWI bus is not addressed to this device. Recall that if the bus is not free, both SDA and SCL must be monitored for a START (or STOP) condition. In this implementation Timer/Counter0 is used to count eight SCL clocks, i.e., one byte. By using the Timer/Counter0 Overflow Interrupt, processing time is freed while one byte is transferred. When Timer Overflow occurs, the "TWI\_skip" is called and a new condition test is done.

4

Figure 5. Interrupt Handling Flow Chart

# **Performance Figures**

| Parameter         | Value                                                                 |                   |

|-------------------|-----------------------------------------------------------------------|-------------------|

| Code Size         | 160 words                                                             |                   |

| Execution Cycles  | N/A                                                                   |                   |

| Register Usage    | <ul><li>Low Registers</li><li>High Registers</li><li>Global</li></ul> | :None<br>:5<br>:5 |

| Peripherals Usage | 2 I/O Pins, Timer/Counter0                                            |                   |

| Interrupt Usage   | Timer/Counter0 Overflow Interrupt<br>External Interrupt0              |                   |

# **Register Usage**

Only five registers are used in this implementation: "temp", "etemp", "TWIdata", "TWIadr", and "TWIstat". Both temporary registers are free to be used inside the interrupt user code.

| Register        | Description                                                                           |

|-----------------|---------------------------------------------------------------------------------------|

| r16 – "temp"    | Temporary Internal Register.                                                          |

| r17 – "etemp"   | Temporary Internal Register.                                                          |

| r18 – "TWIdata" | Contains current received or transmitted data. Only valid inside interrupt user code. |

| r19 – "TWladr"  | Contains current TWI address and direction bit. Do not use for other purposes.        |

| r20 – "TWIstat" | Temporary storage for SREG.                                                           |

6

### **Tips and Warnings**

The TWI routine presented can be reduced in size if the application guarantees that the bus is free (no activity) before initialization is done. As an example, this can be done by letting all masters wait approximately 20 ms after power up before accessing the TWI Bus. This will ensure a free bus and eliminates the need to sample both SCL and SDA while waiting for the first START condition. The initialization will then consist of interrupt enabling, only. This procedure gives a reduction of 12 instructions.

Another size reducing method is possible by replacing the interrupt handling routines with a polling routine. However this is <u>not</u> recommended due to the reduction of processing time for other duties.

Handling incoming and outgoing data is time critical. The user should insert wait-states if the code part which handles incoming or outgoing data is too time consuming (refer to program code for recommended sizes). For Normal mode TWI operation it's also possible to increase the crystal frequency.

Procedure for insertion of wait-states:

- 1. Right before the user code, force the SCL line low to initiate the wait-state.

- 2. Do the user code.

- 3. Finish the user code by releasing the SCL line.

Program code example (inside user code):

| sbi   | DDRD,DDD4 | ; force SCL low to initiate the-wait state | 2 |

|-------|-----------|--------------------------------------------|---|

| • • • |           | ; User data handling code                  |   |

| cbi   | DDRD,DDD4 | ; release SCL to remove the wait-state     |   |

### Conclusion

This application note shows how to implement the AT90S1200 as a multi purpose TWI peripheral device. Normal mode TWI transfer (100 kHz) is supported by using a 3 MHz or faster crystal or resonator, while Fast mode (400 kHz) only is supported for 16 MHz crystals. The use of interrupts to detect bus activity frees processing resources when the device is not accessed.

### **Atmel Headquarters**

*Corporate Headquarters* 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

### **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743 **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

e-mail

literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

ATMEL® and AVR® are the registered trademarks of Atmel.

Other terms and product names may be the trademarks of others.