# (11) **EP 2 833 568 A1**

(12)

### **EUROPEAN PATENT APPLICATION**

(43) Date of publication:

04.02.2015 Bulletin 2015/06

(51) Int Cl.:

H04B 10/40 (2013.01) H04B 10/50 (2013.01) H04B 10/25 (2013.01)

(21) Application number: 14152033.8

(22) Date of filing: 21.01.2014

(84) Designated Contracting States:

AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

Designated Extension States:

**BA ME**

(30) Priority: 01.08.2013 GB 201313788

(71) Applicant: Iconic Sound Limited London NW6 3BT (GB)

(72) Inventors:

Barnett, Danielle

Romford, Essex RM4 1LT (GB)

Holmes, David Romford, Essex RM4 1LT (GB)

Kellett, Michael Andrew Dalbeattie, DG5 4QQ (GB)

(74) Representative: Derry, Paul Stefan et al

Venner Shipley LLP 200 Aldersgate

London EC1A 4HD (GB)

# (54) Light Emission Circuit

(57) 1. Apparatus comprises:

first and second light sources driven respectively by second and third inverting amplifiers with feedback from the first and second light sources to provide signal content respectively on positive and negative phases of an input signal; and

a bias control arrangement configured to measure a bias level of one of the light sources and to bias the second and third amplifiers based on the measured bias level.

EP 2 833 568 A1

#### Field of the Invention

[0001] This invention relates to a light emission circuit.

1

#### Background to the Invention

[0002] In a concert or studio environment, it is usual to connect sound sources, including guitars and microphones, to amplification equipment with shielded electrical cables. Such cables have a copper core and a metallic shield separated by an insulating material. At each end, a jack or plug, typically 1/4 inch (6.35 mm) diameter, allows both the copper core and the shielding of the cable to be electrically connected to electronic circuitry in the relevant electrical equipment. Signals are carried from the sound source in the same form in which they are generated, i.e. as analogue signals in the audible frequency range 20Hz to 20 kHz. In a studio environment, the same type of cable connects sound sources to mixing desk equipment. Cables used in concert environments can be over 10m long, although shorter cables tend to be used in studio environments.

[0003] Such cables can become internally damaged during use, especially when being used in an on-stage environment, although they may appear externally to be undamaged. Damaged cables cause a reduction in the quality of signals being carried, and may result in unwanted distortion or other degradation of the audio signals. If the core of the cable becomes fractured, the cable can stop functioning altogether, although signal deterioration is more common. The inventor considers that signal degradation might result from fractures in the core and/or shielding and/or from damage to the insulating material separating the core from the shielding resulting in unwanted inductances and/or capacitances, which can cause unwanted resonance and/or filtering when supplied with energy in the form of the audio signals being carried.

**[0004]** The effects of cable damage can be avoided through the use of radio links between the sound source and the mixing desk or amplification equipment. Radio microphones are well known. However, the possibility of radio interference means that digital communication links are more reliable. However, many musicians and sound producers prefer audio signals not to be digitised at any point in their transmission on the basis that this results in a reduction in quality, as well as a less pure sound. WO2007/031794 discloses arrangements that mitigate these disadvantages. The present invention builds upon the arrangements disclosed in WO2007/031794.

# **Summary of the Invention**

**[0005]** A first aspect of the invention provides apparatus comprising:

first and second light sources (LED1, LED2);

a first transistor (Q1) having first and second main electrodes and a control electrode;

a second transistor (Q2) having first and second main electrodes and a control electrode;

a first amplifier (U1) having first and second inputs and an output;

a second amplifier (U2) having an input and an output;

a third amplifier (U3) having an input and an output;

a bias control arrangement having an input and an output:

#### 15 wherein:

20

35

40

45

the first light source (LED1) and the first and second main electrodes of the first transistor (Q1) are connected in series in a path between a positive supply terminal and a first node,

the second light source (LED2) and the first and second main electrodes of the second transistor (Q2) are connected in series in a path between the first node and a negative supply terminal,

the first node is connected to a second input of the first amplifier (U1),

the input of the second amplifier is connected to the output of the first amplifier,

the output of the second amplifier is connected to the control input of the first amplifier,

the input of the third amplifier is connected to the output of the first amplifier,

the output of the third amplifier is connected to the control input of the second transistor,

the input of the first amplifier is connected to a signal input terminal (INPUT),

the input of the bias control arrangement is connected to a second node in the path through the first and second light sources and the first and second transistors.

the bias control arrangement is configured to measure bias at its input and provide a control bias signal at its output, and

the output of the bias control arrangement is connected to the input of each of the second and third amplifiers.

[0006] The output of the bias control arrangement may be connected to the input of each of the second and third amplifiers via an arrangement comprising a fourth amplifier (U4) and a buffer (U5). Here, the output of the bias control arrangement may be connected to an input of the buffer (U5), wherein an output of the buffer may be connected to the input of the third amplifier (U3) and to an input of the fourth amplifier (U4), and wherein an output of the fourth amplifier (U4) may be connected to the input of the second amplifier (U2).

[0007] The apparatus may comprise a first resistor

15

20

25

30

40

50

connected directly to the first node and in the path to the positive supply terminal and a second resistor connected directly to the first node and in the path to the negative supply terminal, and wherein the second node may be connected to the first node by either the first resistor or the second resistor.

[0008] The bias control arrangement may include a microprocessor. The microprocessor may be configured to monitor signals received at the signal input terminal and is configured automatically to power down in response to detecting no significant input signal for a period of time. [0009] The bias control arrangement may have a second input that is connected to the input of the first amplifier, and the bias control arrangement may be configured to calculate the bias control signal based on instances when the level of the signal at the second input is low and to refrain from calculating the bias control signal based on instances when the level of the signal at the second input is not low.

**[0010]** The bias control arrangement may be configured to provide at its output a pulse width modulated signal having a duty cycle that is a function of the measured bias

**[0011]** A second aspect of the invention provides apparatus comprising:

first and second light sources driven respectively by second and third inverting amplifiers with feedback from the first and second light sources to provide signal content respectively on positive and negative phases of an input signal; and

a bias control arrangement configured to measure a bias level of one of the light sources and to bias the second and third amplifiers based on the measured bias level.

**[0012]** The output of the bias control arrangement may be connected to the second and third amplifiers via an arrangement comprising a fourth amplifier and a buffer. Here, the output of the bias control arrangement may be connected to an input of the buffer, an output of the buffer may be connected to the input of the third amplifier and to an input of the fourth amplifier, and an output of the fourth amplifier may be connected to the input of the second amplifier.

**[0013]** The bias control arrangement may include a microprocessor. The microprocessor may be configured to monitor the input signal terminal and is configured automatically to power down in response to detecting no significant input signal for a period of time.

**[0014]** The bias control arrangement may be configured to calculate a bias control signal provided to the second and third amplifiers based on instances when the level of the input signal is low and to refrain from calculating the bias control signal based on instances when the level of the input signal is not low.

**[0015]** The bias control arrangement may be configured to provide to the second and third amplifiers a pulse

width modulated signal having a duty cycle that is a function of the measured bias.

**[0016]** The apparatus may comprise an electrical connector, for instance a jack plug, for receiving an electrical input signal.

**[0017]** A third aspect provides a cable arrangement comprising first and second devices connected by a dual core optical waveguide, wherein the first device comprises such apparatus.

### **Brief Description of the Drawings**

**[0018]** Embodiments of the invention will now be described by way of example only with reference to the accompanying drawings, in which:

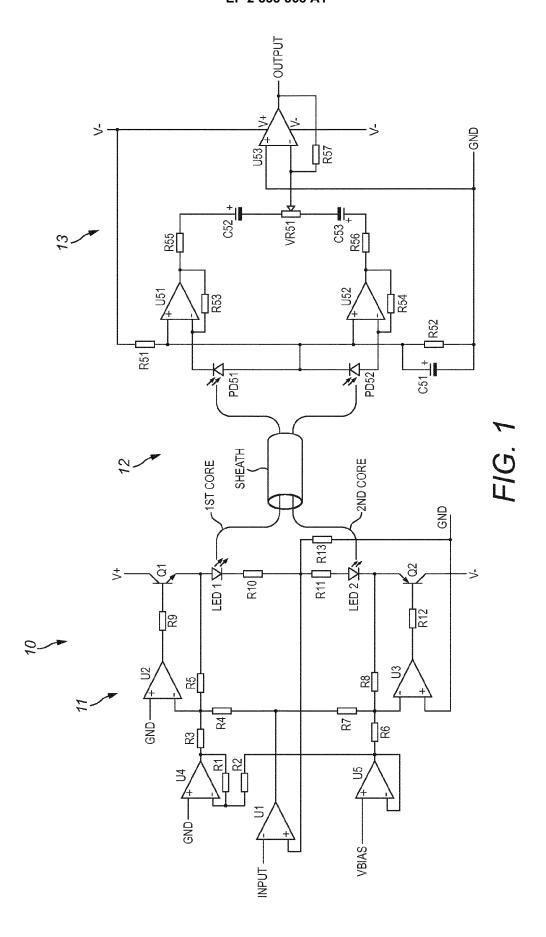

Figure 1 is a schematic drawing of circuitry used to communicate electrical audio signals in optical form, according to certain aspects of the invention;

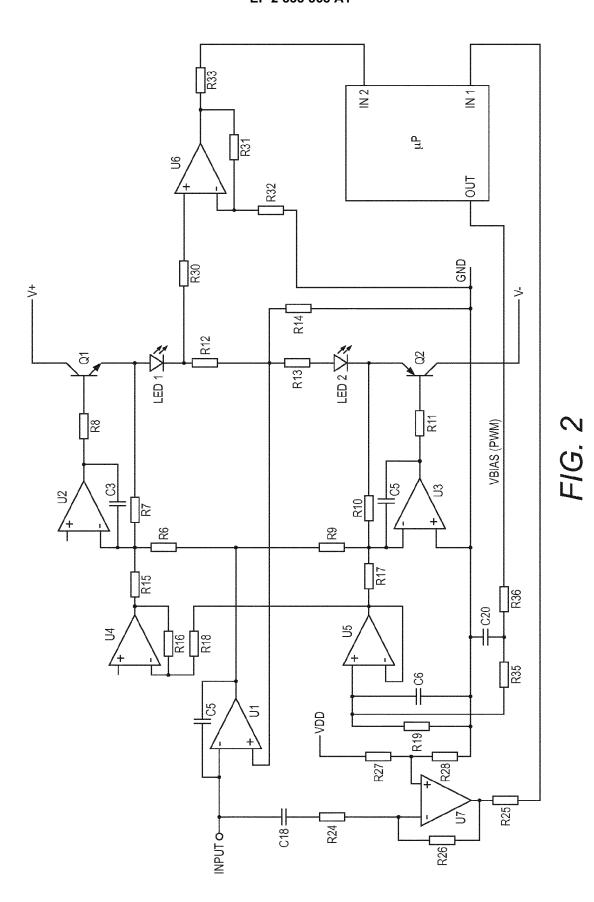

Figure 2 is a schematic drawing of transmitter circuitry of Figure 1, according to certain aspects of the invention;

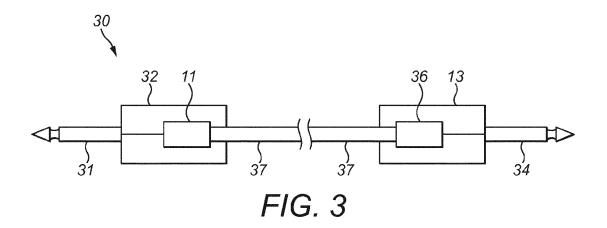

Figure 3 is a schematic drawing of an audio signal communication cable embodying the invention;

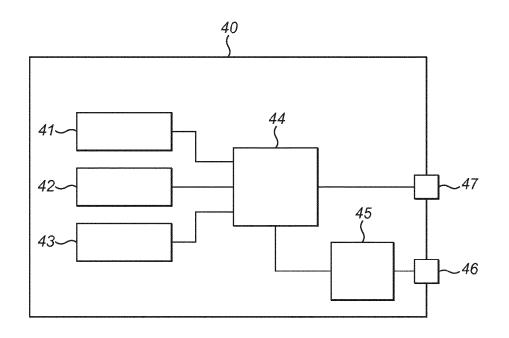

Figure 4 is a schematic drawing of a guitar including the Figure 2 circuitry and embodying the invention; and

Figure 5 is a schematic drawing of a microphone including the Figure 2 circuitry and embodying the invention.

#### **Detailed Description of Embodiments**

**[0019]** Reference will firstly be made to Figure 1, which is a schematic diagram illustrating components of a system 10. The system includes a transmitter 11, an optical cable 12 and a receiver 13.

**[0020]** In brief, the transmitter circuit 11 is arranged to receive electrical signals at audio frequencies, to provide an amplitude modulated optical signal over first and second cores of an optical cable 12, and the receiver 13 is arranged to demodulate the optical signals and to reproduce the original electrical signal. This specification is concerned primarily with the transmitter circuit 11.

<sup>45</sup> **[0021]** Firstly, the arrangement of components within the transmitter circuit 11 will be described.

**[0022]** The transmitter circuit 11 includes first to fifth operational amplifiers (op-amps) U1 to U5. Each of the op-amps has an inverting input, a non-inverting input and an output.

[0023] The first op-amp U1 is an input amplifier, and acts as a buffer. The input amplifier U1 is connected to receive an input electrical signal supplied at an INPUT terminal at its inverting input. The non-inverting input of the first op-amp U1 is connected to a node in a chain between positive and supply negative terminals, as is described in more detail below. Although not shown, buffering and filtering components are provided to process

30

40

45

50

55

a received signal before application to the INPUT terminal

[0024] The chain includes, in sequence from the positive supply terminal: collector and emitter electrodes of a first transistor Q1, anode and cathode terminals of a first light source LED1, a tenth resistor R10, an eleventh resistor R11, a second light source LED2 and collector and emitter electrodes of a second transistor Q2. The first transistor Q1 is an NPN transistor, and the second transistor Q2 is a PNP transistor. The non-inverting input of the first amplifier U1 is connected at the node between the tenth and eleventh resistors R10, R11. This node is also connected to ground potential by a thirteenth resistor R13. The light sources here are light emitting diodes.

[0025] The base electrode of the first transistor Q1 is connected to an output of the second op-amp U2 by a ninth resistor R9. Similarly, the base electrode of the second transistor Q2 is connected to the output of the third op-amp U3 by a twelfth resistor R12. The non-inverting inputs of the second and third op-amps U2 and U3 are connected to ground potential GND. The inverting input of the second op-amp U2 is connected to the output of the first op-amp U1 by a fourth resistor R4. The inverting input of the third op-amp U3 is connected to the output of the first op-amp U1 by a seventh resistor R7. The inverting input of the second op-amp U2 is also connected to the node between the first transistor Q1 and the first light source LED1 by a fifth resistor R5. The inverting input of the third op-amp U3 is connected to the node between the second light source LED2 and the second transistor Q2 by an eighth resistor R8.

**[0026]** A biasing arrangement is provided by the fourth and fifth op-amps U4 and U5.

[0027] The output of the fifth op-amp U5 is connected to the inverting input of the third op-amp U3 by a sixth resistor R6. The inverting input of the fifth op-amp U5 is connected directly to the output of the fifth op-amp, and is connected to the inverting input of the fourth op-amp U4 by a second resistor R2. The first resistor R1 is connected between the output and inverting INPUT terminals of the fourth op-amp U4. The output of the fourth op-amp U4 is also connected to the inverting input of the second op-amp U2 by a third resistor R3. The non-inverting input of the fourth op-amp U4 is connected to ground potential. The non-inverting input of the fifth op-amp U5 is connected to receive a bias Voltage signal VBIAS.

**[0028]** The first and second cores of the optical fibre cable arrangement 12 are connected to respective ones of the first and second light sources LED1 and LED2. The first and second cores are contained within a sheath, which is indicated schematically in the figure. At the receiver 13, the first core of the optical fibre 12 is connected to a first photodiode PD51 and the second core is connected to a second photodiode PD52.

**[0029]** The output signal from the first photodiode PD51 is amplified by a first receiver op-amp U51. A second receiver op-amp U52 is provided to amplify the signal provided by the second photodiode PD52. Outputs of the

first and second receiver op-amps U51 and U52 are summed at a potentiometer VR51, and the result is amplified by a third receiver op-amp U53.

[0030] In the transmitter circuit 11, the first and second resistors R1 and R2 may have the same value. Also, each of the third to eighth resistors R3 to R8 may have the same value as one another. The ninth and twelfth resistors R9 and R12 may have the same value, which may for instance be  $100\Omega$ . The tenth and eleventh resistors R10, R11 may have the same value, which may for instance be  $10\Omega$ . The thirteenth resistor R13 may also have a value of  $10\Omega$ .

[0031] Operation of the transmitter circuit 11 will now be described.

[0032] In brief, the second and third op-amps U2 and U3 drive the first and second light sources LED1 and LED2 respectively. The light sources are driven based on the input signal received at the inverting input of the first op-amp U1. The second op-amp U2 drives the first light source1 to provide illumination at a level that is directly proportional to the input Voltage for one half of the waveform of the input Voltage, and the third op-amp U3 drives the second light source LED2 to provide an illumination at a level proportional to the Voltage of the input signal for the other half of the waveform. It can be visualised that the first light source LED1 provides the positive part of the input signal and the second light source LED2 provides the negative part of the input signal. When the input signal is negative, the first light source LED1 provides substantially no signal content, and when the input signal is positive, the second light source LED2 provides substantially no signal content.

**[0033]** Assuming that the value of a VBIAS applied to the non-inverting input of the fifth op-amp U5 is zero Volts, the outputs of the fourth and fifth op-amps U4 and U5 are also o. When the input signal has a positive value, the output of the first op-amp U1 becomes more negative, which in turn causes the outputs of the second and third op-amps U2 and U3 to become more positive. This causes the current flowing in the first light source LED1 to increase and the current flowing in the second light source LED2 to decrease.

**[0034]** In turn, this causes the current flowing through the collector-emitter path of the first transistor Q1 through the tenth resistor R10 and into the thirteenth resistor R13 to increase. This causes a positive Voltage to appear across the thirteenth resistor R13.

[0035] The action of the feedback connection from the thirteenth resistor R13 to the non-inverting input of the first op-amp U1 results in the Voltage across the thirteenth resistor R13 following the input Voltage at the inverting input of the first op-amp U1. Since the Voltage across the thirteenth R13 is proportional to the current flowing though it and thus through the conducting one of the first and second light sources LED1, LED2 the current through the conducting light source LED1 or LED2 is caused to be proportional to the Voltage at the input of the first op-amp U1. As such, this arrangement provides

25

40

45

50

a feedback signal to the first op-amp U1 that is proportional to the current in the light sources LED1 and LED2. **[0036]** When the input signal is negative, a similar process results in current flowing through the first resistor R1, the second light source LED2 and the second resistor Q2, resulting in a negative Voltage across the thirteenth resistor R13.

[0037] With a value of VBIAS at zero Volts, the crossing of the signal supplied at the INPUT terminal from positive to negative or from negative to positive would require the output of the second and third op-amps U2 and U3 to make large steps for the respective light source LED1 or LED2 to start conduction.

[0038] Disregarding the effects of errors and offsets in the op-amps and assuming zero bias provided by the fourth and fifth op-amps U4 and U5, the output of the first op-amp U1 is zero if its input is zero, and the outputs of the second and third op-amps are also o. In this condition, the first and second transistors Q1 and Q2 are turned off, that is they are non-conducting, and there is no current in either of the light sources LED1 and LED2 and there is a zero Voltage across the thirteenth resistor R13. If even a very small input Voltage is applied at the input, the feedback loop requires that one of the transistors Q1 and Q2 be turned on to drive current through one of the light sources LED1 or LED2. This requires a Voltage of about +/- 2 Volts at the output of the second or third opamp U2 or U3 according to the polarity of the input. Typically, with real components, the outputs of the second and third op-amps U2 and U3 need only to change by a further 0.5 Volts to 0.7 Volts for the maximum signal that the transmitter circuit 11 can handle.

**[0039]** The need for the provision of large steps in Voltage by the second and third op-amps U2 and U3 is avoided by the biasing arrangement shown in Figure 1 and shown in more detail in Figure 2.

[0040] In particular, a bias current for the first and second light sources LED1 and LED2 is generated by the biasing circuit formed by the fourth and fifth op-amps U4 and U5. In particular, a Voltage approximately equal to the forward Voltage of the light sources LED1 and LED2 is applied to the VBIAS input, which is the non-inverting input of the fifth op-amp U5. This causes the output of the fifth op-amp U5 to be equal to the Voltage of VBIAS and causes the output of the fourth op-amp U4 to be equal to the negative Voltage, i.e. -VBIAS.

[0041] Acting through the third and sixth resistors R3 and R6, the signals on the outputs of the fourth and fifth op-amps U4 and U5 cause the third op-amp U3 to drive the base of the second transistor Q2 negative until the Voltage on the cathode of the second light source LED2 is -VBIAS and cause the output of the second op-amp U2 to be driven positive until the Voltage on the anode of the first light source LED1 is equal to VBIAS.

**[0042]** The use of two light sources driven by two different amplifiers to generate signals on different phases of the input signal results in a doubling of the dynamic range, compared to the situation where a single light

source is used. This advantage is achieved at the expense of an additional core required for the optical cable 12. However, this is considered to be an acceptable downside considering the performance advantages that result from the increased dynamic range.

**[0043]** The present embodiment provides a Voltage adjustment arrangement by which it is possible to adjust the current flowing through the light sources LED1 and LED2 in the absence of a signal at the input to a value that is suitable to reduce non-linearity whilst not consuming excessive power.

**[0044]** Through the use of a bias Voltage adjustment arrangement, differences in forward Voltage for different light sources, resulting from different temperatures of operation and also from manufacturing tolerances, can be accommodated.

**[0045]** In the embodiments described herein, this is achieved by measuring the bias current that flows through the light sources LED1 and LED2 and by adjusting the Voltage of the signal at VBIAS to maintain the bias current at the required level.

**[0046]** Moreover, the bias Voltage adjustment arrangement biases two separate amplifiers U2 and U3, and their associated light sources LED1 and LED2, in a balanced fashion using only one input VBIAS.

**[0047]** Figure 2 shows the transmitter circuit arrangement 11 in more detail. Reference numerals are re-used from Figure for like elements. The additional elements that are shown in Figure 2 but are not shown in Figure 1 will now be described.

[0048] The main additional component is a microprocessor  $\mu P$ . The microprocessor  $\mu P$  is configured to measure the bias current flowing through the light sources and to provide a Voltage at VBIAS that is appropriate to achieve the required bias current level.

[0049] The microprocessor  $\mu P$  has two analogue inputs In1 and In2. The first input In1 is connected to sample the signal at the INPUT terminal. The second input In2 of the microprocessor  $\mu P$  is connected to sample the Voltage at a node in the chain including the first and second light sources LED1 and LED2.

[0050] In particular, the INPUT terminal is connected to an inverting input of a seventh op-amp U7 via an eighteenth capacitor C18 and a twenty-fourth resistor R24. The output of the seventh op-amp U7 is connected to the first input In1 of the microprocessor  $\mu P$  by a twenty-fifth resistor R25. A twenty-sixth resistor R26 is connected between the inverting input and output terminals of the seventh op-amp U7. The non-inverting input of the seventh op-amp U7 is connected to the mid-point of a potential divider formed by twenty-seventh and twenty-eighth resistors R27 and R28 connected between a second supply potential VDD and ground potential GND.

**[0051]** The node between the cathode of the first light source LED1 and the twelfth resistor R12 is connected to the non-inverting input of a sixth op-amp U6 by a thirtieth resistor R30. The inverting input of the sixth op-amp U6 is connected to ground potential GND by a thirty-sec-

20

25

30

40

45

50

ond resistor R32. A thirty-first resistor R31 is connected between the output and inverting INPUT terminals of the op-amp U6. The output of the sixth op-amp U6 is connected to the second input In2 of the microprocessor  $\mu P$  by a thirty-third resistor R33.

[0052] An output Out of the microprocessor  $\mu P$  is connected to the non-inverting input of the fifth op-amp U5 as VBIAS. The output Out of the microprocessor  $\mu P$  is an analogue output. The output Out of the microprocessor  $\mu P$  is connected in particular by an RC circuit comprised of three resistors R19, R35 and R36 and two capacitors C6 and C20. The RC circuit does not include any series capacitors, which would block DC, but includes a capacitor connected to ground potential GND. [0053] Also, capacitors are connected across the outputs and inverting inputs of the second and third op-amps U2 and U3. These capacitors control the bandwidth of the amplifiers provided by the second and third op-amps U2 and U3.

[0054] A signal of maximum amplitude approximately 1.2 Volts peak to peak is presented at the INPUT terminal. Because the twelfth, thirteenth and fourteenth resistors R12 to R14 are all  $10\Omega$  resistors, the maximum peak current through the first and second light sources LED1 and LED2 is about 60mA.

[0055] The microprocessor  $\mu P$  is configured to adjust the bias Voltage applied to the non-inverting input of the fifth op-amp U5 by measuring the bias current as follows. [0056] The bias current flowing through the light sources LED1 and LED2 results in a Voltage across the twelfth resistor R12. In the absence of any Voltage on the INPUT terminal, the feedback loop from the node between the twelfth and thirteenth resistors R12 and R13 to the noninverting input of the first op-amp U1 ensures that the Voltage at the node between the resistors R12 and R13 is o. As such, the Voltage at the node between the twelfth resistor R12 and the first light source LED1 is a function only of the bias current. The Voltage at this node is amplified by the sixth op-amp U6, having a gain determined by the values of the thirty-first and thirty-second resistors R31 and R32. The resulting amplified signal is proportional to the bias current. This signal is provided to the second input In2 of the microprocessor μP. The second input In2 is an analogue is a digital converter (ADC) input. Consequently, the microprocessor  $\mu P$  is provided with digital values (data) that is indicative of the Voltage at the node between the twelfth resistors R12 and the first light source LED1, which is proportional to the current flowing through the first light source LED1 in the absence of a Voltage at the INPUT terminal.

[0057] The microprocessor  $\mu P$  is configured to sample the signal at the second input In2 at a high rate, for instance 1000 samples per second. Whenever the microprocessor  $\mu P$  determines that the level of the signal received at the second input In2 is sufficiently low that the signal induced current in one of the light sources LED1 and LED2 is below a predetermined threshold, the bias current is estimated. The bias current is estimated by

processing the digitised value resulting from the Voltage at the second input In2 of the microprocessor  $\mu P$ . The threshold is chosen to have any suitable value. The threshold may be for instance 20% of the desired bias current. A low threshold may result in the bias current not being adjusted for long periods of time in normal use, but a high threshold may result in the processor incorrectly estimating and adjusting the bias current due to signal induced currents in the twelfth resistor R12. A suitable threshold results in bias current adjustment at suitably short intervals without providing sensitivity to signal induced currents in the twelfth resistor R12.

[0058] The microprocessor  $\mu P$  is configured to filter the estimated bias current values. The filtered estimates are used to drive a digital feedback loop that is implemented in software in the microprocessor  $\mu P$ , an output of which provides a digital value that represents the value of VBIAS that is needed to provide the desired bias current through the light sources LED1 and LED2. In designing the software, an ideal bias current is chosen based on the need to extend battery life (which tends towards a low bias current) and achieving acceptable sound quality (based on measurements of signal distortion and listening tests). The software integrates the estimated bias current measurement over time, taking new samples when the signal is below the threshold, as discussed above, and adjusts the PWM output to increase or decrease the bias current so as to cause the integrated measurement to approach the ideal.

[0059] The value indicative of the desired level of VBI-AS is used by the microprocessor  $\mu P$  to provide at the output Out a pulse width modulated (PWM) signal having a duty cycle that is representative of the value of VBIAS. The PWM signal is then filtered by the RC arrangement comprising the resistors R19, R35 and R36 and the capacitors C6 and C28 such as to provide a substantially DC (direct current) signal to the non-inverting input of the fifth op-amp U5.

[0060] The transmitter circuit provides particularly good noise performance, in large part because of the large peak LED current. The large peak LED current is possible because of the dual drive mechanism provided by the connection of the second and third op-amps U2 and U3 as inverting amplifiers with feedback from the node in the path including the light sources LED1 and LED2. This allows the current to be swung with a very low bias current. Taking the example of swinging the current through 120mA, this can be achieved with about 5mA of bias current. Achieving the same with a class A circuit design would require 130mA of bias current, which would present a very high draw on battery. Consequently a class A design would typically use a lower bias current, e.g. 40mA bias current, which would reduce the peak signal (by about two thirds, or 10dB) which worsens noise by about 10dB. The dual drive mechanism of the transmitter circuit 11 reduces power consumption whilst increasing the signal-to-noise ratio.

[0061] Moreover, in the transmitter circuit 11 bias volt-

25

40

45

ages are injected from a single positive bias source, namely the output Out of the microprocessor. This is possible because of the arrangement of the fourth and fifth op-amps U4 and U5, and is possible of the connection of the second and third op-amps U2 and U3 as inverting amplifiers with feedback from the node in the path including the light sources LED1 and LED2. The microprocessor  $\mu P$  is configured to examine signals received at the first input In1. The first input In1 is an ADC input, and the microprocessor  $\mu P$  generates and processes digital values that are representative of the analogue Voltage received at the first input In1. By virtue of the arrangement of the seventh op-amp U7, the analogue Voltage present at the first input In1 of the microprocessor  $\mu P$  is representative of the Voltage at the INPUT terminal.

[0062] The microprocessor  $\mu P$  is configured to detect from signals received at the first input In1 when there has been any significant signal received at the INPUT terminal. The microprocessor  $\mu P$  is configured to respond to determining that no significant signal has been present at the INPUT terminal for a predetermined period of time by powering down the transmitter circuit 11, in particular by powering down the microprocessor  $\mu P$  and ceasing to provide supply Voltage to the Voltage terminals V+ and V-. The significant period of time may for instance be 60 seconds, 300 seconds, 600 seconds etc.

**[0063]** In this way, the transmitter circuit 11 can experience reduced power consumption, because the transmitter circuit 11 is powered down and thus does not consume power when it is not in use. This can be convenient for the user, who thus does not need to remember to turn off the transmitter circuit 11 after use. The user may turn the transmitter circuit 11 on through the use of a hardware switch (not shown).

[0064] The microprocessor  $\mu P$  may determine that an insignificant level of signal is present at the INPUT terminal if the level of signal does not exceed a threshold, or does not exceed a threshold for a threshold period of time. The threshold may for instance be 0.5%, 1% or 2% of the maximum signal level, so 0.003, 0.006 or 0.012 Volts respectively, or in the range of 0.5-2% of the maximum signal level. The threshold period of time may for instance be a tenth of a second.

**[0065]** It will be appreciated that the above-described embodiments are merely illustrative and are not limiting on the scope of the claims. Various alternatives will be envisaged by the skilled person, and some will now be described.

[0066] Instead of using the microprocessor  $\mu P$  to measure the bias current and to provide the bias signal VBIAS, these functions could instead be performed by a circuit of analogue components. Using a microprocessor is advantageous in that relatively sophisticated processing can be implemented relatively easily. Also, using a microprocessor as described in the embodiments provides the additional advantage that the microprocessor  $\mu P$  can also be used to determine when no significant input signal is present and to power down the transmitter

circuit 11 accordingly. This function would be expensive to achieve using analogue components.

[0067] Instead of using a Voltage at a terminal of one of the light sources LED1 and LED2 to allow measurement of the bias current through the light sources, other arrangements are possible. For instance, in other embodiments the Voltage across the tenth and eleventh resistors R10 and R11 are measured in order to measure the bias current. When the Voltage across the tenth and eleventh resistors R10 and R11 are equal and opposite, the sum of their absolute magnitudes corresponds directly with the bias current. The Voltages across the tenth and eleventh resistors R10 and R11, and the calculation of the bias current, may be performed by a microprocessor, by analogue circuitry or by a mixture of analogue and digital circuits.

[0068] In the above embodiments, the signal at the second input In2 of the microprocessor  $\mu P$  is sampled 1000 times per second. In other embodiments, the signal of the second input In2 is sampled at a much higher frequency, in particular at a frequency that is significantly higher than the maximum frequency of the audio signals that are received at the INPUT terminal. In these embodiments, the bias current through the first and second light sources LED1 and LED2 can be measured and a Voltage for the signal VBIAS calculated every time that the input signal passes through zero Volts. Better performance is achieved in these embodiments, although at the cost of an increase in the processing requirement of the microprocessor  $\mu P$ , which may require the use of a higher capability microprocessor.

[0069] Figure 3 shows a cable arrangement 30 according to various aspects of the invention. A first jack includes a first metallic 1/4 inch plug 31 and a corresponding body 32. Within the body of the first jack is a first device comprising the transmitter circuit 11 and a 1.5 or 1.2V battery. The transmitter circuit 11 is connected to the first plug 31 so as to be able to receive analogue electrical audio frequency signals applied thereto. The LEDs LED1 and LED2 of the transmitter circuit 11 in the first device are arranged so as to pass the light that it emits into ends of two cores of a shielded optical fibre 37, which comprises the cores Corel and Core 2 and the Sheath of Figure 1. At an opposite end of the optical fibre 37, a second device 36 is included in a body of a second jack, which includes a second 1/4 inch plug 34. The second device 36 includes the receiver circuit 13 of Figure 1 and a 1.5 or 1.2 V battery. The photodiodes PD51 and PD52 in the second device 36 are arranged to receive light transmitted down the optical fibre 37. The electrical output of the second device 36 is provided to the second plug 34.

**[0070]** The cable arrangement 30 is used by mating the first plug into a signal out socket of a guitar or other sound source, and by mating the second plug 34 into a signal in socket of a mixing desk or amplification device or similar. When the guitar is played, analogue electrical audio frequency signals are provided to the conductors

25

30

35

40

45

of the first plug, and thus are carried to the input of the transmitter circuit 11 included in the first device. The first device thus amplitude modulates the audio signal onto an optical signal at baseband, which is transmitted along the optical fibre 37. The baseband amplitude modulated optical signal is received at the second device 36, where the amplitude modulation is converted into an electrical analogue audio frequency signal and provided to the conductors of the second plug 34 and thus the amplification device or mixing desk that it is connected to. The signals produced by the audio source thus are carried to the amplification device or mixing desk without being digitised and without being transmitted along a shielded electrical cable.

**[0071]** Manual distortion of the prototype optical cable 37 results in no audible change in signal, since there is no signal degradation in the optical cable 37.

**[0072]** Since current consumption of the Figure 1 circuits is low, batteries are able to power the transmitter and receiver circuits 11, 13 correctly for many hours before requiring replacement.

**[0073]** The cable arrangement 30 suffers some disadvantages compared to the conventional electrical cable arrangement. In particular, a power supply is needed at each end of the cable arrangement, whereas this is not true of the electrical cable.

**[0074]** The two jacks are visibly different from one another, for instance by the inclusion of arrows indicating the direction of signal transmission, or through the use of different patterning or colouring. This mitigates potential problems from connecting the cable arrangement 30 the wrong way around (the cable arrangement 30 is unidirectional, and can carry audio signals only from the first jack to the second jack). The conventional electrical cable on the other hand is bidirectional.

**[0075]** A break in a core of the optical cable would normally result in the ceasing of incorrect transmission, although such can also occur with conventional electrical cables.

[0076] Different audio sources produce different signal Voltages. For instance, an electric guitar produces an output signal having a maximum swing of 3 or 4 Volts, whereas certain microphones produce only 50mV or so. Although a cable arrangement optimised for use with an electrical guitar functions also with a microphone source, the converse is not true. Also, a cable arrangement capable of handling a relatively small signal swing, for instance 100mV, is optimised for use with microphone sources and is better able to handle microphone-originating signals without degradation. Accordingly, different cable arrangements, each optimised for a particular Voltage swing, may provide improved results than a single, all-purpose arrangement. Different cable arrangements may be optimised for different Voltage swings by the provision of different buffering and filtering arrangements prior to the INPUT terminal as shown in the circuit diagram of Figure 1.

[0077] Figure 4 illustrates schematically an electric gui-

tar 40 according to aspects of the invention. The guitar includes three transducers, namely a neck humbucker 41, a middle coil 42 and a bridge humbucker 43. Each of these is connected to an electronic switching circuit 44, which includes controllable potentiometers. The switching circuit 44 provides electrical analogue signals at audio frequencies to a socket 47, with which a ¼ inch plug can be mated. The guitar thusfar described is conventional.

[0078] The guitar 40 also includes a circuit 45, which comprises the Figure 2 transmitter circuit 11. The circuit 45 is connected to receive electrical analogue signals at audio frequencies from the switching circuit 44. The circuit 45 is powered by a power source, such as a 1.5 or 1.2 V battery (not shown) included in the guitar 40. The circuit 45 amplitude modulates the electrical analogue signal onto an optical signal and provides the result to an optical connector 46 mounted on a face of the housing of the guitar 40. A dual core optical cable (not shown) is connectable into the optical connector 46, and carries the optical signal generated by the circuit 45 away from the guitar. Thus, the guitar 40 provides an optical amplitude modulated signal in the same way that a combination of a conventional guitar and the first jack of the Figure 3 cable arrangement 30 would provide. All of the benefits stated above with relation to the previous Figures apply to this embodiment. Since it includes an electrical signal output socket 47, the guitar 40 also is usable conventionally, although this can be omitted if not required.

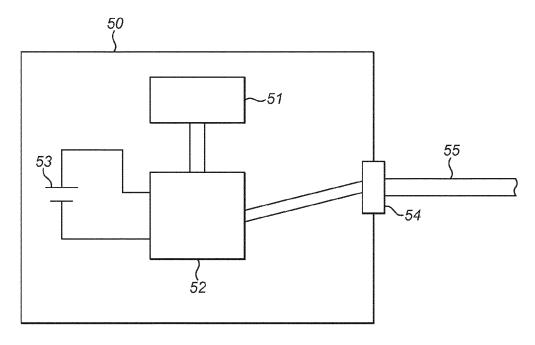

[0079] Figure 5 illustrates schematically a microphone 50 according to aspects of the invention. The microphone 50 includes a microphone transducer 51, as is conventional. The microphone transducer is connected to a circuit 52, which comprises the Figure 1A or Figure 1B circuit, the Figure 3 transmit circuit or similar. The circuit 52 is powered by a battery 53. The circuit 52 is connected to receive electrical analogue signals at audio frequencies from the microphone transducer 51. The circuit 52 amplitude modulates the electrical analogue signal onto an optical signal and provides the result to an optical connector 54 mounted on a face of the housing of the microphone 50. An optical cable 55 is removably or fixedly connected into the optical connector 54, and carries the optical signal generated by the circuit 52 away from the microphone 50. Thus, the microphone 59 provides an optical amplitude modulated signal in a way similar to that of the Figure 4 guitar 40 or the Figure 2 transmitter circuit 11.

**[0080]** Although the above describes that the sound source can be a guitar or microphone, the sound source may be any other type that produces analogue audio signals. The invention has most advantage with sound sources which are moved around during a performance, since these are most likely to have electrical cables damaged during use.

**[0081]** An additional advantage is electrical isolation. Conventional cabling includes electrical conductors. In the event of faulty amplification equipment, electrical

15

30

35

40

45

50

55

power could be transferred through the cable to a guitar player or other person, potentially resulting in electrical shock. The same could occur in the event of a lightning strike, which may occur at outdoors concerts and the like. Using an optical fibre to convey audio signals, on the contrary, provides electrical isolation between the ends of the cable, and thus provides improved safety.

**[0082]** The human ear is able to perceive audio signals between 20 Hz and 20 kHz, so it is normally only those signals that are of interest to a musician or sound producer. However, the carrying also of additional signal frequencies is not precluded by the invention, as long as the content of primary interest is in the audible frequency range.

[0083] Since the signal of interest is amplitude modulated onto the optical signal, the nature of the light source is not important, as long as the amplitude of its output is controllable. The light source need not be a single frequency source, or even fixed in frequency. An LED makes a good light source because of its ease of use and low cost.

**[0084]** A circuit arrangement (not shown) may be added prior to the input terminal so as to provide some frequency response shaping. The arrangement may comprise plural RC circuits and a switch configured to switch in one of the RC circuits and to switch out the others. This can allow a user to select a desired frequency shaping characteristic by selecting a suitable position for the switch. The arrangement may also comprise a buffer, for instance using an op-amp, between the true input terminal and the RC circuit/switch arrangement.

[0085] The current driving of the LEDs LED1 and LED2 controlled by feedback contributes to good noise performance.

**[0086]** A prototype has been constructed using the arrangement 11 of Figure 2. Performance was excellent, with a signal-to-noise ratio of 102dB. Moreover, power consumption in the prototype is very low, giving rise to a long battery life. In tests, more than 12 hours use was achieved from an AA alkaline battery.

#### Claims

1. Apparatus comprising:

first and second light sources driven respectively by second and third inverting amplifiers with feedback from the first and second light sources to provide signal content respectively on positive and negative phases of an input signal; and a bias control arrangement configured to measure a bias level of one of the light sources and to bias the second and third amplifiers based on the measured bias level.

2. Apparatus as claimed in claim 1, wherein the output of the bias control arrangement is connected to the

second and third amplifiers via an arrangement comprising a fourth amplifier and a buffer.

- 3. Apparatus as claimed in claim 2, wherein the output of the bias control arrangement is connected to an input of the buffer, wherein an output of the buffer is connected to the input of the third amplifier and to an input of the fourth amplifier, and wherein an output of the fourth amplifier is connected to the input of the second amplifier.

- 4. Apparatus as claimed in any preceding claim, wherein the bias control arrangement includes a microprocessor, and optionally wherein the microprocessor is configured to monitor the input signal terminal and is configured automatically to power down in response to detecting no significant input signal for a period of time.

- 5. Apparatus as claimed in any preceding claim, wherein the bias control arrangement is configured to calculate a bias control signal provided to the second and third amplifiers based on instances when the level of the input signal is low and to refrain from calculating the bias control signal based on instances when the level of the input signal is not low.

- 6. Apparatus as claimed in any preceding claim, wherein the bias control arrangement is configured to provide to the second and third amplifiers a pulse width modulated signal having a duty cycle that is a function of the measured bias.

- 7. Apparatus as claimed in claim 1, comprising:

first and second light sources (LED1, LED2); a first transistor (Q1) having first and second main electrodes and a control electrode;

a second transistor (Q2) having first and second main electrodes and a control electrode;

a first amplifier (U1) having first and second inputs and an output;

a second amplifier (U2) having an input and an output;

a third amplifier (U3) having an input and an output; and

a bias control arrangement having an input and an output;

### wherein:

the first light source (LED1) and the first and second main electrodes of the first transistor (Q1) are connected in series in a path between a positive supply terminal and a first node, the second light source (LED2) and the first and second main electrodes of the second transistor (Q2) are connected in series in a path between

10

15

20

30

40

45

the first node and a negative supply terminal, the first node is connected to a second input of the first amplifier (U1).

17

the input of the second amplifier is connected to the output of the first amplifier,

the output of the second amplifier is connected to the control input of the first amplifier,

the input of the third amplifier is connected to the output of the first amplifier,

the output of the third amplifier is connected to the control input of the second transistor,

the input of the first amplifier is connected to a signal input terminal (INPUT),

the input of the bias control arrangement is connected to a second node in the path through the first and second light sources and the first and second transistors,

the bias control arrangement is configured to measure bias at its input and provide a control bias signal at its output, and

the output of the bias control arrangement is connected to the input of each of the second and third amplifiers.

- 8. Apparatus as claimed in claim 7, wherein the output of the bias control arrangement is connected to the input of each of the second and third amplifiers via an arrangement comprising a fourth amplifier (U4) and a buffer (U5).

- 9. Apparatus as claimed in claim 8, wherein the output of the bias control arrangement is connected to an input of the buffer (U5), wherein an output of the buffer is connected to the input of the third amplifier (U3) and to an input of the fourth amplifier (U4), and wherein an output of the fourth amplifier (U4) is connected to the input of the second amplifier (U2).

- 10. Apparatus as claimed in any of claims 7 to 9, comprising a first resistor connected directly to the first node and in the path to the positive supply terminal and a second resistor connected directly to the first node and in the path to the negative supply terminal, and wherein the second node is connected to the first node by either the first resistor or the second resistor.

- 11. Apparatus as claimed in any of claims 7 to 10, wherein the bias control arrangement includes a microprocessor, and optionally wherein the microprocessor is configured to monitor signals received at the signal input terminal and is configured automatically to power down in response to detecting no significant input signal for a period of time.

- **12.** Apparatus as claimed in any of claims 7 to 11, wherein the bias control arrangement has a second input that is connected to the input of the first amplifier,

and wherein the bias control arrangement is configured to calculate the bias control signal based on instances when the level of the signal at the second input is low and to refrain from calculating the bias control signal based on instances when the level of the signal at the second input is not low.

- 13. Apparatus as claimed in any of claims 7 to 12, wherein the bias control arrangement is configured to provide at its output a pulse width modulated signal having a duty cycle that is a function of the measured

bias.

- **14.** Apparatus as claimed in any preceding claim, comprising an electrical connector, for instance a jack plug, for receiving an electrical input signal.

- **15.** A cable arrangement comprising first and second devices connected by a dual core optical waveguide, wherein the first device comprises apparatus as claimed in claim 14.

55

12

*FIG.* 5

# **EUROPEAN SEARCH REPORT**

Application Number EP 14 15 2033

|                                            | DOCUMENTS CONSIDERE                                                                                                                                                        | D TO BE RELEVANT                                                                                                          |                                                                     |                                             |  |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------|--|--|

| Category                                   | Citation of document with indicati of relevant passages                                                                                                                    | on, where appropriate,                                                                                                    | Relevant<br>to claim                                                | CLASSIFICATION OF THE APPLICATION (IPC)     |  |  |

| A                                          | WO 82/02632 A1 (WESTER 5 August 1982 (1982-08 * page 4, lines 15-31;                                                                                                       | -05)                                                                                                                      | 1-15                                                                | INV.<br>H04B10/40<br>H04B10/25<br>H04B10/50 |  |  |

| Y                                          | WO 2007/031794 A1 (BAR<br>HOLMES DAVID [GB])<br>22 March 2007 (2007-03<br>* page 18, lines 4-31;                                                                           | -22)                                                                                                                      | 1-15                                                                |                                             |  |  |

| Υ                                          | JP S62 256538 A (NEC C<br>9 November 1987 (1987-<br>* abstract *                                                                                                           |                                                                                                                           | 1-15                                                                |                                             |  |  |

| A                                          | EP 0 878 882 A2 (AT & CORP) 18 November 1998 * page 5, lines 10-28;                                                                                                        | (1998-11-18)                                                                                                              | 1-15                                                                |                                             |  |  |

| A                                          | US 2008/187324 A1 (AKI<br>AL) 7 August 2008 (200<br>* paragraph [0007]; fi                                                                                                 | 8-08-07)                                                                                                                  | 1-15                                                                | TECHNICAL FIELDS                            |  |  |

| A                                          | US 2006/255746 A1 (KUMAR RUSS<br>AL) 16 November 2006 (2006-11<br>* paragraphs [0031] - [0035];                                                                            | 2006-11-16)                                                                                                               | Γ 4,5,11                                                            | H04B<br>H01S<br>H05B                        |  |  |

|                                            |                                                                                                                                                                            |                                                                                                                           |                                                                     |                                             |  |  |

|                                            | The present search report has been of                                                                                                                                      | drawn up for all claims                                                                                                   |                                                                     |                                             |  |  |

|                                            | Place of search                                                                                                                                                            | Date of completion of the search                                                                                          |                                                                     | Examiner                                    |  |  |

|                                            | Munich                                                                                                                                                                     | 14 August 2014                                                                                                            | De                                                                  | Vries, Jane                                 |  |  |

| X : parti<br>Y : parti<br>docu<br>A : tech | ATEGORY OF CITED DOCUMENTS  icularly relevant if taken alone cularly relevant if combined with another iment of the same category nological background -written disclosure | T : theory or princip E : earlier patent do after the filing da D : document cited L : document cited & : member of the s | ocument, but publ<br>ate<br>in the application<br>for other reasons | ished on, or                                |  |  |

### ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 14 15 2033

5

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

14-08-2014

| 10 |

|----|

|----|

| 15 |  |  |  |

|----|--|--|--|

|    |  |  |  |

|    |  |  |  |

25

20

30

35

40

45

50

55

FORM P0459

| Patent docume<br>cited in search re |        | Publication<br>date |                                                    | Patent family member(s)                                                                                       |                                           | Publication<br>date                                                                                                        |

|-------------------------------------|--------|---------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| WO 8202632                          | A1     | 05-08-1982          | CA<br>EP<br>JP<br>US<br>WO                         | 1164697<br>0069760<br>\$57502198<br>4393518<br>8202632                                                        | A1<br>A<br>A                              | 03-04-1984<br>19-01-1983<br>09-12-1982<br>12-07-1983<br>05-08-1982                                                         |

| WO 20070317                         | '94 A1 | 22-03-2007          | EP<br>WO                                           | 1941635<br>2007031794                                                                                         |                                           | 09-07-2008<br>22-03-2007                                                                                                   |

| JP S6225653                         | 8 A    | 09-11-1987          | NONE                                               |                                                                                                               |                                           |                                                                                                                            |

| EP 0878882                          | A2     | 18-11-1998          | AU<br>AU<br>CA<br>CN<br>DE<br>DE<br>JP<br>JP<br>US | 736324<br>6481798<br>2235026<br>1199943<br>69802228<br>69802228<br>0878882<br>4291428<br>H10321940<br>5963570 | A<br>A1<br>A<br>D1<br>T2<br>A2<br>B2<br>A | 26-07-2001<br>12-11-1998<br>12-11-1998<br>25-11-1998<br>06-12-2001<br>27-06-2002<br>18-11-1998<br>08-07-2009<br>04-12-1998 |

| US 20081873                         | 324 A1 | 07-08-2008          | JP<br>JP<br>US                                     | 4893637<br>2008197639<br>2008187324                                                                           | Α                                         | 07-03-2012<br>28-08-2008<br>07-08-2008                                                                                     |

| US 20062557                         | 46 A1  | 16-11-2006          | BR<br>CA<br>CN<br>EP<br>HK<br>JP<br>JP<br>US<br>WO | PI0612430<br>2608743<br>101176386<br>1884141<br>1118169<br>4634506<br>2008541407<br>2006255746<br>2006124893  | A1<br>A2<br>A1<br>B2<br>A<br>A1           | 22-05-2012<br>23-11-2006<br>07-05-2008<br>06-02-2008<br>08-07-2011<br>23-02-2011<br>20-11-2008<br>16-11-2006               |

|                                     |        |                     |                                                    |                                                                                                               |                                           |                                                                                                                            |

© For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

# EP 2 833 568 A1

### REFERENCES CITED IN THE DESCRIPTION

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

# Patent documents cited in the description

• WO 2007031794 A [0004]