## 9.0 INTERRUPTS

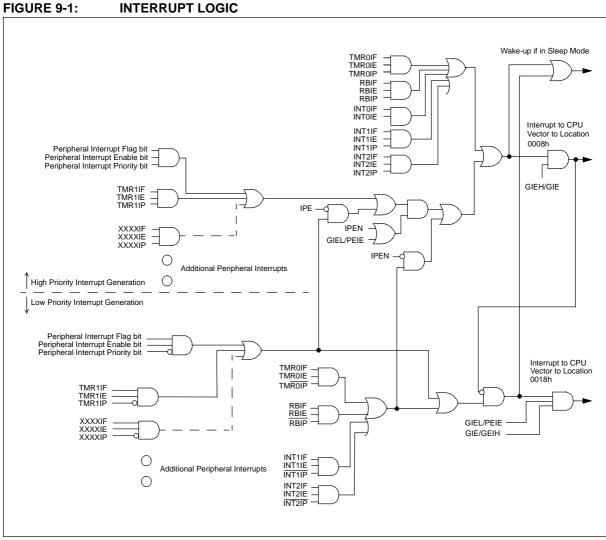

The PIC18F2480/2580/4480/4580 devices have multiple interrupt sources and an interrupt priority feature that allows each interrupt source to be assigned a high priority level or a low priority level. The high priority interrupt vector is at 000008h and the low priority interrupt vector is at 000018h. High priority interrupt events will interrupt any low priority interrupts that may be in progress.

There are ten registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

Each interrupt source has three bits to control its operation. The functions of these bits are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- Priority bit to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 000008h or 000018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PICmicro<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 000008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High priority interrupt sources can interrupt a low priority interrupt. Low priority interrupts are not processed while high priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (00008h or 000018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INT pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

**Note:** Do not use the MOVFF instruction to modify any of the interrupt control registers while **any** interrupt is enabled. Doing so may cause erratic microcontroller behavior.

# PIC18F2480/2580/4480/4580

#### 9.1 **INTCON Registers**

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

### **REGISTER 9**

| R/W-0                          | R/W-0                                                 | R/W-0         | R/W-0         | R/W-0        | R/W-0        | R/W-0       | R/\    |

|--------------------------------|-------------------------------------------------------|---------------|---------------|--------------|--------------|-------------|--------|

| GIE/GIEF                       | I PEIE/GIEL                                           | TMR0IE        | INTOIE        | RBIE         | TMR0IF       | INTOIF      | RE     |

| bit 7                          |                                                       |               |               |              |              |             |        |

| GIE/GIEH:                      | Global Interrup                                       | t Enable bit  |               |              |              |             |        |

|                                | <u>N = 0:</u><br>es all unmasked<br>es all interrupts | interrupts    |               |              |              |             |        |

| <u>When IPEI</u><br>1 = Enable | -                                                     |               |               |              |              |             |        |

|                                | .: Peripheral Inte                                    | , ,           | bit           |              |              |             |        |

| When IPE                       | •                                                     | peripheral in |               |              |              |             |        |

| When IPE                       |                                                       | peripheral ir |               |              |              |             |        |

|                                | MR0 Overflow I                                        |               |               |              |              |             |        |

|                                | es the TMR0 ove<br>es the TMR0 ove                    |               |               |              |              |             |        |

| INTOIE: IN                     | T0 External Inte                                      | rrupt Enable  | bit           |              |              |             |        |

|                                | es the INT0 exte<br>es the INT0 exte                  |               |               |              |              |             |        |

| RBIE: RB                       | Port Change Int                                       | errupt Enable | e bit         |              |              |             |        |

|                                | es the RB port ch<br>es the RB port c                 |               |               |              |              |             |        |

| TMR0IF: T                      | MR0 Overflow I                                        | nterrupt Flag | bit           |              |              |             |        |

|                                | register has ove<br>register did not                  | •             | st be cleared | t in softwa  | re)          |             |        |

|                                | T0 External Inte                                      |               |               |              |              |             |        |

|                                | T0 external inte<br>T0 external inte                  |               |               | cleared in s | software)    |             |        |

| RBIF: RB                       | Port Change Inte                                      | errupt Flag b | it            |              |              |             |        |

|                                | t one of the RB7<br>of the RB7:RB4                    |               |               | e (must be   | cleared in s | oftware)    |        |

| Note:                          | A mismatch co<br>mismatch cond                        |               |               |              | -            | RTB will er | nd the |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

# PIC18F2480/2580/4480/4580

| <b>REGISTER 9-2:</b> | INTCON2                                                                                 | : INTERRU                                                                                                                       |               |              | TER 2        |           |              |        |

|----------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|--------------|-----------|--------------|--------|

|                      | R/W-1                                                                                   | R/W-1                                                                                                                           | R/W-1         | R/W-1        | U-0          | R/W-1     | U-0          | R/W-1  |

|                      | RBPU                                                                                    | INTEDG0                                                                                                                         | INTEDG1       | INTEDG2      | _            | TMR0IP    |              | RBIP   |

|                      | bit 7                                                                                   |                                                                                                                                 |               |              |              |           |              | bit 0  |

|                      |                                                                                         |                                                                                                                                 |               |              |              |           |              |        |

| bit 7                | RBPU: PC                                                                                | RTB Pull-up                                                                                                                     | Enable bit    |              |              |           |              |        |

|                      |                                                                                         | <ul> <li>1 = All PORTB pull-ups are disabled</li> <li>0 = PORTB pull-ups are enabled by individual port latch values</li> </ul> |               |              |              |           |              |        |

| bit 6                | INTEDG0:                                                                                | External Inte                                                                                                                   | rrupt 0 Edge  | e Select bit |              |           |              |        |

|                      |                                                                                         | upt on rising e<br>upt on falling (                                                                                             |               |              |              |           |              |        |

| bit 5                | INTEDG1:                                                                                | External Inte                                                                                                                   | rrupt 1 Edge  | e Select bit |              |           |              |        |

|                      | <ul> <li>1 = Interrupt on rising edge</li> <li>0 = Interrupt on falling edge</li> </ul> |                                                                                                                                 |               |              |              |           |              |        |

| bit 4                | INTEDG2:                                                                                | External Inte                                                                                                                   | rrupt 2 Edge  | e Select bit |              |           |              |        |

|                      |                                                                                         | upt on rising e<br>upt on falling (                                                                                             | 0             |              |              |           |              |        |

| bit 3                | Unimplem                                                                                | nented: Read                                                                                                                    | <b>as</b> '0' |              |              |           |              |        |

| bit 2                | TMR0IP: T                                                                               | MR0 Overflo                                                                                                                     | w Interrupt I | Priority bit |              |           |              |        |

|                      | 1 = High p<br>0 = Low p                                                                 |                                                                                                                                 |               |              |              |           |              |        |

| bit 1                | Unimplem                                                                                | nented: Read                                                                                                                    | <b>as</b> '0' |              |              |           |              |        |

| bit 0                |                                                                                         | Port Change                                                                                                                     | Interrupt Pr  | iority bit   |              |           |              |        |

|                      | 1 = High p<br>0 = Low p                                                                 | -                                                                                                                               |               |              |              |           |              |        |

|                      | Legend:                                                                                 |                                                                                                                                 |               |              |              |           |              |        |

|                      | R = Reada                                                                               | able bit                                                                                                                        | W = W         | /ritable bit | U = Unim     | plemented | bit, read as | '0'    |

|                      | -n = Value                                                                              | at POR                                                                                                                          | '1' = B       | it is set    | '0' = Bit is | s cleared | x = Bit is u | nknown |

|                      |                                                                                         |                                                                                                                                 |               |              |              |           |              |        |

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| REGISTER 9-3: | INTCON3:                                     | INTERRU                    | PT CONTI                       |                                         | STER 3       |              |              |        |

|---------------|----------------------------------------------|----------------------------|--------------------------------|-----------------------------------------|--------------|--------------|--------------|--------|

|               | R/W-1                                        | R/W-1                      | U-0                            | R/W-0                                   | R/W-0        | U-0          | R/W-0        | R/W-0  |

|               | INT2IP                                       | INT1IP                     | _                              | INT2IE                                  | INT1IE       | _            | INT2IF       | INT1IF |

|               | bit 7                                        |                            |                                |                                         |              |              |              | bit 0  |

| bit 7         | INT2IP: IN                                   | T2 External                | Interrupt Pri                  | ority bit                               |              |              |              |        |

|               | 1 = High p<br>0 = Low pr                     | •                          |                                |                                         |              |              |              |        |

| bit 6         | INT1IP: INT1 External Interrupt Priority bit |                            |                                |                                         |              |              |              |        |

|               | 1 = High p<br>0 = Low pr                     | ,                          |                                |                                         |              |              |              |        |

| bit 5         | Unimplem                                     | Unimplemented: Read as '0' |                                |                                         |              |              |              |        |

| bit 4         | INT2IE: IN                                   | T2 External                | Interrupt En                   | able bit                                |              |              |              |        |

|               |                                              |                            | external inte<br>external inte | •                                       |              |              |              |        |

| bit 3         | INT1IE: IN                                   | T1 External                | Interrupt En                   | able bit                                |              |              |              |        |

|               |                                              |                            | external inte<br>external inte | •                                       |              |              |              |        |

| bit 2         | Unimplem                                     | ented: Read                | <b>d as</b> '0'                |                                         |              |              |              |        |

| bit 1         | INT2IF: INT                                  | T2 External                | Interrupt Fla                  | g bit                                   |              |              |              |        |

|               |                                              |                            | interrupt oc<br>interrupt dic  | curred (mus <sup>.</sup><br>I not occur | t be cleared | in software) |              |        |

| bit 0         | INT1IF: INT                                  | T1 External                | Interrupt Fla                  | g bit                                   |              |              |              |        |

|               |                                              |                            | interrupt oc<br>interrupt dic  | curred (mus<br>I not occur              | t be cleared | in software) |              |        |

|               | Legend:                                      |                            |                                |                                         |              |              |              |        |

|               | R = Reada                                    | ble bit                    | W = V                          | Vritable bit                            | U = Unir     | nplemented   | bit, read as | 'O'    |

| Logona.           |                  |                      |                    |  |

|-------------------|------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

|                   |                  |                      |                    |  |

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

## 9.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Request (Flag) registers (PIR1, PIR2).

- **Note 1:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

## REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0                | R/W-0 | R-0  | R-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|------|------|-------|--------|--------|--------|

| PSPIF <sup>(1)</sup> | ADIF  | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |      |      |       |        |        | bit 0  |

| 7   | PSPIF: Parallel Slave F                                                     | ort Read/Write Interrup  | ot Flag bit <sup>(1)</sup>                 |

|-----|-----------------------------------------------------------------------------|--------------------------|--------------------------------------------|

|     | <ul><li>1 = A read or a write op</li><li>0 = No read or write had</li></ul> |                          | e (must be cleared in software)            |

|     | Note 1: This bit is re                                                      | eserved on PIC18F2X8     | 0 devices; always maintain this bit clear. |

| t 6 | ADIF: A/D Converter In                                                      | terrupt Flag bit         |                                            |

|     | <ul><li>1 = An A/D conversion</li><li>0 = The A/D conversion</li></ul>      |                          | eared in software)                         |

| t 5 | RCIF: EUSART Receiv                                                         | e Interrupt Flag bit     |                                            |

|     | 1 = The EUSART receiv<br>0 = The EUSART receiv                              |                          | II (cleared when RCREG is read)            |

| t 4 | TXIF: EUSART Transm                                                         | it Interrupt Flag bit    |                                            |

|     | 1 = The EUSART trans<br>0 = The EUSART trans                                |                          | mpty (cleared when TXREG is written)       |

| t 3 | SSPIF: Master Synchro                                                       | nous Serial Port Interru | upt Flag bit                               |

|     | <ul><li>1 = The transmission/re</li><li>0 = Waiting to transmit/</li></ul>  |                          | ust be cleared in software)                |

| t 2 | CCP1IF: CCP1 Interrup                                                       | ot Flag bit              |                                            |

|     | Capture mode:                                                               |                          |                                            |

|     | 1 = A TMR1 register ca<br>0 = No TMR1 register c                            |                          | e cleared in software)                     |

|     | Compare mode:                                                               |                          |                                            |

|     | 1 = A TMR1 register co<br>0 = No TMR1 register c                            | •                        | (must be cleared in software)<br>d         |

|     | <u>PWM mode:</u><br>Unused in this mode.                                    |                          |                                            |

| t 1 | TMR2IF: TMR2 to PR2                                                         | Match Interrupt Flag bi  | t                                          |

|     | 1 = TMR2 to PR2 matc<br>0 = No TMR2 to PR2 m                                |                          | eared in software)                         |

| t 0 | TMR1IF: TMR1 Overflo                                                        | w Interrupt Flag bit     |                                            |

|     | 1 = TMR1 register over<br>0 = MR1 register did no                           |                          | d in software)                             |

|     | Legend:                                                                     |                          |                                            |

|     | R = Readable bit                                                            | W = Writable bit         | U = Unimplemented bit, read as '0'         |

|     |                                                                             |                          |                                            |

-n = Value at POR

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

| REGISTER 9-5: | PIR2: PEF                               | RIPHERAL                                                                                                                                                        |                 | JPT REQU     | IEST (FLA     | G) REGIS     | TER 2         |                        |

|---------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|---------------|--------------|---------------|------------------------|

|               | R/W-0                                   | R/W-0                                                                                                                                                           | U-0             | R/W-0        | R/W-0         | R/W-0        | R/W-0         | R/W-0                  |

|               | OSCFIF                                  | CMIF <sup>(1)</sup>                                                                                                                                             | _               | EEIF         | BCLIF         | HLVDIF       | TMR3IF        | ECCP1IF <sup>(1)</sup> |

|               | bit 7                                   | 1                                                                                                                                                               |                 |              |               |              |               | bit 0                  |

| bit 7         | OSCFIF: (                               | Dscillator Fa                                                                                                                                                   | il Interrupt F  | lag bit      |               |              |               |                        |

|               | 0 = Syster                              | m clock ope                                                                                                                                                     | rating          |              | hanged to II  | NTOSC (mu    | ist be cleare | ed in software)        |

| bit 6         |                                         | nparator Inte                                                                                                                                                   |                 |              |               |              |               |                        |

|               |                                         | <ul> <li>1 = Comparator input has changed (must be cleared in software)</li> <li>0 = Comparator input has not changed</li> </ul>                                |                 |              |               |              |               |                        |

| bit 5         | Unimplem                                | ented: Rea                                                                                                                                                      | <b>d as</b> '0' |              |               |              |               |                        |

| bit 4         |                                         | a EEPROM/                                                                                                                                                       |                 | -            | -             | -            |               |                        |

|               |                                         | <ul> <li>1 = The write operation is complete (must be cleared in software)</li> <li>0 = The write operation is not complete, or has not been started</li> </ul> |                 |              |               |              |               |                        |

| bit 3         | BCLIF: Bus Collision Interrupt Flag bit |                                                                                                                                                                 |                 |              |               |              |               |                        |

|               |                                         | collision oc                                                                                                                                                    |                 | t be cleared | l in software | e)           |               |                        |

|               |                                         | s collision o                                                                                                                                                   |                 |              |               |              |               |                        |

| bit 2         |                                         | ligh/Low-Vo                                                                                                                                                     | •               |              | •             |              |               |                        |

|               |                                         | voltage con<br>evice voltag                                                                                                                                     |                 | •            |               | ,            | int           |                        |

| bit 1         | TMR3IF: T                               | MR3 Overfl                                                                                                                                                      | ow Interrup     | t Flag bit   |               |              |               |                        |

|               |                                         | register over<br>register did                                                                                                                                   |                 |              | ed in softwa  | are)         |               |                        |

| bit 0         | ECCP1IF:                                | CCPx Inter                                                                                                                                                      | rupt Flag bit   | (1)          |               |              |               |                        |

|               |                                         | <u>ode:</u><br>R1 register c<br>IR1 register                                                                                                                    |                 |              | be cleared i  | n software)  |               |                        |

|               | 0 = No TM                               | R1 register o<br>IR1 register                                                                                                                                   | •               |              |               | cleared in s | oftware)      |                        |

|               | <u>PWM mod</u><br>Unused in             |                                                                                                                                                                 |                 |              |               |              |               |                        |

|               | Note 1:                                 | These bits                                                                                                                                                      | are availab     | le in PIC18  | F4X80 and     | reserved in  | PIC18F2X8     | 0 devices.             |

|               |                                         |                                                                                                                                                                 |                 |              |               |              |               |                        |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented I  | bit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| REGISTER 9-6: | PIR3: PERIPHERAL INTI                                                                 | ERRUPT REQU          | JEST (FLA             | G) REGIST             | ER 3        |            |

|---------------|---------------------------------------------------------------------------------------|----------------------|-----------------------|-----------------------|-------------|------------|

| Mode 0        | R/W-0 R/W-0 R/V                                                                       | V-0 R/W-0            | R/W-0                 | R/W-0                 | R/W-0       | R/W-0      |

| induc u       | IRXIF WAKIF ERF                                                                       | RIF TXB2IF           | TXB1IF <sup>(1)</sup> | TXB0IF <sup>(1)</sup> | RXB1IF      | RXB0IF     |

|               | R/W-0 R/W-0 R/W                                                                       | V-0 R/W-0            | R/W-0                 | R/W-0                 | R/W-0       | R/W-0      |

| Mode 1, 2     | IRXIF WAKIF ERF                                                                       |                      | TXB1IF <sup>(1)</sup> | TXB0IF <sup>(1)</sup> | RXBnIF      | FIFOWMIF   |

|               | bit 7                                                                                 |                      |                       |                       |             | bit 0      |

|               |                                                                                       |                      |                       |                       |             |            |

| bit 7         | IRXIF: CAN Invalid Receive                                                            | •                    |                       |                       |             |            |

|               | <ul> <li>1 = An invalid message has</li> <li>0 = No invalid message on (</li> </ul>   |                      | CAN DUS               |                       |             |            |

| bit 6         | WAKIF: CAN bus Activity W                                                             |                      | Flag bit              |                       |             |            |

|               | 1 = Activity on CAN bus has                                                           |                      | Ū                     |                       |             |            |

|               | 0 = No activity on CAN bus                                                            |                      |                       |                       |             |            |

| bit 5         | ERRIF: CAN bus Error Inter                                                            |                      | ( 14 I                | ,                     |             |            |

|               | 1 = An error has occurred in<br>0 = No CAN module errors                              | the CAN module       | e (multiple sc        | ources)               |             |            |

| bit 4         | When CAN is in Mode 0:                                                                |                      |                       |                       |             |            |

|               | TXB2IF: CAN Transmit Buff                                                             | er 2 Interrupt Fla   | g bit                 |                       |             |            |

|               | 1 = Transmit Buffer 2 has c                                                           |                      |                       |                       | may be rel  | oaded      |

|               | 0 = Transmit Buffer 2 has n                                                           |                      | nsmission of          | a message             |             |            |

|               | When CAN is in Mode 1 or 2<br><b>TXBnIF:</b> Any Transmit Buffe                       |                      | vit                   |                       |             |            |

|               | 1 = One or more transmit                                                              |                      |                       | mission of a          | a message   | and may be |

|               | reloaded                                                                              |                      |                       |                       |             |            |

|               | 0 = No transmit buffer is rea                                                         |                      | (1)                   |                       |             |            |

| bit 3         | TXB1IF: CAN Transmit Buff                                                             | •                    | •                     |                       |             | a da d     |

|               | 1 = Transmit Buffer 1 has co<br>0 = Transmit Buffer 1 has no                          |                      |                       |                       | nay be reic | baded      |

| bit 2         | <b>TXB0IF:</b> CAN Transmit Buff                                                      |                      |                       | incoorage             |             |            |

|               | 1 = Transmit Buffer 0 has co                                                          | •                    | •                     | essage and r          | nay be relo | aded       |

|               | 0 = Transmit Buffer 0 has no                                                          | ot completed tran    | smission of a         | a message             |             |            |

| bit 1         | When CAN is in Mode 0:<br><b>RXB1IF:</b> CAN Receive Buffe                            | or 1 Interrupt Elev  | a hit                 |                       |             |            |

|               | 1 = Receive Buffer 1 has rec                                                          |                      |                       |                       |             |            |

|               | 0 = Receive Buffer 1 has no                                                           |                      | •                     |                       |             |            |

|               | When CAN is in Mode 1 or 2                                                            |                      |                       |                       |             |            |

|               | <b>RXBnIF:</b> Any Receive Buffe                                                      |                      |                       |                       |             |            |

|               | <ul> <li>1 = One or more receive but</li> <li>0 = No receive buffer has re</li> </ul> |                      |                       | sage                  |             |            |

| bit 0         | When CAN is in Mode 0:                                                                |                      | oougo                 |                       |             |            |

|               | RXB0IF: CAN Receive Buffe                                                             | er 0 Interrupt Flag  | g bit                 |                       |             |            |

|               | 1 = Receive Buffer 0 has rec                                                          |                      | 0                     |                       |             |            |

|               | <ul><li>0 = Receive Buffer 0 has no</li><li>When CAN is in Mode 1:</li></ul>          | t received a new     | message               |                       |             |            |

|               | Unimplemented: Read as '                                                              | 0'                   |                       |                       |             |            |

|               | When CAN is in Mode 2:                                                                |                      |                       |                       |             |            |

|               | FIFOWMIF: FIFO Waterman                                                               |                      | bit                   |                       |             |            |

|               | 1 = FIFO high watermark is                                                            |                      |                       |                       |             |            |

|               | 0 = FIFO high watermark is                                                            |                      | aroad to (c)          |                       |             |            |

|               | Note 1: In CAN Mode 1                                                                 | anu ∠, this dit is f |                       |                       |             |            |

|               | Legend:                                                                               |                      |                       |                       |             | ]          |

|               |                                                                                       |                      |                       |                       |             | (0)        |

| FER 9-6: | PIR3: PERIPHERAL | INTERRUPT REQUEST | (FLAG) REGISTER 3 |  |

|----------|------------------|-------------------|-------------------|--|

R = Readable bit

-n = Value at POR

W = Writable bit

'1' = Bit is set

x = Bit is unknown

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

## 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

| REGISTER 9-7: | PIE1: PERIPHERAL | INTERRUPT ENABLE REGISTER 1 |

|---------------|------------------|-----------------------------|

|               |                  |                             |

| ER 9-7. | FIEL FERIFIERAL INTERROFT ENABLE REGISTER T                                                                           |            |                            |              |             |           |              |        |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------|------------|----------------------------|--------------|-------------|-----------|--------------|--------|--|--|--|--|

|         | R/W-0                                                                                                                 | R/W-0      | R/W-0                      | R/W-0        | R/W-0       | R/W-0     | R/W-0        | R/W-0  |  |  |  |  |

|         | PSPIE <sup>(1)</sup>                                                                                                  | ADIE       | RCIE                       | TXIE         | SSPIE       | CCP1IE    | TMR2IE       | TMR1IE |  |  |  |  |

|         | bit 7                                                                                                                 |            |                            |              |             |           |              | bit 0  |  |  |  |  |

| bit 7   | PSPIE: Parallel Slave Port Read/Write Interrupt Enable bit <sup>(1)</sup>                                             |            |                            |              |             |           |              |        |  |  |  |  |

|         | <ul> <li>1 = Enables the PSP read/write interrupt</li> <li>0 = Disables the PSP read/write interrupt</li> </ul>       |            |                            |              |             |           |              |        |  |  |  |  |

|         | <b>Note 1:</b> This bit is reserved on PIC18F2X80 devices; always maintain this bit clear.                            |            |                            |              |             |           |              |        |  |  |  |  |

| bit 6   | ADIE: A/D Converter Interrupt Enable bit<br>1 = Enables the A/D interrupt<br>0 = Disables the A/D interrupt           |            |                            |              |             |           |              |        |  |  |  |  |

| bit 5   |                                                                                                                       |            | ve Interrupt               | Enable bit   |             |           |              |        |  |  |  |  |

| bit o   | 1 = Enables                                                                                                           | s the EUSA | RT receive i               | nterrupt     |             |           |              |        |  |  |  |  |

| bit 4   | TXIE: EUSART Transmit Interrupt Enable bit                                                                            |            |                            |              |             |           |              |        |  |  |  |  |

|         |                                                                                                                       |            | RT transmit<br>RT transmit |              |             |           |              |        |  |  |  |  |

| bit 3   | SSPIE: Master Synchronous Serial Port Interrupt Enable bit                                                            |            |                            |              |             |           |              |        |  |  |  |  |

|         | <ul> <li>1 = Enables the MSSP interrupt</li> <li>0 = Disables the MSSP interrupt</li> </ul>                           |            |                            |              |             |           |              |        |  |  |  |  |

| bit 2   | CCP1IE: CCP1 Interrupt Enable bit                                                                                     |            |                            |              |             |           |              |        |  |  |  |  |

|         | <ul> <li>1 = Enables the CCP1 interrupt</li> <li>0 = Disables the CCP1 interrupt</li> </ul>                           |            |                            |              |             |           |              |        |  |  |  |  |

| bit 1   | TMR2IE: T                                                                                                             | MR2 to PR2 | 2 Match Inte               | rrupt Enable | bit         |           |              |        |  |  |  |  |

|         | <ul> <li>1 = Enables the TMR2 to PR2 match interrupt</li> <li>0 = Disables the TMR2 to PR2 match interrupt</li> </ul> |            |                            |              |             |           |              |        |  |  |  |  |

| bit 0   | TMR1IE: TMR1 Overflow Interrupt Enable bit                                                                            |            |                            |              |             |           |              |        |  |  |  |  |

|         | <ul> <li>1 = Enables the TMR1 overflow interrupt</li> <li>0 = Disables the TMR1 overflow interrupt</li> </ul>         |            |                            |              |             |           |              |        |  |  |  |  |

|         | Legend:                                                                                                               |            |                            |              |             |           |              |        |  |  |  |  |

|         | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                  |            |                            |              |             |           |              |        |  |  |  |  |

|         | -n = Value a                                                                                                          | at POR     | '1' = B                    | it is set    | '0' = Bit i | s cleared | x = Bit is u | nknown |  |  |  |  |

# PIC18F2480/2580/4480/4580

| ER 9-8: | PIE2: PEF                                                    | RIPHERAL                                             | INTERRU     | IPT ENAB           | LE REGIS    | TER 2       |            |                        |  |  |  |  |  |

|---------|--------------------------------------------------------------|------------------------------------------------------|-------------|--------------------|-------------|-------------|------------|------------------------|--|--|--|--|--|

|         | R/W-0                                                        | R/W-0                                                | U-0         | R/W-0              | R/W-0       | R/W-0       | R/W-0      | R/W-0                  |  |  |  |  |  |

|         | OSCFIE                                                       | CMIE <sup>(1)</sup>                                  | _           | EEIE               | BCLIE       | HLVDIE      | TMR3IE     | ECCP1IE <sup>(2)</sup> |  |  |  |  |  |

|         | bit 7                                                        | i i                                                  |             |                    |             |             |            | bit 0                  |  |  |  |  |  |

| bit 7   | OSCFIE: (                                                    | Oscillator Fail                                      | Interrupt I | Enable bit         |             |             |            |                        |  |  |  |  |  |

|         | 1 = Enabl<br>0 = Disab                                       |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

| bit 6   | CMIE: Cor                                                    | CMIE: Comparator Interrupt Enable bit <sup>(1)</sup> |             |                    |             |             |            |                        |  |  |  |  |  |

|         | 1 = Enabl<br>0 = Disab                                       |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

| bit 5   | Unimplem                                                     | Unimplemented: Read as '0'                           |             |                    |             |             |            |                        |  |  |  |  |  |

| bit 4   | EEIE: Data EEPROM/Flash Write Operation Interrupt Enable bit |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

|         | 1 = Enabl<br>0 = Disab                                       |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

| bit 3   | BCLIE: Bus Collision Interrupt Enable bit                    |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

|         | 1 = Enabl<br>0 = Disab                                       |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

| bit 2   | HLVDIE: High/Low-Voltage Detect Interrupt Enable bit         |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

|         | 1 = Enabl<br>0 = Disab                                       |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

| bit 1   | TMR3IE: 1                                                    | MR3 Overflo                                          | w Interrup  | t Enable bit       |             |             |            |                        |  |  |  |  |  |

|         | 1 = Enabl<br>0 = Disab                                       |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

| bit 0   | ECCP1IE:                                                     | CCP1 Interr                                          | upt Enable  | bit <sup>(2)</sup> |             |             |            |                        |  |  |  |  |  |

|         | 1 = Enabl<br>0 = Disab                                       |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

|         | Note 1:                                                      | This bit is a                                        | vailable in | PIC18F4X8          | 0 devices a | nd reserved | in PIC18F2 | 2X80 devices.          |  |  |  |  |  |

|         | 2:                                                           | This bit is a                                        | vailable in | PIC18F4X8          | 0 devices o | nly.        |            |                        |  |  |  |  |  |

|         |                                                              |                                                      |             |                    |             |             |            |                        |  |  |  |  |  |

## **REGISTER 9-8**

###

.1 L

| Legena:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

| <b>REGISTER 9-9:</b> | PIE3: PEI                                                                               | RIPHERAI                                                                                                                                                        |               |              | BLE REGIS             | STER 3                |        |          |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|-----------------------|-----------------------|--------|----------|--|--|--|

| Mode 0               | R/W-0                                                                                   | R/W-0                                                                                                                                                           | R/W-0         | R/W-0        | R/W-0                 | R/W-0                 | R/W-0  | R/W-0    |  |  |  |

| Mode u               | IRXIE                                                                                   | WAKIE                                                                                                                                                           | ERRIE         | TXB2IE       | TXB1IE <sup>(1)</sup> | TXB0IE <sup>(1)</sup> | RXB1IE | RXB0IE   |  |  |  |

|                      | R/W-0                                                                                   | R/W-0                                                                                                                                                           | R/W-0         | R/W-0        | R/W-0                 | R/W-0                 | R/W-0  | R/W-0    |  |  |  |

| Mode 1, 2            | IRXIE                                                                                   | WAKIE                                                                                                                                                           | ERRIE         | TXBnIE       | TXB1IE <sup>(1)</sup> | TXB0IE <sup>(1)</sup> | RXBnIE | FIFOWMIE |  |  |  |

|                      | bit 7                                                                                   |                                                                                                                                                                 |               |              |                       |                       |        | bit 0    |  |  |  |

| bit 7                |                                                                                         | <b>RXIE:</b> CAN Invalid Received Message Interrupt Enable bit<br>1 = Enable invalid message received interrupt                                                 |               |              |                       |                       |        |          |  |  |  |

|                      | 0 <b>= Disabl</b>                                                                       | 0 = Disable invalid message received interrupt                                                                                                                  |               |              |                       |                       |        |          |  |  |  |

| bit 6                |                                                                                         | <b>VAKIE:</b> CAN bus Activity Wake-up Interrupt Enable bit <ul> <li>L = Enable bus activity wake-up interrupt</li> </ul>                                       |               |              |                       |                       |        |          |  |  |  |

|                      | <ul> <li>0 = Disable bus activity wake-up interrupt</li> </ul>                          |                                                                                                                                                                 |               |              |                       |                       |        |          |  |  |  |

| bit 5                | 1 = Enable                                                                              | ERRIE: CAN bus Error Interrupt Enable bit<br>L = Enable CAN bus error interrupt<br>D = Disable CAN bus error interrupt                                          |               |              |                       |                       |        |          |  |  |  |

| bit 4                | TXB2IE: (                                                                               | When CAN is in Mode 0:<br><b>TXB2IE:</b> CAN Transmit Buffer 2 Interrupt Enable bit<br>1 = Enable Transmit Buffer 2 interrupt                                   |               |              |                       |                       |        |          |  |  |  |

|                      | <ul> <li>Disable Transmit Buffer 2 interrupt</li> </ul>                                 |                                                                                                                                                                 |               |              |                       |                       |        |          |  |  |  |

|                      | When CAN is in Mode 1 or 2:<br><b>TXBnIE:</b> CAN Transmit Buffer Interrupts Enable bit |                                                                                                                                                                 |               |              |                       |                       |        |          |  |  |  |

|                      | 0 = Disabl                                                                              | <ul> <li>1 = Enable transmit buffer interrupt; individual interrupt is enabled by TXBIE and BIE0</li> <li>0 = Disable all transmit buffer interrupts</li> </ul> |               |              |                       |                       |        |          |  |  |  |

| bit 3                |                                                                                         | <b>TXB1IE:</b> CAN Transmit Buffer 1 Interrupt Enable bit <sup>(1)</sup><br>1 = Enable Transmit Buffer 1 interrupt                                              |               |              |                       |                       |        |          |  |  |  |

|                      | 0 = Disabl                                                                              | 0 = Disable Transmit Buffer 1 interrupt                                                                                                                         |               |              |                       |                       |        |          |  |  |  |

| bit 2                | 1 = Enable                                                                              | <b>TXB0IE:</b> CAN Transmit Buffer 0 Interrupt Enable bit <sup>(1)</sup><br>1 = Enable Transmit Buffer 0 interrupt<br>0 = Disable Transmit Buffer 0 interrupt   |               |              |                       |                       |        |          |  |  |  |

| bit 1                |                                                                                         | <u>N is in Mode</u>                                                                                                                                             |               |              | abla bit              |                       |        |          |  |  |  |

|                      | 1 = Enable                                                                              | e Receive E                                                                                                                                                     | Buffer 1 inte |              |                       |                       |        |          |  |  |  |

|                      |                                                                                         | e Receive I<br>N is in Mode                                                                                                                                     |               | enupt        |                       |                       |        |          |  |  |  |

|                      |                                                                                         |                                                                                                                                                                 |               | terrupts Ena |                       | anablad by            |        |          |  |  |  |

|                      |                                                                                         | e all receive                                                                                                                                                   |               |              | i interrupt is        | enabled by            | DIEU   |          |  |  |  |

| bit 0                |                                                                                         | <u>N is in Mode</u><br>CAN Receiv                                                                                                                               |               | Interrupt En | able bit              |                       |        |          |  |  |  |

|                      |                                                                                         | e Receive E<br>e Receive F                                                                                                                                      |               |              |                       |                       |        |          |  |  |  |

|                      | 0 = Disable Receive Buffer 0 interrupt<br><u>When CAN is in Mode 1:</u>                 |                                                                                                                                                                 |               |              |                       |                       |        |          |  |  |  |

|                      | <b>Unimplemented:</b> Read as '0'<br>When CAN is in Mode 2:                             |                                                                                                                                                                 |               |              |                       |                       |        |          |  |  |  |

|                      |                                                                                         |                                                                                                                                                                 |               | errupt Enab  | le bit                |                       |        |          |  |  |  |

|                      |                                                                                         | e FIFO wate<br>e FIFO wat                                                                                                                                       |               |              |                       |                       |        |          |  |  |  |

|                      |                                                                                         |                                                                                                                                                                 |               |              | forced to '0'.        | _                     |        |          |  |  |  |

|                      |                                                                                         |                                                                                                                                                                 |               |              |                       |                       |        |          |  |  |  |

|                      | Legend:                                                                                 |                                                                                                                                                                 |               |              |                       |                       |        |          |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as   | s 'O'   |

|--------------------------------------------------------------------|---------|

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is | unknown |

#### 9.4 **IPR Registers**

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority registers (IPR1, IPR2). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

## REGISTER

| ER 9-10: | IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1                              |               |              |              |              |              |                |        |  |  |  |  |

|----------|-----------------------------------------------------------------------------|---------------|--------------|--------------|--------------|--------------|----------------|--------|--|--|--|--|

|          | R/W-1                                                                       | R/W-1         | R/W-1        | R/W-1        | R/W-1        | R/W-1        | R/W-1          | R/W-1  |  |  |  |  |

|          | PSPIP <sup>(1)</sup>                                                        | ADIP          | RCIP         | TXIP         | SSPIP        | CCP1IP       | TMR2IP         | TMR1IP |  |  |  |  |

|          | bit 7                                                                       |               |              | 1            |              |              | ļ              | bit 0  |  |  |  |  |

| bit 7    | PSPIP: Parallel Slave Port Read/Write Interrupt Priority bit <sup>(1)</sup> |               |              |              |              |              |                |        |  |  |  |  |

|          | 1 = High pi<br>0 = Low pr                                                   |               |              |              |              |              |                |        |  |  |  |  |

|          | Note 1:                                                                     | This bit is I | reserved on  | PIC18F2X8    | 0 devices; a | lways mainta | ain this bit s | et.    |  |  |  |  |

| bit 6    | ADIP: A/D Converter Interrupt Priority bit                                  |               |              |              |              |              |                |        |  |  |  |  |

|          | 1 = High pi<br>0 = Low pr                                                   |               |              |              |              |              |                |        |  |  |  |  |

| bit 5    | RCIP: EUS                                                                   | ART Recei     | ve Interrupt | Priority bit |              |              |                |        |  |  |  |  |

|          | 1 = High pi<br>0 = Low pr                                                   | •             |              |              |              |              |                |        |  |  |  |  |

| bit 4    | TXIP: EUSART Transmit Interrupt Priority bit                                |               |              |              |              |              |                |        |  |  |  |  |

|          | 1 = High p<br>0 = Low pr                                                    |               |              |              |              |              |                |        |  |  |  |  |

| bit 3    | SSPIP: Master Synchronous Serial Port Interrupt Priority bit                |               |              |              |              |              |                |        |  |  |  |  |

|          | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul>             |               |              |              |              |              |                |        |  |  |  |  |

| bit 2    | CCP1IP: CCP1 Interrupt Priority bit                                         |               |              |              |              |              |                |        |  |  |  |  |

|          | 1 = High p<br>0 = Low pr                                                    | •             |              |              |              |              |                |        |  |  |  |  |

| bit 1    | TMR2IP: TMR2 to PR2 Match Interrupt Priority bit                            |               |              |              |              |              |                |        |  |  |  |  |

|          | 1 = High pi<br>0 = Low pr                                                   | •             |              |              |              |              |                |        |  |  |  |  |

| bit 0    | TMR1IP: TMR1 Overflow Interrupt Priority bit                                |               |              |              |              |              |                |        |  |  |  |  |

|          | 1 = High pi<br>0 = Low pr                                                   | •             |              |              |              |              |                |        |  |  |  |  |

|          | Legend:                                                                     |               |              |              |              |              |                | ]      |  |  |  |  |

|          | R = Readal                                                                  | ole bit       | W = W        | /ritable bit | U = Unin     | nplemented   | bit, read as   | '0'    |  |  |  |  |

| R = Readable bit  | VV = VVritable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|--------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |