2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e-MMC

**Features**

## e·MMC<sup>TM</sup> Memory

### MTFC2GMVEA-0M WT, MTFC4GLVEA-0M WT, MTFC4GMVEA-1M WT, MTFC8GLVEA-1M WT, MTFC16GJVEC-2M WT, MTFC32GJVED-3M WT, MTFC64GJVDN-3M WT

#### **Features**

- MultiMediaCard (MMC) controller and NAND Flash

- 153- or 169-ball WFBGA/VFBGA/LFBGA (RoHS 6/6compliant)

- V<sub>CC</sub>: 2.7-3.6V

- V<sub>CCO</sub> (dual voltage): 1.65–1.95V; 2.7–3.6V

- Temperature ranges

- Operating temperature: -25°C to +85°C

- Storage temperature: -40°C to +85°C

- Typical current consumption

- Standby current: 110µA for 2GB, 120µA for 4GB, 8GB, 16GB; 140µA for 32G; 160µA for 64GB

- Active current (RMS): 70mA (2GB); 80mA (4GB, 8GB, 16GB, 32GB, 64GB)

### **MMC-Specific Features**

- JEDEC/MMC standard version 4.41-compliant (IEDEC Standard No. 84-A441) – SPI mode not supported (see www.jedec.org/sites/default/files/ docs/JESD84-A441.pdf)

- Advanced 11-signal interface

- x1, x4, and x8 I/Os, selectable by host

- MMC mode operation

- Command classes: class 0 (basic); class 2 (block read); class 4 (block write); class 5 (erase): class 6 (write protection); class 7 (lock card)

- MMC*plus*™ and MMC*mobile*™ protocols

- Temporary write protection

- 52 MHz clock speed (MAX)

- Boot operation (high-speed boot)

- Sleep mode

- Replay-protected memory block (RPMB)

- Secure erase and trim

- Hardware reset signal

- Multiple partitions with enhanced attribute

- Permanent and power-on write protection

- Double data rate (DDR) function

- High-priority interrupt (HPI)

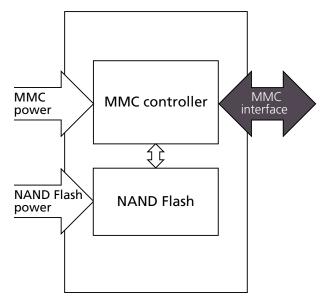

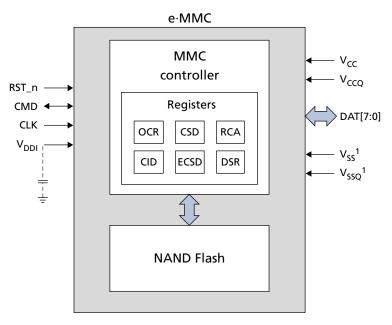

Figure 1: Micron e-MMC Device

#### **MMC-Specific Features (Continued)**

- Enhanced reliable write

- Configurable reliability settings

- Background operation

- Fully enhanced configurable

- Backward-compatible with previous MMC modes

- ECC and block management implemented

2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC Features

### e-MMC Performance

**Table 1: MLC Partition Performance**

|                  | Part Number                          |                                      |                                                             |       |  |  |  |

|------------------|--------------------------------------|--------------------------------------|-------------------------------------------------------------|-------|--|--|--|

| Condition        | MTFC2GMVEA-0M WT<br>MTFC4GLVEA-0M WT | MTFC4GMVEA-1M WT<br>MTFC8GLVEA-1M WT | MTFC16GJVEC-2M WT<br>MTFC32GJVED-3M WT<br>MTFC64GJVDN-3M WT | Units |  |  |  |

| Sequential write | 6.6                                  | 13.5                                 | 20                                                          | MB/s  |  |  |  |

| Sequential read  | 30                                   | 44                                   | 44                                                          | MB/s  |  |  |  |

Note: 1. Random access of 4KB chunk; sequential read access of 1MB chunk. Additional performance data, such as power consumption or timing for different device modes, will be provided in a separate document upon customer request.

### **Ordering Information**

### **Table 2: Ordering Information**

| Base Part Number  | Density | Package                 | NAND Flash<br>Type  | Shipping Media |

|-------------------|---------|-------------------------|---------------------|----------------|

| MTFC2GMVEA-0M WT  | 2GB     | 153-ball WFBGA          | 1 x 16Gb, MLC, 25nm | Tray           |

|                   |         | 11.5mm x 13.0mm x 0.8mm |                     | Tape and reel  |

| MTFC4GLVEA-0M WT  | 4GB     | 153-ball WFBGA          | 1 x 32Gb, MLC, 25nm | Tray           |

|                   |         | 11.5mm x 13.0mm x 0.8mm |                     | Tape and reel  |

| MTFC4GMVEA-1M WT  | 4GB     | 153-ball WFBGA          | 2 x 16Gb, MLC, 25nm | Tray           |

|                   |         | 11.5mm x 13.0mm x 0.8mm |                     | Tape and reel  |

| MTFC8GLVEA-1M WT  | 8GB     | 153-ball WFBGA          | 2 x 32Gb, MLC, 25nm | Tray           |

|                   |         | 11.5mm x 13.0mm x 0.8mm |                     | Tape and reel  |

| MTFC16GJVEC-2M WT | 16GB    | 169-ball WFBGA          | 2 x 64Gb, MLC, 25nm | Tray           |

|                   |         | 14.0mm x 18.0mm x 0.8mm |                     | Tape and reel  |

| MTFC32GJVED-3M WT | 32GB    | 169-ball VFBGA          | 4 x 64Gb, MLC, 25nm | Tray           |

|                   |         | 14.0mm x 18.0mm x 1.0mm |                     | Tape and reel  |

| MTFC64GJVDN-3M WT | 64GB    | 169-ball LFBGA          | 8 x 64Gb, MLC, 25nm | Tray           |

|                   |         | 14.0mm x 18.0mm x 1.4mm |                     | Tape and reel  |

#### 2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC Features

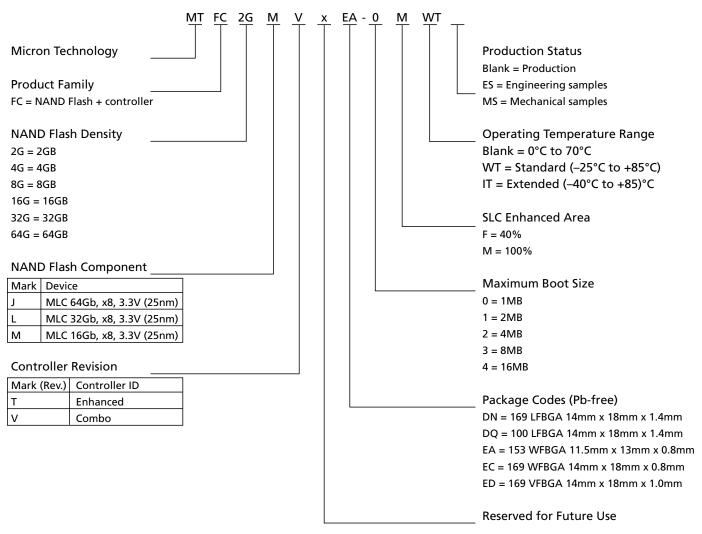

### **Part Numbering Information**

Micron<sup>®</sup> *e*·MMC memory devices are available in different configurations and densities. Verify valid part numbers by using Micron's part catalog search at www.micron.com. To compare features and specifications by device type, visit www.micron.com/products. Contact the factory for devices not found.

**Figure 2: Marketing Part Number Chart**

Note: 1. Not all combinations are necessarily available. For a list of available devices or for further information on any aspect of these products, please contact your nearest Micron sales office.

## 2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC General Description

## **General Description**

Micron *e*·MMC is a communication and mass data storage device that includes a Multi-MediaCard (MMC) interface, a NAND Flash component, and a controller on an advanced 11-signal bus, which is compliant with the MMC system specification. Its low cost, small size, Flash technology independence, and high data throughput make *e*·MMC ideal for embedded applications like set-top boxes, digital cameras/camcorders, digital TVs, and a variety other consumer products.

The nonvolatile e·MMC draws no power to maintain stored data, delivers high performance across a wide range of operating temperatures, and resists shock and vibration disruption.

# 2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC Signal Descriptions

## **Signal Descriptions**

**Table 3: Signal Descriptions**

| Symbol                        | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                           | Input  | Clock: Each cycle of the clock directs a transfer on the command line and on the data line(s). The frequency can vary between the minimum and the maximum clock frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RST_n                         | Input  | Reset: The RST_n signal is used by the host for resetting the device, moving the device to the pre-<br>idle state. By default, the RST_n signal is temporarily disabled in the device. The host must set ECSD<br>register byte 162, bits[1:0] to 0x1 to enable this functionality before the host can use it.                                                                                                                                                                                                                                                                                                              |

| CMD                           | 1/0    | Command: This signal is a bidirectional command channel used for command and response transfers. The CMD signal has two bus modes: open-drain mode and push-pull mode (see Operating Modes). Commands are sent from the MMC host to the device, and responses are sent from the device to the host.                                                                                                                                                                                                                                                                                                                        |

| DAT[7:0]                      | I/O    | Data I/O: These are bidirectional data signals. The DAT signals operate in push-pull mode. By default, after power-on or assertion of the RST_n signal, only DAT0 is used for data transfer. The MMC controller can configure a wider data bus for data transfer either using DAT[3:0] (4-bit mode) or DAT[7:0] (8-bit mode). e·MMC includes internal pull-up resistors for data lines DAT[7:1]. Immediately after entering the 4-bit mode, the device disconnects the internal pull-up resistors on the DAT[3:1] lines. Upon entering the 8-bit mode, the device disconnects the internal pull-ups on the DAT[7:1] lines. |

| V <sub>CC</sub>               | Supply | V <sub>CC</sub> : NAND interface (I/F) I/O and NAND Flash power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>CCQ</sub>              | Supply | V <sub>CCQ</sub> : e·MMC controller core and e·MMC I/F I/O power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>SS</sub> <sup>1</sup>  | Supply | V <sub>SS</sub> : NAND I/F I/O and NAND Flash ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SSQ</sub> <sup>1</sup> | Supply | V <sub>SSQ</sub> : e·MMC controller core and e·MMC I/F ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>DDI</sub>              |        | Internal voltage node: At least a $0.1\mu F$ capacitor is required to connect $V_{DDI}$ to ground. A $1\mu F$ capacitor is recommended. Do not tie to supply voltage or ground.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NC                            | _      | No connect: No internal connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RFU                           |        | Reserved for future use: No internal connection is present. Leave it floating externally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Note: 1.  $V_{SS}$  and  $V_{SSQ}$  are connected internally.

## 2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC 153-Ball Signal Assignments

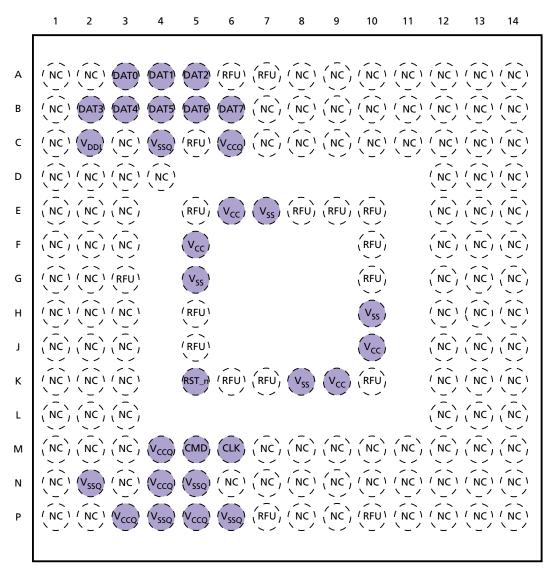

### **153-Ball Signal Assignments**

Figure 3: 153-Ball FBGA (top view, ball down)

Notes: 1. Some test pads on the device are not shown. They are not solder balls and are for Micron internal use only.

2. Some previous versions of the JEDEC product or mechanical specification had defined reserved for future use (RFU) balls as no connect (NC) balls. NC balls assigned in the previous specifications could have been connected to ground on the system board. To enable new feature introduction, some of these balls are assigned as RFU in the v4.4 mechanical specification. Any new PCB footprint implementations should use the new ball assignments and leave the RFU balls floating on the system board.

### 2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC 169-Ball Signal Assignments

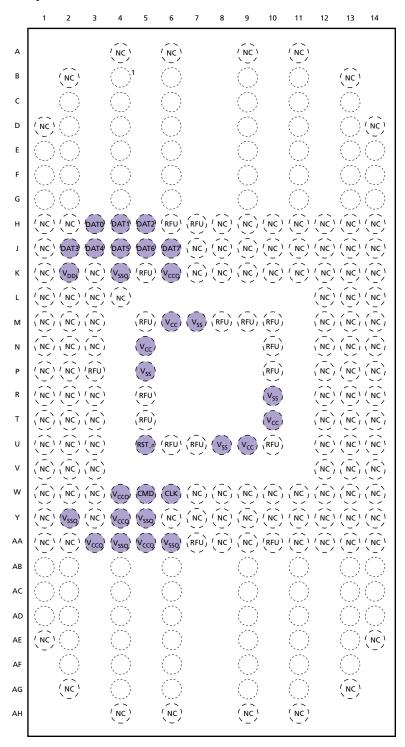

### **169-Ball Signal Assignments**

### Figure 4: 169-Ball FBGA (top view, ball down)

Notes: 1. Empty balls do not denote actual solder balls; they are position indicators only.

#### Micron Confidential and Proprietary

## 2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC 169-Ball Signal Assignments

- 2. Some test pads on the device are not shown. They are not solder balls and are for Micron internal use only.

- 3. Some previous versions of the JEDEC product or mechanical specification had defined reserved for future use (RFU) balls as no connect (NC) balls. NC balls assigned in the previous specifications could have been connected to ground on the system board. To enable new feature introduction, some of these balls are assigned as RFU in the v4.4 mechanical specification. Any new PCB footprint implementations should use the new ball assignments and leave the RFU balls floating on the system board.

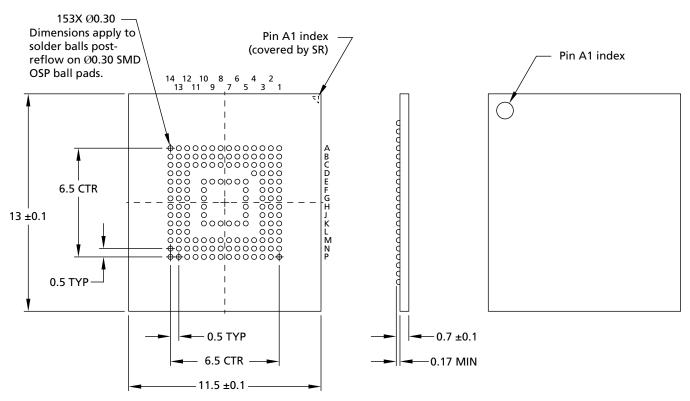

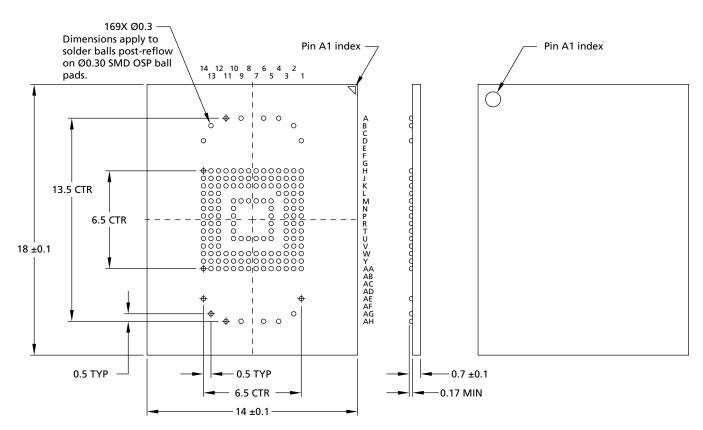

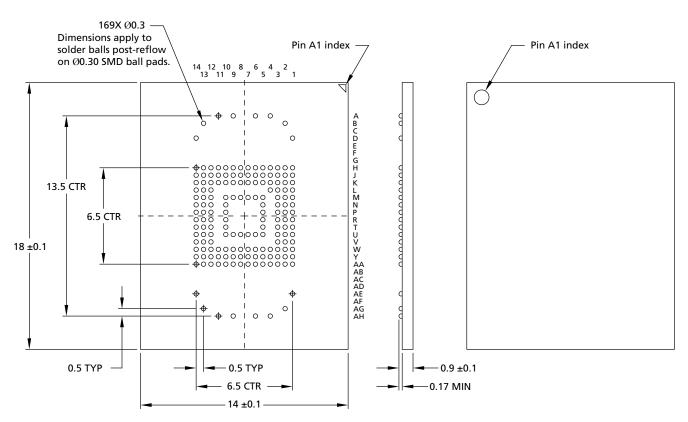

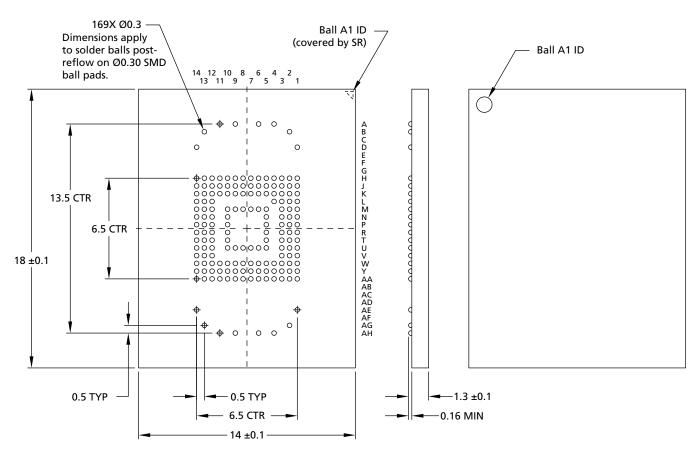

## **Package Dimensions**

Figure 5: 153-Ball WFBGA - 11.5mm x 13.0mm x 0.8mm (Package Code: EA)

Note: 1. Dimensions are in millimeters.

Figure 6: 169-Ball WFBGA - 14.0mm x 18.00mm x 0.8mm (Package Code: EC)

Note: 1. Dimensions are in millimeters.

Figure 7: 169-Ball VFBGA - 14.0mm x 18.00mm x 1.0mm (Package Code: ED)

Note: 1. Dimensions are in millimeters.

Figure 8: 169-Ball LFBGA - 14.0mm x 18.00mm x 1.4mm (Package Code: DN)

Note: 1. Dimensions are in millimeters.

#### 2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC Architecture

### **Architecture**

#### Figure 9: e-MMC Functional Block Diagram

Note: 1. V<sub>SS</sub> and V<sub>SSO</sub> are internally connected.

### **MMC Protocol Independent of NAND Flash Technology**

The MMC specification defines the communication protocol between a host and a device. The protocol is independent of the NAND Flash features included in the device. The device has an intelligent on-board controller that manages the MMC communication protocol.

The controller also handles block management functions such as logical block allocation and wear leveling. These management functions require complex algorithms and depend entirely on NAND Flash technology (generation or memory cell type).

The device handles these management functions internally, making them invisible to the host processor.

### **Defect and Error Management**

Micron *e*·MMC incorporates advanced technology for defect and error management. If a defective block is identified, the device completely replaces the defective block with one of the spare blocks. This process is invisible to the host and does not affect data space allocated for the user.

The device also includes a built-in error correction code (ECC) algorithm to ensure that data integrity is maintained.

To make the best use of these advanced technologies and ensure proper data loading and storage over the life of the device, the host must exercise the following precautions:

- Check the status after WRITE, READ, and ERASE operations.

- Avoid power-down during WRITE and ERASE operations.

## **CID Register**

The card identification (CID) register is 128 bits wide. It contains the device identification information used during the card identification phase as required by  $e \cdot \text{MMC}$  protocol. Each device is created with a unique identification number.

**Table 4: CID Register Field Parameters**

| Name                  | Field | Width | CID Bits  | CID Value                                                |

|-----------------------|-------|-------|-----------|----------------------------------------------------------|

| Manufacturer ID       | MID   | 8     | [127:120] | FEh                                                      |

| Reserved              | _     | 6     | [119:114] | _                                                        |

| Card/BGA              | CBX   | 2     | [113:112] | 01h                                                      |

| OEM/application ID    | OID   | 8     | [111:104] | -                                                        |

| Product name          | PNM   | 48    | [103:56]  | MMC02G<br>MMC04G<br>MMC08G<br>MMC16G<br>MMC32G<br>MMC64G |

| Product revision      | PRV   | 8     | [55:48]   | -                                                        |

| Product serial number | PSN   | 32    | [47:16]   | -                                                        |

| Manufacturing date    | MDT   | 8     | [15:8]    | _                                                        |

| CRC7 checksum         | CRC   | 7     | [7:1]     | _                                                        |

| Not used; always 1    | _     | 1     | 0         | _                                                        |

### **CSD Register**

The card-specific data (CSD) register provides information about accessing the device contents. The CSD register defines the data format, error correction type, maximum data access time, and data transfer speed, as well as whether the DS register can be used. The programmable part of the register (entries marked with W or E in the following table) can be changed by the PROGRAM\_CSD (CMD27) command.

**Table 5: CSD Register Field Parameters**

| Name                                               |                | Field                                                                                                                        | Width | Cell<br>Type <sup>1</sup> | CSD<br>Bits | CSD<br>Value |

|----------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------|-------------|--------------|

| CSD structure                                      | CSD_STRUCTURE  | rieiu                                                                                                                        | 2     | R                         | [127:126]   | 03h          |

|                                                    | _              |                                                                                                                              |       |                           |             |              |

| System specification version                       | SPEC_VERS      |                                                                                                                              | 4     | R                         | [125:122]   | 4h           |

| Reserved <sup>2</sup>                              |                |                                                                                                                              | 2     | TBD                       | [121:120]   | -            |

| Data read access time 1                            | TAAC           |                                                                                                                              | 8     | R                         | [119:112]   | 4Fh          |

| Data read access time 2 in CLK cycles (NSAC × 100) | NSAC           |                                                                                                                              | 8     | R                         | [111:104]   | 01h          |

| Maximum bus clock frequency                        | TRAN_SPEED     |                                                                                                                              | 8     | R                         | [103:96]    | 32h          |

| Card command classes                               | ccc            |                                                                                                                              | 12    | R                         | [95:84]     | 0F5h         |

| Maximum read data block                            | READ_BL_LEN    | MTFC2GMVEA-0M WT                                                                                                             | 4     | R                         | [83:80]     | 0Ah          |

| length                                             |                | MTFC4GLVEA-0M WT,<br>MTFC4GMVEA-1M WT,<br>MTFC8GLVEA-1M WT,<br>MTFC16GJVEC-2M WT,<br>MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT |       |                           |             | 09h          |

| Partial blocks for reads supported                 | READ_BL_PARTIA | READ_BL_PARTIAL                                                                                                              |       | R                         | 79          | 0h           |

| Write block misalignment                           | WRITE_BLK_MISA | ALIGN                                                                                                                        | 1     | R                         | 78          | 0h           |

| Read block misalignment                            | READ_BLK_MISA  | LIGN                                                                                                                         | 77    | R                         | 77          | 0h           |

| DS register implemented                            | DSR_IMP        |                                                                                                                              | 1     | R                         | 76          | 1h           |

| Reserved                                           |                | _                                                                                                                            | 2     | R                         | [75:74]     | _            |

| Device size                                        | C_SIZE         | MTFC2GMVEA-0M WT                                                                                                             | 12    | R                         | [73:62]     | E4Fh         |

|                                                    |                | MTFC4GLVEA-0M WT,<br>MTFC4GMVEA-1M WT,<br>MTFC8GLVEA-1M WT,<br>MTFC16GJVEC-2M WT,<br>MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT |       |                           |             | FFFh         |

| Maximum read current at V <sub>DD,min</sub>        | VDD_R_CURR_MI  | VDD_R_CURR_MIN                                                                                                               |       | R                         | [61:59]     | 7h           |

| Maximum read current at V <sub>DD,max</sub>        | VDD_R_CURR_MA  | VDD_R_CURR_MAX                                                                                                               |       | R                         | [58:56]     | 7h           |

| Maximum write current at V <sub>DD,min</sub>       | VDD_W_CURR_M   | IIN                                                                                                                          | 3     | R                         | [55:53]     | 7h           |

### **Table 5: CSD Register Field Parameters (Continued)**

| Name                                         |                 | Field                                                         | Width | Cell<br>Type <sup>1</sup> | CSD<br>Bits | CSD<br>Value |

|----------------------------------------------|-----------------|---------------------------------------------------------------|-------|---------------------------|-------------|--------------|

| Maximum write current at V <sub>DD,max</sub> | VDD_W_CURR_M    | AX                                                            | 3     | R                         | [52:50]     | 7h           |

| Device size multiplier                       | C_SIZE_MULT     |                                                               | 3     | R                         | [49:47]     | 7h           |

| Erase group size                             | ERASE_GRP_SIZE  |                                                               | 5     | R                         | [46:42]     | 1Fh          |

| Erase group size multiplier                  | ERASE_GRP_MULT  | Γ                                                             | 5     | R                         | [41:37]     | 1Fh          |

| Write protect group size                     | WP_GRP_SIZE     | MTFC2GMVEA-0M WT                                              | 5     | R                         | [36:32]     | 03h          |

|                                              |                 | MTFC4GLVEA-0M WT,<br>MTFC4GMVEA-1M WT                         |       |                           |             | 07h          |

|                                              |                 | MTFC8GLVEA-1M WT                                              | 7     |                           |             | 0Fh          |

|                                              |                 | MTFC16GJVEC-2M WT,<br>MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT |       |                           |             | 1Fh          |

| Write protect group enable                   | WP_GRP_ENABLE   | WP_GRP_ENABLE                                                 |       | R                         | 31          | 1h           |

| Manufacturer default ECC                     | DEFAULT_ECC     |                                                               | 2     | R                         | [30:29]     | 0h           |

| Write-speed factor                           | R2W_FACTOR      |                                                               | 3     | R                         | [28:26]     | 2h           |

| Maximum write data block length              | WRITE_BL_LEN    |                                                               | 4     | R                         | [25:22]     | 9h           |

| Partial blocks for writes supported          | WRITE_BL_PARTIA | AL                                                            | 1     | R                         | 21          | 0h           |

| Reserved                                     |                 | -                                                             | 4     | R                         | [20:17]     | _            |

| Content protection application               | CONTENT_PROT_A  | APP                                                           | 1     | R                         | 16          | 0h           |

| File-format group                            | FILE_FORMAT_GR  | Р                                                             | 1     | R/W                       | 15          | 0h           |

| Copy flag (OTP)                              | COPY            |                                                               | 1     | R/W                       | 14          | 0h           |

| Permanent write protection                   | PERM_WRITE_PRO  | OTECT                                                         | 1     | R/W                       | 13          | 0h           |

| Temporary write protection                   | TMP_WRITE_PRO   | TECT                                                          | 1     | R/W/E                     | 12          | 0h           |

| File format                                  | FILE_FORMAT     |                                                               | 2     | R/W                       | [11:10]     | 0h           |

| ECC                                          | ECC             |                                                               | 2     | R/W/E                     | [9:8]       | 0h           |

| CRC                                          | CRC             |                                                               | 7     | R/W/E                     | [7:1]       | _            |

| Not used; always 1                           |                 | _                                                             | 1     | _                         | 0           | 1h           |

Notes: 1. R = Read-only

R/W = One-time programmable and readable

R/W/E = Multiple writable with value kept after a power cycle, assertion of the RST\_n

signal, and any CMD0 reset, and readable

TBD = To be determined

2. Reserved bits should be read as 0.

### **ECSD Register**

The 512-byte extended card-specific data (ECSD) register defines device properties and selected modes. The most significant 320 bytes are the properties segment. This segment defines device capabilities and cannot be modified by the host. The lower 192 bytes are the modes segment. The modes segment defines the configuration in which the device is working. The host can change the properties of modes segments using the SWITCH command.

**Table 6: ECSD Register Field Parameters**

| Name                                                            |                               | Field                                   | Size<br>(Bytes) | Cell<br>Type <sup>1</sup> | ECSD<br>Bytes | ECSD<br>Value |

|-----------------------------------------------------------------|-------------------------------|-----------------------------------------|-----------------|---------------------------|---------------|---------------|

| Properties Segment                                              |                               |                                         |                 |                           |               |               |

| Reserved <sup>2</sup>                                           |                               | _                                       | 7               | _                         | [511:505]     | _             |

| Supported command sets                                          | S_CMD_SET                     |                                         | 1               | R                         | 504           | 1h            |

| HPI features                                                    | HPI_FEATURES                  |                                         | 1               | R                         | 503           | 3h            |

| Background operations support                                   | BKOPS_SUPPORT                 |                                         | 1               | R                         | 502           | 1h            |

| Reserved                                                        |                               | _                                       | 255             | _                         | [501:247]     | _             |

| Background operations status                                    | BKOPS_STATUS                  |                                         | 1               | R                         | 246           | 0h            |

| Number of correctly program-<br>med sectors                     | CORRECTLY_PRG_<br>SECTORS_NUM |                                         | 4               | R                         | [245:242]     | -             |

| First initialization time after                                 | INI_TIMEOUT_PA                | MTFC2GMVEA-0M WT                        | 1               | R                         | 241           | 7Ah           |

| partitioning                                                    |                               | MTFC4GLVEA-0M WT                        |                 |                           |               | F6h           |

| (first CMD1 to device ready)                                    |                               | MTFC4GMVEA-1M WT                        |                 |                           |               | 7Ah           |

|                                                                 |                               | MTFC8GLVEA-1M WT,<br>MTFC16GJVEC-2M WT  |                 |                           |               | F6h           |

|                                                                 |                               | MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT |                 |                           |               | FFh           |

| Reserved                                                        |                               | _                                       | 1               | 1                         | 240           | _             |

| Power class for 52 MHz, DDR at 3.6V <sup>3</sup>                | PWR_CL_DDR_52_                | 360                                     | 1               | R                         | 239           | 0h            |

| Power class for 52 MHz, DDR at 1.95V <sup>3</sup>               | PWR_CL_DDR_52_                | 195                                     | 1               | R                         | 238           | 0h            |

| Reserved                                                        |                               | _                                       | 2               | -                         | [237:236]     | _             |

| Minimum write performance<br>for 8-bit at 52 MHz in DDR<br>mode | MIN_PERF_DDR_W_8_52           |                                         | 1               | R                         | 235           | 0h            |

| Minimum read performance for<br>8-bit at 52 MHz in DDR mode     | MIN_PERF_DDR_R_8_52           |                                         | 1               | R                         | 234           | 0h            |

| Reserved                                                        |                               | _                                       | 1               | -                         | 233           | _             |

|                                                                 |                               |                                         |                 |                           | 1             |               |

| Name                    |                 | Field                                                                          | Size<br>(Bytes) | Cell<br>Type <sup>1</sup> | ECSD<br>Bytes | ECSD<br>Value |

|-------------------------|-----------------|--------------------------------------------------------------------------------|-----------------|---------------------------|---------------|---------------|

| TRIM multiplier         | TRIM_MULT       | MTFC2GMVEA-0M WT<br>MTFC4GLVEA-0M WT,<br>MTFC4GMVEA-1M WT,<br>MTFC8GLVEA-1M WT | 1               | R                         | 232           | 06h           |

|                         |                 | MTFC16GJVEC-2M WT,<br>MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT                  |                 |                           |               | 0Fh           |

| Secure feature support  | SEC_FEATURE_SUF | PPORT                                                                          | 1               | R                         | 231           | 15h           |

| SECURE ERASE multiplier | SEC_ERASE_MULT  | MTFC2GMVEA-0M WT<br>MTFC4GLVEA-0M WT,<br>MTFC4GMVEA-1M WT,<br>MTFC8GLVEA-1M WT | 1               | R                         | 230           | 02h           |

|                         |                 | MTFC16GJVEC-2M WT,<br>MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT                  |                 |                           |               | 06h           |

| SECURE TRIM multiplier  | SEC_TRIM_MULT   | MTFC2GMVEA-0M WT<br>MTFC4GLVEA-0M WT,<br>MTFC4GMVEA-1M WT,<br>MTFC8GLVEA-1M WT | 1               | R                         | 229           | 03h           |

|                         |                 | MTFC16GJVEC-2M WT,<br>MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT                  |                 |                           |               | 09h           |

| Boot information        | BOOT_INFO       |                                                                                | 1               | R                         | 228           | 7h            |

| Reserved                |                 | -                                                                              | 1               | -                         | 227           | _             |

| Boot partition size     | BOOT_SIZE_MULT  | MTFC2GMVEA-0M WT,<br>MTFC4GLVEA-0M WT                                          | 1               | R                         | 226           | 08h           |

|                         |                 | MTFC4GMVEA-1M WT,<br>MTFC8GLVEA-1M WT                                          |                 |                           |               | 10h           |

|                         |                 | MTFC16GJVEC-2M WT                                                              |                 |                           |               | 20h           |

|                         |                 | MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT                                        |                 |                           |               | 40h           |

| Access size             | ACC_SIZE        | ACC_SIZE MTFC2GMVEA-0M WT, 1 R 225<br>MTFC4GLVEA-0M WT                         | 225             | 05h                       |               |               |

|                         |                 | MTFC4GMVEA-1M WT,<br>MTFC8GLVEA-1M WT                                          |                 |                           |               | 06h           |

|                         |                 | MTFC16GJVEC-2M WT,<br>MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT                  |                 |                           |               | 07h           |

|                                                                         |                 |                                                               | Size    | Cell              | ECSD      | ECSD      |

|-------------------------------------------------------------------------|-----------------|---------------------------------------------------------------|---------|-------------------|-----------|-----------|

| Name                                                                    |                 | Field                                                         | (Bytes) | Type <sup>1</sup> | Bytes     | Value     |

| High-capacity erase unit size                                           | HC_ERASE_GRP_S  | MTFC2GMVEA-0M WT                                              | 1       | R                 | 224       | 00h       |

|                                                                         | IZE             | MTFC4GLVEA-0M WT                                              | ]       |                   |           | 04h       |

|                                                                         |                 | MTFC4GMVEA-1M WT,                                             | ]       |                   |           | 08h       |

|                                                                         |                 | MTFC8GLVEA-1M WT                                              |         |                   |           |           |

|                                                                         |                 | MTFC16GJVEC-2M WT,<br>MTFC32GJVED-3M WT,<br>MTFC64GJVDN-3M WT |         |                   |           | 10h       |

| High-capacity erase timeout                                             | ERASE_TIMEOUT_  | MULT                                                          | 1       | R                 | 223       | 01h       |

| Reliable write-sector count                                             | REL_WR_SEC_C    |                                                               | 1       | R                 | 222       | 01h       |

| High-capacity write protect                                             | HC_WP_GRP_SIZE  | MTFC2GMVEA-0M WT                                              | 1       | R                 | 221       | 00h       |

| group size                                                              |                 | MTFC4GLVEA-0M WT                                              |         |                   |           | 02h       |

|                                                                         |                 | MTFC4GMVEA-1M WT                                              |         |                   |           | 01h       |

|                                                                         |                 | MTFC8GLVEA-1M WT,                                             |         |                   |           | 02h       |

|                                                                         |                 | MTFC16GJVEC-2M WT                                             |         |                   |           |           |

|                                                                         |                 | MTFC32GJVED-3M WT                                             |         |                   |           | 04h       |

|                                                                         |                 | MTFC64GJVDN-3M WT                                             |         |                   |           | 08h       |

| Sleep current (V <sub>CC</sub> )                                        | S_C_VCC         |                                                               | 1       | R                 | 220       | 08h       |

| Sleep current (V <sub>CCQ</sub> )                                       | S_C_VCCQ        |                                                               | 1       | R                 | 219       | 08h       |

| Reserved                                                                |                 | _                                                             | 1       | _                 | 218       | _         |

| Sleep/awake timeout                                                     | S_A_TIMEOUT     |                                                               | 1       | R                 | 217       | 10h       |

| Reserved                                                                |                 | _                                                             | 1       | _                 | 216       | _         |

| Sector count                                                            | SEC_COUNT       | MTFC2GMVEA-0M WT                                              | 4       | R                 | [215:212] | 00000000h |

|                                                                         |                 | MTFC4GLVEA-0M WT                                              |         |                   |           | 00750000h |

|                                                                         |                 | MTFC4GMVEA-1M WT                                              |         |                   |           | 00728000h |

|                                                                         |                 | MTFC8GLVEA-1M WT                                              |         |                   |           | 00EA0000h |

|                                                                         |                 | MTFC16GJVEC-2M WT                                             |         |                   |           | 01D40000h |

|                                                                         |                 | MTFC32GJVED-3M WT                                             |         |                   |           | 03B20000h |

|                                                                         |                 | MTFC64GJVDN-3M WT                                             |         |                   |           | 07700000h |

| Reserved                                                                |                 | _                                                             | 1       | _                 | 211       | _         |

| Minimum write performance for 8-bit at 52 MHz                           | MIN_PERF_W_8_52 | 2                                                             | 1       | R                 | 210       | 08h       |

| Minimum read performance for 8-bit at 52 MHz                            | MIN_PERF_R_8_52 |                                                               | 1       | R                 | 209       | 08h       |

| Minimum write performance<br>for 8-bit at 26 MHz and 4-bit at<br>52 MHz | MIN_PERF_W_8_26 | 6_4_52                                                        | 1       | R                 | 208       | 08h       |

| Minimum read performance for<br>8-bit at 26 MHz and 4-bit at 52<br>MHz  | MIN_PERF_R_8_26 | _4_52                                                         | 1       | R                 | 207       | 08h       |

|                                               |                       | Size    | Cell              | ECSD  | ECSD  |

|-----------------------------------------------|-----------------------|---------|-------------------|-------|-------|

| Name                                          | Field                 | (Bytes) | Type <sup>1</sup> | Bytes | Value |

| Minimum write performance for 4-bit at 26 MHz | MIN_PERF_W_4_26       | 1       | R                 | 206   | 08h   |

| Minimum read performance for 4-bit at 26 MHz  | MIN_PERF_R_4_26       | 1       | R                 | 205   | 08h   |

| Reserved                                      | -                     | 1       | _                 | 204   | _     |

| Power class for 26 MHz at 3.6V <sup>3</sup>   | PWR_CL_26_360         | 1       | R                 | 203   | 00h   |

| Power class for 52 MHz at 3.6V <sup>3</sup>   | PWR_CL_52_360         | 1       | R                 | 202   | 00h   |

| Power class for 26 MHz at 1.95V <sup>3</sup>  | PWR_CL_26_195         | 1       | R                 | 201   | 00h   |

| Power class for 52 MHz at 1.95V <sup>3</sup>  | PWR_CL_52_195         | 1       | R                 | 200   | 00h   |

| Partition switching timing                    | PARTITION_SWITCH_TIME | 1       | R                 | 199   | 1h    |

| Out-of-interrupt busy timing                  | OUT_OF_INTERRUPT_TIME | 1       | R                 | 198   | 02h   |

| Reserved                                      | -                     | 1       | _                 | 197   | _     |

| Card type                                     | CARD_TYPE             | 1       | R                 | 196   | 07h   |

| Reserved                                      | -                     | 1       | _                 | 195   | _     |

| CSD structure version                         | CSD_STRUCTURE         | 1       | R                 | 194   | 2h    |

| Reserved                                      | -                     | 1       | _                 | 193   | -     |

| Extended CSD revision                         | EXT_CSD_REV           | 1       | R                 | 192   | 5h    |

| Modes Segment                                 |                       |         |                   |       |       |

| Command set                                   | CMD_SET               | 1       | R/W/E_P           | 191   | 0h    |

| Reserved                                      | -                     | 1       | _                 | 190   | _     |

| Command set revision                          | CMD_SET_REV           | 1       | R                 | 189   | 0h    |

| Reserved                                      | -                     | 1       | _                 | 188   | _     |

| Power class                                   | POWER_CLASS           | 1       | R/W/E_P           | 187   | 0h    |

| Reserved                                      | -                     | 1       | _                 | 186   | _     |

| High-speed interface timing                   | HS_TIMING             | 1       | R/W/E_P           | 185   | 0h    |

| Reserved                                      | -                     | 1       | _                 | 184   | _     |

| Bus width mode                                | BUS_WIDTH             | 1       | W/E_P             | 183   | 0h    |

| Reserved                                      | -                     | 1       | _                 | 182   | _     |

| Erased memory content                         | ERASED_MEM_CONT       | 1       | R                 | 181   | 0h    |

| Reserved                                      | -                     | 1       | _                 | 180   | _     |

| Partition configuration                       | PARTITION_CONFIG      | 1       | R/W/E,<br>R/W/E_P | 179   | 0h    |

| Boot configuration protection                 | BOOT_CONFIG_PROT      | 1       | R/W,<br>R/W/C_P   | 178   | 0h    |

| Boot bus width                                | BOOT_BUS_WIDTH        | 1       | R/W/E             | 177   | 0h    |

| Reserved                                      | -                     | 1       | _                 | 176   | _     |

| N                                               |                 | etald                                  | Size    | Cell                        | ECSD      | ECSD             |

|-------------------------------------------------|-----------------|----------------------------------------|---------|-----------------------------|-----------|------------------|

| Name                                            | EDAGE CROUP B   | Field                                  | (Bytes) | Type <sup>1</sup>           | Bytes     | Value            |

| High-density erase group defi-<br>nition        | ERASE_GROUP_D   | 1                                      | R/W/E_P | 175                         | 00h       |                  |

| Reserved                                        |                 | -                                      | 1       | _                           | 174       | -                |

| Boot area write protection register             | BOOT_WP         |                                        | 1       | R/W,<br>R/W/C_P             | 173       | 0h               |

| Reserved                                        |                 | _                                      | 1       | _                           | 172       | _                |

| User write protection register                  | USER_WP         |                                        | 1       | R/W,<br>R/W/C_P,<br>R/W/E_P | 171       | 0h               |

| Reserved                                        |                 | _                                      | 1       | _                           | 170       | -                |

| Firmware configuration                          | FW_CONFIG       |                                        | 1       | R/W                         | 169       | 0h               |

| RPMB size                                       | RPMB_SIZE_MULT  | -                                      | 1       | R                           | 168       | 1h               |

| Write reliability setting register <sup>3</sup> | WR_REL_SET      |                                        | 1       | R/W                         | 167       | 00h <sup>4</sup> |

| Write reliability parameter register            | WR_REL_PARAM    |                                        | 1       | R                           | 166       | 05h              |

| Reserved                                        | -               |                                        | 1       | _                           | 165       | _                |

| Manually start background operations            | BKOPS_START     |                                        | 1       | W/E_P                       | 164       | -                |

| Enable background operations handshake          | BKOPS_EN        |                                        | 1       | R/W                         | 163       | 0h               |

| Hardware reset function                         | RST_n_FUNCTION  |                                        | 1       | R/W                         | 162       | 0h               |

| HPI management                                  | HPI_MGMT        |                                        | 1       | R/W/E_P                     | 161       | 0h               |

| Partitioning support                            | PARTITIONING_SU | JPPORT                                 | 1       | R                           | 160       | 3h               |

| Maximum enhanced area size                      | MAX_ENH_SIZE_   | MTFC2GMVEA-0M WT                       | 3       | R                           | [159:157] | 0001CAh          |

|                                                 | MULT            | MTFC4GLVEA-0M WT                       |         |                             |           | 0001D4h          |

|                                                 |                 | MTFC4GMVEA-1M WT                       |         |                             |           | 0001CAh          |

|                                                 |                 | MTFC8GLVEA-1M WT,<br>MTFC16GJVEC-2M WT |         |                             |           | 0001D4h          |

|                                                 |                 | MTFC32GJVED-3M WT                      |         |                             |           | 0001D9h          |

|                                                 |                 | MTFC64GJVDN-3M WT                      |         |                             |           | 0001DCh          |

| Partitions attribute                            | PARTITIONS_ATTR | RIBUTE                                 | 1       | R/W                         | 156       | 0h               |

| Partitioning setting                            | PARTITION_SETTI | NG_COMPLETED                           | 1       | R/W                         | 155       | 0h               |

| General-purpose partition size                  | GP_SIZE_MULT    |                                        |         | R/W                         | [154:143] | 0h               |

| Enhanced user data area size                    | ENH_SIZE_MULT   |                                        | 3       | R/W                         | [142:140] | 0h               |

| Enhanced user data start address                | ENH_START_ADD   | R                                      | 4       | R/W                         | [139:136] | 0h               |

| Reserved                                        |                 | _                                      | 1       | _                           | 135       | -                |

| Bad block management mode                       | SEC_BAD_BLK_M   | GMNT                                   | 1       | R/W                         | 134       | 0h               |

#### **Table 6: ECSD Register Field Parameters (Continued)**

| Name     | Field | Size<br>(Bytes) | Cell<br>Type <sup>1</sup> | ECSD<br>Bytes | ECSD<br>Value |

|----------|-------|-----------------|---------------------------|---------------|---------------|

| Reserved | _     | 134             | _                         | [133:0]       | _             |

Notes: 1. R = Read-only

R/W = One-time programmable and readable

R/W/E = Multiple writable with the value kept after a power cycle, assertion of the RST\_n signal, and any CMD0 reset, and readable

R/W/C\_P = Writable after the value is cleared by a power cycle and assertion of the RST\_n signal (the value not cleared by CMD0 reset) and readable

R/W/E\_P = Multiple writable with the value reset after a power cycle, assertion of the RST\_n signal, and any CMD0 reset, and readable

W/E\_P = Multiple writable with the value reset after power cycle, assertion of the RST\_n signal, and any CMD0 reset, and not readable

TBD = To be determined

- 2. Reserved bits should be read as 0.

- 3. Micron has tested power failure under best application knowledge conditions with positive results. Customers may request a dedicated test for their specific application condition

- 4. Can be set to 1Fh to enable reliability settings. This byte is one-time programmable.

## 2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC DC Electrical Specifications – Device Power

## **DC Electrical Specifications – Device Power**

The device current consumption for various device configurations is defined in the power class fields of the ECSD register.

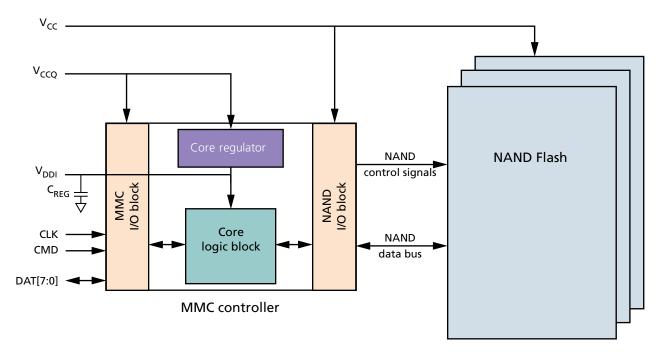

$V_{CC}$  is used for the NAND Flash device and its interface voltage;  $V_{CCQ}$  is used for the controller and the  $e \cdot MMC$  interface voltage. A  $C_{REG}$  capacitor must be connected to the  $V_{DDI}$  terminal to stabilize regulator output on the system.

**Figure 10: Device Power Diagram**

**Note:** Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not guaranteed. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**Table 7: Absolute Maximum Ratings**

| Parameters              | Symbol           | Min  | Max | Unit |

|-------------------------|------------------|------|-----|------|

| Voltage input           | V <sub>IN</sub>  | -0.6 | 4.6 | V    |

| V <sub>CC</sub> supply  | V <sub>CC</sub>  | -0.6 | 4.6 | V    |

| V <sub>CCQ</sub> supply | V <sub>CCQ</sub> | -0.6 | 4.6 | V    |

| Storage temperature     | T <sub>STG</sub> | -40  | 85  | °C   |

Note: 1. Voltage on any pin relative to V<sub>SS</sub>.

# 2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC DC Electrical Specifications – Device Power

### **Table 8: Operating Conditions**

| Parameters                          | Symbol                        | Min  | Тур | Max  | Unit |

|-------------------------------------|-------------------------------|------|-----|------|------|

| Supply voltage (controller and I/O) | V <sub>CCQ</sub>              | 1.65 | _   | 1.95 | V    |

|                                     |                               | 2.70 | -   | 3.6  |      |

| Supply voltage (NAND)               | V <sub>CC</sub>               | 2.70 | -   | 3.6  | V    |

| Supply power-on for 3.3V            | <sup>t</sup> PRUH             | _    | -   | 35   | ms   |

| Supply power-on for 1.8V            | <sup>t</sup> PRUL             | _    | -   | 25   | ms   |

| V <sub>DDI</sub> capacitance value  | C <sub>REG</sub> <sup>1</sup> | 0.1  | _   | _    | μF   |

| Operating temperature               | T <sub>A</sub>                | -25  | -   | 85   | °C   |

Note: 1. C<sub>REG</sub> is used to stabilize the internal regulator output to controller core logic voltages. Micron recommends using the following capacitor values:

$C_{VCC}$  (capacitor for  $V_{CC}$ ) = 4.3 $\mu$ F.  $C_{VCCQ}$  (capacitor for  $V_{CCQ}$ ) = 4.3 $\mu$ F

$C_{REG} = 1.0 \mu F.$

2GB, 4GB, 8GB, 16GB, 32GB, 64GB: e·MMC Revision History

### **Revision History**

Rev. A - 06/12

· Initial release

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900 www.micron.com/productsupport Customer Comment Line: 800-932-4992 Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein. Although considered final, these specifications are subject to change, as further product development and data characterization sometimes occur.