### 1.1. MCU Interface

MCU Interface consist of 8 data pin and 5 control pins. The pin assignment is summarized in Table 1-1.

| Pins      | Data/Command Interface |    |    |     |      |    |    | 9  |   | Co   | ontrol Sign | al   |      |

|-----------|------------------------|----|----|-----|------|----|----|----|---|------|-------------|------|------|

| Interface | D7                     | D6 | D5 | D4  | D3   | D2 | D1 | D0 | E | R/W# | CS#         | D/C# | WAIT |

| 8b/6800   |                        |    |    | D[7 | 7:0] |    |    |    | E | R/W# | CS#         | D/C# | wait |

Table 1-1 : MCU interface assignment under different bus interface mode

## 1.1.1 MCU Paralell 6800-series Interface

The parallel interface consists of 8 bi-directional data pins (D[7:0]), R/W#, D/C#, E and CS#. A LOW in R/W# indicates WRITE operation and HIGH in R/W# indicates READ operation. A LOW in D/C# indicates COMMAND read/write and HIGH in D/C# indicates DATA read/write. The E input serves as data latch signal while CS# is LOW. Data is latched at the falling edge of E signal.

| Function      | Е            | R/W# | CS# | D/C# | WAIT |

|---------------|--------------|------|-----|------|------|

| Write command | $\downarrow$ | L    | L   | L    | L    |

| Read status   | $\downarrow$ | Н    | L   | L    | L    |

| Write data    | $\downarrow$ | L    | L   | Н    | L    |

| Read data     | $\downarrow$ | Н    | L   | Н    | L    |

#### Table 1-2 : Control pins of 6800 interface

#### Note

(1)  $\downarrow$  stands for falling edge of signal (2) H stands for HIGH in signal

$\left( 3\right) L$  stands for LOW in signal

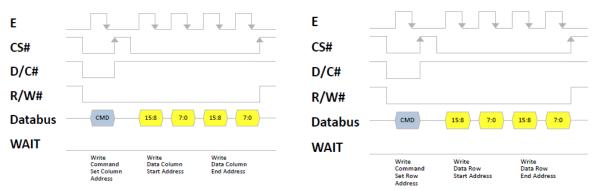

# Figure 1-1 : Set Column & Row Address procedure – set a start- and end address of column & row

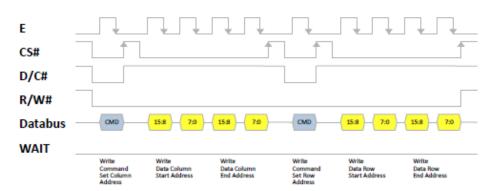

#### Figure 1-2 : Set Column & Row Address in one flow procedure

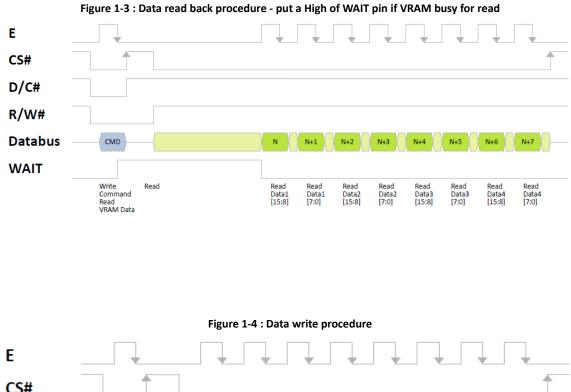

In order to match the internally operating frequency of display RAM with that of the microprocessor, some waiting of extern read processing is internally performed which requires the insertion of a high at WAIT pin before the first actual display data can read. This is shown in Figure 1-3.

#### 1.1.2 Databus to VRAM mapping

#### Table 1-3 : Data bus to VRAM mapping

| Write Data |             |             |    | Data Bus |    |    |    |    |    |    |  |

|------------|-------------|-------------|----|----------|----|----|----|----|----|----|--|

| Bus Width  | Color Depth | Input Order | D7 | D6       | D5 | D4 | D3 | D2 | D1 | D0 |  |

| 8 bits     | 65K         | 1st         | B4 | В3       | B2 | B1 | в0 | G5 | G4 | G3 |  |

| o bits     | 700         | 2nd         | G2 | G1       | G0 | R4 | R3 | R2 | R1 | RO |  |

# 2.1 Command

## 2.1.1 Basic Commands

|                       |                                                                              |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            | Command Table           | e                                                                                                                               |

|-----------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| D/C#                  | HEX                                                                          | D7                                                                          | D6                                                                 | D5                                                                          | D4                                                                 | D3                                                                          | D2                                                                   | D1                                                       | D0                                                         | Command                 | Description                                                                                                                     |

| 0<br>1                | 0x15<br>А <sub>н</sub>                                                       | 0<br>A <sub>15</sub>                                                        | 0<br>A <sub>14</sub>                                               | 0<br>A <sub>13</sub>                                                        | 1<br>A <sub>12</sub>                                               | 0<br>A <sub>11</sub>                                                        | 1<br>A <sub>10</sub>                                                 | 0<br>A9                                                  | 1<br>A <sub>8</sub>                                        | Set<br>Column Address   | A [15:0] : Start Address (reset = 0)<br>B [15:0] : End Address (reset = 0)                                                      |

| 1<br>1<br>1           | A∟<br>B <sub>H</sub><br>B∟                                                   | A <sub>7</sub><br>B <sub>15</sub><br>B <sub>7</sub>                         | A <sub>6</sub><br>B <sub>14</sub><br>B <sub>6</sub>                | A5<br>B13<br>B5                                                             | A <sub>4</sub><br>B <sub>12</sub><br>B <sub>4</sub>                | A <sub>3</sub><br>B <sub>11</sub><br>B <sub>3</sub>                         | A <sub>2</sub><br>B <sub>10</sub><br>B <sub>2</sub>                  | A <sub>1</sub><br>B <sub>9</sub><br>B <sub>1</sub>       | A <sub>0</sub><br>B <sub>8</sub><br>B <sub>0</sub>         |                         | Range A from 0 to Display X-Size -1                                                                                             |

| 0<br>1<br>1<br>1<br>1 | 0x75<br>А <sub>н</sub><br>А <sub>L</sub><br>В <sub>н</sub><br>В <sub>L</sub> | 0<br>A <sub>15</sub><br>A <sub>7</sub><br>B <sub>15</sub><br>B <sub>7</sub> | $\begin{array}{c} 1 \\ A_{14} \\ A_6 \\ B_{14} \\ B_6 \end{array}$ | 1<br>A <sub>13</sub><br>A <sub>5</sub><br>B <sub>13</sub><br>B <sub>5</sub> | $\begin{array}{c} 1 \\ A_{12} \\ A_4 \\ B_{12} \\ B_4 \end{array}$ | 0<br>A <sub>11</sub><br>A <sub>3</sub><br>B <sub>11</sub><br>B <sub>3</sub> | $ \begin{array}{c} 1 \\ A_{10} \\ A_2 \\ B_{10} \\ B_2 \end{array} $ | $\begin{array}{c} 0\\ A_9\\ A_1\\ B_9\\ B_1 \end{array}$ | $ \begin{array}{c} 1\\ A_8\\ A_0\\ B_8\\ B_0 \end{array} $ | Set<br>Row Address      | A [15:0] : Start Address (reset = 0)<br>B [15:0] : End Address (reset = 0)<br>Range A from 0 to Display Y-Size -1               |

| 0                     | 0x5C                                                                         | 0                                                                           | 1                                                                  | 0                                                                           | 1                                                                  | 1                                                                           | 1                                                                    | 0                                                        | 1                                                          | Write<br>RAM Command    | Enable MCU to write Data into VRAM                                                                                              |

| 0                     | 0x5D                                                                         | 0                                                                           | 1                                                                  | 0                                                                           | 1                                                                  | 1                                                                           | 1                                                                    | 0                                                        | 1                                                          | Read<br>RAM Command     | Enable MCU to read Data from VRAM                                                                                               |

| 0<br>1                | 0xA0<br>A [7:0]                                                              | 1<br>A <sub>7</sub>                                                         | 0<br>A <sub>6</sub>                                                | 1<br>A5                                                                     | 0<br>A4                                                            | 0<br>A <sub>3</sub>                                                         | 0<br>A <sub>2</sub>                                                  | 0<br>A1                                                  | 0<br>A <sub>0</sub>                                        | Set<br>Display Setup    | A[0] = 0b, Horizontal address increment (reset)<br>A[0] = 1b, Vertical address increment                                        |

|                       |                                                                              |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            |                         | A[1] = 0b, Column Scan Left to Right [ $L \rightarrow R$ ] (reset)<br>A[1] = 1b, Column Scan Right to Left [ $L \leftarrow R$ ] |

|                       |                                                                              |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            |                         | A[2] = 0b, Row Scan Up to Down [ $U \rightarrow D$ ] (reset)<br>A[2] = 1b, Row Scan Down to UP [ $U \leftarrow D$ ]             |

|                       |                                                                              |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            |                         | A[3] = 0b, reserved<br>A[3] = 1b, reserved                                                                                      |

|                       |                                                                              |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            |                         | A[4] = 0b, reserved<br>A[4] = 1b, reserved                                                                                      |

|                       |                                                                              |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            |                         | A[5] = 0b, Read/Write Display Data from/to Page 1<br>A[5] = 1b, Read/Write Display Data from/to Page 2                          |

|                       |                                                                              |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            |                         | A[6] = 0b, Display Data Page 1<br>A[6] = 1b, Display Data Page 2                                                                |

|                       |                                                                              |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            |                         | A[7] = 0b, reserved<br>A[7] = 1b, reserved                                                                                      |

| 0                     | 0xAB                                                                         |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            | Set<br>Display Function |                                                                                                                                 |

| 0                     | 0x18                                                                         |                                                                             |                                                                    |                                                                             |                                                                    |                                                                             |                                                                      |                                                          |                                                            | Set<br>Read Address     |                                                                                                                                 |

# 2.2.1 Set Column Address (0x15)

This five byte command specifies column start address and end address of the display data RAM. This command also sets the column address pointer to column start address. This pointer is used to define the current read/write column address in graphic display data RAM. If horizontal address increment mode is enabled by command A0h, after finishing read/write one column data, it is incremented automatically to the next column address. Whenever the column address pointer finishes accessing the end column address, it is reset back to start column address and the row address is incremented to the next row.

## 2.2.2 Set Row Address (0x75)

This five byte command specifies row start address and end address of the display data RAM. This command also sets the row address pointer to row start address. This pointer is used to define the current read/write row address in graphic display data RAM. If vertical address increment mode is enabled by command AOh, after finishing read/write one row data, it is incremented automatically to the next row address. Whenever the row address pointer finishes accessing the end row address, it is reset back to start row address.

For example, column start address is set to 2 and column end address is set to 125, row start address is set to 1 and row end address is set to 126. Horizontal address increment mode is enabled by command A0h. In this case, the graphic display data RAM column accessible range is from column 2 to column 125 and from row 1 to row 126 only. In addition, the column address pointer is set to 2 and row address pointer is set to 1.

After finishing read/write one pixel of data, the column address is increased automatically by 1 to access the next RAM location for next read/write operation (*solid line in Figure 2-1*).

Whenever the column address pointer finishes accessing the end column 125, it is reset back to column 2 and row address is automatically increased by 1 (*solid line in Figure 2-1*).

While the end row 126 and end column 125 RAM location is accessed, the row address is reset back to 1 and the column address is reset back to 2 (*dotted line in Figure 2-1*).

|         | Col 0 | Col 1 | Col 2    |   | <br>Col125    | Col126 | Col127 |

|---------|-------|-------|----------|---|---------------|--------|--------|

| Row 0   |       |       |          |   |               |        |        |

| Row 1   |       |       | <b>^</b> |   |               |        |        |

| Row 2   |       |       |          |   |               |        |        |

| :       |       |       | -        | : |               |        |        |

| :       |       |       |          | : |               |        |        |

| :       |       |       |          | : |               |        |        |

| Row 125 |       |       | -        |   |               |        |        |

| Row 126 |       |       |          |   | $\rightarrow$ |        |        |

| Row 127 |       |       | 1        |   | 1             |        |        |

|         | 1     | 1     |          |   | <br>1         | 1      | 1      |

#### Figure 2-1 : Example of Column and Row Address Pointer Movement

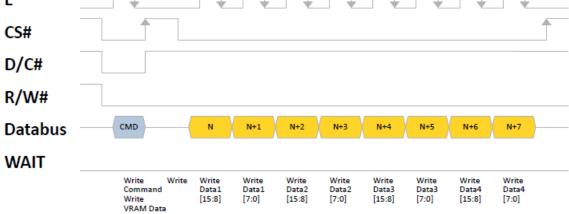

## 2.2.3 Write RAM Command (0x5C)

After entering this single byte command, data entries will be written into the display RAM until the CS# line is entered High pegel again or another command is written. Address pointer is increased accordingly. This command must be sent before write data into RAM.

## 2.2.4 Read RAM Command (0x5C)

After entering this single byte command, poll the wait line to ensure that the data to reading becomes valid. If the Wait line is Low you can read data from display RAM until the Wait line, CS# line is entered High pegel again or another command is written. Address pointer is increased accordingly. This command must be sent before read data from RAM.

## 2.2.5 Set Display Setup

• Address increment mode (A[0])

When A[0] is set to 0, the driver is set as horizontal address increment mode. After the display RAM is read / written, the column address pointer is increased automatically by 1. If the column address pointer reaches column end address, the column address pointer is reset to column start address and row address pointer is increased by 1. The sequence of movement of the row and column address point for horizontal address increment mode is shown in *Figure 2-2*.

|         | Col 0      | Col 1 |   | Col 126 | Col 127 |

|---------|------------|-------|---|---------|---------|

| Row 0   |            |       |   |         |         |

| Row 1   | +          |       |   |         |         |

| :       | <b>+</b> : | 1     | 1 | 1.0     |         |

| Row 126 | +          |       |   |         |         |

| Row 127 | +          |       |   |         |         |

Figure 2-2 : Address Pointer Movement of Horizontal Address Increment Mode

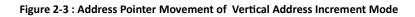

When A[0] is set to 1, the driver is set to vertical address increment mode. After the display RAM is read / written, the row address pointer is increased automatically by 1. If the row address pointer reaches the row end address, the row address pointer is reset to row start address and column address pointer is increased by 1. The sequence of movement of the row and column address point for vertical address increment mode is shown in *Figure 2-3*.

|         | Co | 0 10 | Co | 11 |   | Col | 126 | Col | 127 |

|---------|----|------|----|----|---|-----|-----|-----|-----|

| Row 0   |    |      |    |    |   |     | 1   |     |     |

| Row 1   |    |      |    |    | / |     |     |     |     |

| :       |    |      |    |    | : |     |     |     |     |

| Row 126 |    |      |    |    | / |     |     |     |     |

| Row 127 |    |      |    | ¥  |   |     | ¥ _ |     |     |

• Column Scan (A[1])

This command bit is made for increasing the layout flexibility of segment scan signals in Display module with segment arranged from left to right (when A[1] is set to 0) or vice versa (when A[1] is set to 1), as demonstrated in *Figure 2-4*.

$\begin{array}{l} A[1]=0: RAM \ Column \ 0 \rightarrow Colomn \ X_{max} \ maps \ to \ Display \ Column \ 0 \rightarrow Column \ X_{max} \\ A[1]=1: RAM \ Column \ 0 \rightarrow Colomn \ X_{max} \ maps \ to \ Display \ Column \ X_{max} \rightarrow Column \ 0 \end{array}$

| A[1] = 0               | Col 0 | 2-4 : Column Sca<br>Col 1 |       | Col X <sub>max-1</sub> | Col X <sub>max</sub> |

|------------------------|-------|---------------------------|-------|------------------------|----------------------|

| Row 0                  |       |                           | ••••• |                        | ->                   |

| Row 1                  |       |                           |       |                        |                      |

| :                      |       |                           | •     |                        |                      |

| Row Y <sub>max-1</sub> |       |                           | ••••• |                        | →                    |

| Row Y <sub>max</sub>   |       |                           |       |                        | $\rightarrow$        |

| A[1] = 1               | Col 0 | Col 1 | ••••• | Col X <sub>max-1</sub> | Col X <sub>max</sub> |

|------------------------|-------|-------|-------|------------------------|----------------------|

| Row 0                  |       |       | ••••• |                        | 5                    |

| Row 1                  | -     |       |       |                        |                      |

| :                      |       |       | •     |                        |                      |

| Row Y <sub>max-1</sub> |       |       |       |                        |                      |

| Row Y <sub>max</sub>   |       |       | ••••• |                        |                      |

|                        | ,     | 1     | 1     | 1                      |                      |

## • Row Scan (A[2])

This command bit is made for increasing the layout flexibility of segment scan signals in Display module with rows arranged from up to down (when A[2] is set to 0) or vice versa (when A[2] is set to 1), as demonstrated in *Figure 2-5*.

A[2] = 0: RAM Row 0  $\rightarrow$  Row Y<sub>max</sub> maps to Display Row 0  $\rightarrow$  Row Y<sub>max</sub>

A[2] = 1: RAM Row  $0 \rightarrow \text{Row } Y_{\text{max}}$  maps to Display Row  $Y_{\text{max}} \rightarrow \text{Row } 0$

|                      | Figur | e 2-5 : Row Scar | n - Ram to Dis | play                   |                      |

|----------------------|-------|------------------|----------------|------------------------|----------------------|

| A[2] = 0             | Col 0 | Col 1            | •••••          | Col X <sub>max-1</sub> | Col X <sub>max</sub> |

| Row 0                |       |                  | •••••          |                        |                      |

| Row 1                |       |                  |                |                        | Ţ                    |

| :                    |       |                  | ÷              |                        | 1                    |

| Row Ymax-1           |       |                  | •••••          |                        |                      |

| Row Y <sub>max</sub> |       |                  | •••••          |                        |                      |

| • |  |

|---|--|

|   |  |

|   |  |

|   |  |

Figure 2-4 : Column Scan - Ram to Display