# Programmable Logic Devices

# **ATF15xx Family Device Fitter**

Device Fitting Software

User Manual

| SECTION 1    |                                                         | 5  |

|--------------|---------------------------------------------------------|----|

| INTRODUCTIO  | N                                                       | 5  |

| SECTION 2    |                                                         | 6  |

| ATF15XX FAM  | IILY ARCHITECTURAL FEATURES                             | 6  |

| 2.1 MA       | CROCELL [MC] FEATURES                                   | 8  |

| 2.2 FOL      | DBACK LOGIC                                             | 9  |

| 2.3 CAS      | CADE LOGIC                                              | 9  |

| 2.4 POV      | VER DOWN CONTROL                                        | 9  |

| 2.5 SLE      | W RATE CONTROL                                          | 10 |

| 2.6 LOC      | IC DOUBLING                                             | 10 |

| SECTION 3    |                                                         | 11 |

| USING THE A  | IF15XX FITTER                                           | 11 |

| 3.1 INS      | TALLATION                                               | 11 |

|              | 3.1.1 PROCHIP DESIGNER                                  | 11 |

|              | 3.1.2 ATMEL-WINCUPL                                     | 11 |

|              | 3.1.3 PROTEL TOOLS                                      | 11 |

|              | 3.1.4 ATMEL SYNARIO                                     | 11 |

|              | 3.1.5 LEGACY VERSIONS OF ABEL (4.2X-5.X), CUPL (4.5X)   | 11 |

| 3.2 DEV      | ICE SUPPORT                                             | 12 |

|              | 3.2.1 LEGACY ABEL (DOS VERSIONS)                        | 12 |

|              | 3.2.2 ATMEL ATF15XX DEVICE NAMES (MNEMONICS)            | 12 |

| 3.3 PIN/     | NODE MAPS FOR THE ATF15XX FAMILY                        | 14 |

| 3.4 OPE      | RATION                                                  | 21 |

|              | 3.4.1 VHDL DESIGNS (PROCHIP ENVIRONMENT)                | 21 |

|              | 3.4.2 VHDL DESIGNS (ATMEL-SYNARIO ENVIRONMENT)          | 22 |

|              | 3.4.3 ABEL DESIGNS (ATMEL-SYNARIO AND LEGACY ABEL 5.1X) | 22 |

|              | 3.4.4 CUPL/SCHEMATIC DESIGNS (PROCHIP ENVIRONMENT)      | 22 |

|              | 3.4.5 CUPL (ATMEL- WINCUPL)                             | 23 |

|              | 3.4.6 CUPL AND MCUPL (LEGACY VERSIONS OF CUPL)          | 24 |

|              | 3.4.7 COMMAND LINE                                      | 25 |

| SECTION 4    |                                                         | 26 |

| FIT15XX STRA | TEGIES                                                  | 26 |

| 4.1 BAS      | IC STRATEGIES                                           | 26 |

|              | 4.1.1 SPECIFYING INPUT FILENAME [-I]                    | 26 |

|              | 4.1.2 SPECIFYING OUTPUT FILENAMES [-O]                  | 26 |

| 4.1.3 FITTER REPORT FILENAME [-LOG]               | 26 |

|---------------------------------------------------|----|

| 4.1.4 ERROR FILE [-ERR]                           | 27 |

| 4.1.5 SPECIFY DEVICE [-DEVICE]                    | 27 |

| 4.1.6 PREASSIGN PINS [-PRE TRY KEEP IGNORE]       | 27 |

| 4.1.7 SILENT OPTION [-SILENT]                     | 28 |

| 4.1.8 HELP OPTION [-HELP]                         | 28 |

| 4.2 ADVANCED OPTIONS AND STRATEGIES [-H2]         | 28 |

| 4.2.1 OPTIMIZE                                    | 28 |

| 4.2.2 XOR SYNTHESIS                               | 28 |

| 4.2.3 CASCADE LOGIC                               | 29 |

| 4.2.4 FOLDBACK LOGIC                              | 29 |

| 4.2.5 FOLDBACK LOGIC COMPATIBILITY                | 29 |

| 4.2.6 NODE COLLAPSING                             | 30 |

| 4.2.7 DEDICATED INPUTS                            | 30 |

| 4.2.8 SLEW RATE CONTROL                           | 30 |

| 4.2.9 POWER DOWN CONTROL                          | 31 |

| 4.2.10 JEDEC FILE [-STR JEDEC_FILE = FILE_NAME]   | 31 |

| 4.2.11 VECTOR FILE [-STR VECTOR_FILE = FILE_NAME] | 31 |

| 4.3 PROPERTY STATEMENT                            | 32 |

| 4.3.1 ABEL                                        | 32 |

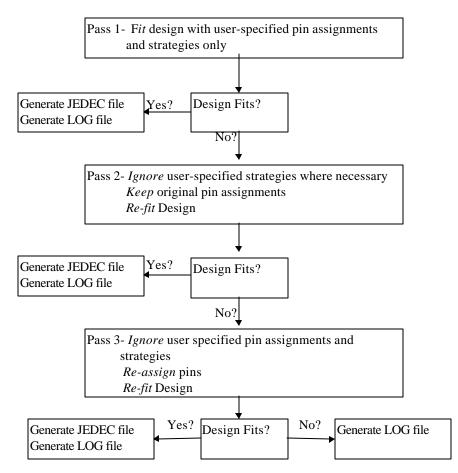

| 4.3.2 CUPL                                        | 34 |

| 4.4 FITTER MACRO LIBRARY FOR ATF1500A             | 35 |

| 4.4.1 ATF1500A MACRO LIBRARY FOR ABEL             | 35 |

| 4.4.2 USING THE CUPL MACRO LIBRARY                | 35 |

| SECTION 5                                         | 37 |

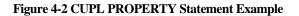

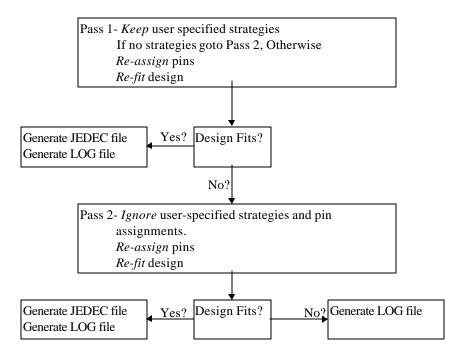

| 5.1 DESIGN PASSES                                 | 37 |

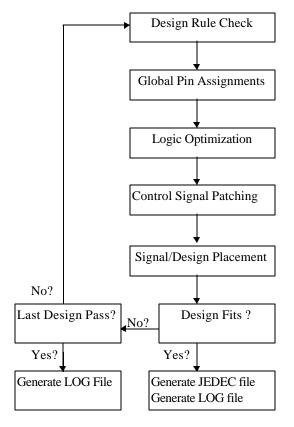

| 5.1.1 KEEP OPTION                                 | 38 |

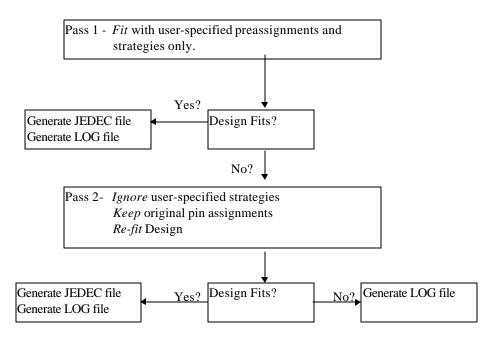

| 5.1.2 TRY OPTION                                  | 39 |

| 5.1.3 IGNORE OPTION                               | 40 |

| 5.2 DESIGN RULE CHECK                             | 40 |

| 5.3 ASSIGN GLOBAL INPUT PINS                      | 40 |

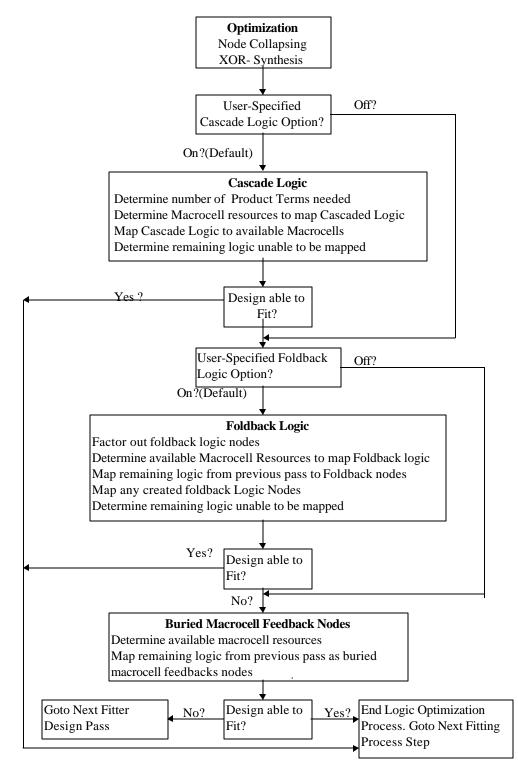

| 5.4 LOGIC OPTIMIZATION                            | 41 |

| 5.5 CONTROL SIGNAL PATCHING                       | 42 |

| 5.6 SIGNAL/DESIGN PLACEMENT                       | 42 |

| 5.7 FUSEMAPPING                                   | 42 |

| SECTION 6                                         | 43 |

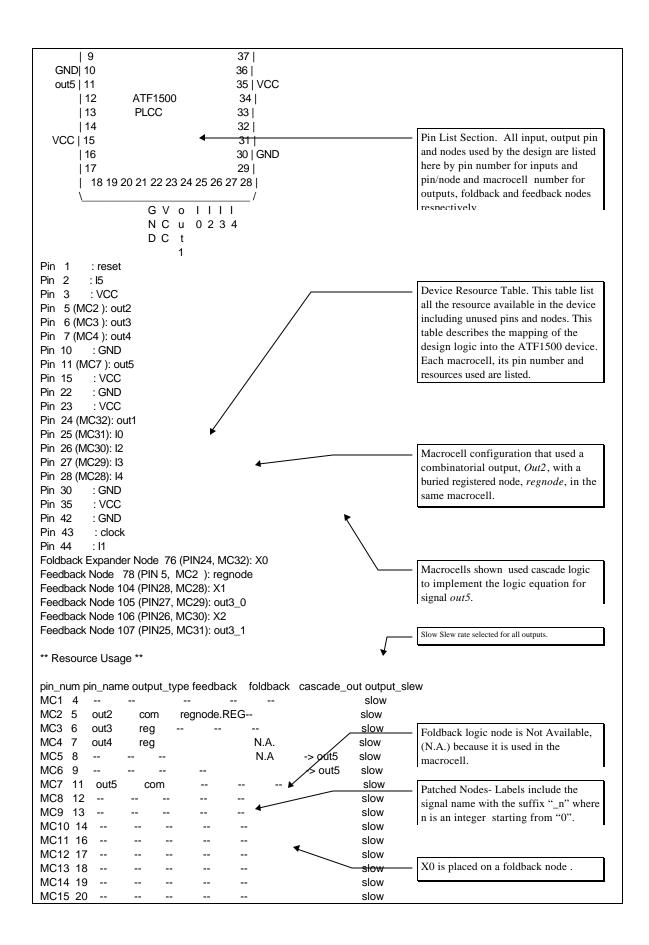

| INTERPRETING THE FITTER LOG FILE                        | 43 |

|---------------------------------------------------------|----|

| SECTION 7                                               | 47 |

| FITTER HINTS                                            | 47 |

| 7.1 HINT 1 - DO NOT ASSIGN PINS                         | 48 |

| 7.2 HINT 2 - USE DEFAULT PROPERTIES AND STRATEGIES      | 48 |

| 7.3 HINT 3 - USING CASCADE LOGIC FOR DESIGN PERFORMANCE | 48 |

| 7.4 HINT 4 - USING FOLDBACK LOGIC                       | 49 |

| 7.5 HINT 5- USE XOR SYNTHESIS                           | 51 |

| 7.6 HINT 6- PREVENT CERTAIN NODES FROM COLLAPSING       | 54 |

| 7.7 HINT 7- USING SLEW RATE CONTROL                     | 58 |

| 7.8 HINT 8 -USING THE POWER DOWN PIN                    | 59 |

| SECTION 8                                               | 58 |

| APPENDIX A - ERROR LISTING                              | 58 |

| SECTION 9                                               | 60 |

| APPENDIX B - ATF1500A MACRO LIBRARY LISTING             | 60 |

# Introduction

This manual describes how to use the Atmel<sup>TM</sup> ATF15xx device fitter for Atmel-WinCUPL, Prochip Designer, Protel design tools and legacy tools such as ABEL<sup>TM</sup>, Atmel-Synario. The ATF15xx family of Complex Programmable Logic Devices [CPLDs] includes the ATF1500A, ATF1502xx, ATF1504xx, ATF1508xx and ATF1516xx devices. The fitter is required to fit designs into an Atmel CPLD and generate a JEDEC file. The macrocell (MC) and device features of this family will be introduced along with fitter installation requirements. The various fitter options and the fitting process are described in detail. Design examples are included to highlight the features of the ATF15xx family of devices and the various fitter command options.

In this manual, device fitter strategies for the ATF1500A differ slightly from the strategies available for the ATF15xx device fitters.

# **ATF15xx Family Architectural Features**

The ATF15xx family includes the ATF1500A and ATF15xx devices (ATF1502xx, ATF1504xx, ATF1508xx and the ATF1516xx). In-system programming (ISP) capability and low voltage/low power offering of these devices is shown in Table 1.

The ATF1500A and the ATF1502xx are offered in 44-lead PLCC/TQFP packages. The ATF1504xx is offered in 44-lead PLCC/TQFP, 68-lead PLCC, 84-lead PLCC and 100-lead TQFP/PQFP packages. The ATF1508xx is offered in 84-lead PLCC, 100-lead TQFP/PQFP and 160-lead PQFP packages. Additional package options such as BGA will be offered for the ATF15xxSE and the ATF15xxAE family of devices.

| Atmel Device            | Number of       | ISP        | Description                 |

|-------------------------|-----------------|------------|-----------------------------|

|                         | Macrocells (MC) | capability |                             |

| ATF1500A                | 32              | No         | 5 V Standard Power Device   |

| ATF1500AL               | 32              | No         | 5 V Low Power Device        |

| ATF1500ABV              | 32              | No         | 2.7 V Standard Power Device |

| ATF1502AS, ATF1502SE    | 32              |            |                             |

| ATF1504AS, ATF1504SE    | 64              | Yes        | 5 V Standard Power Device   |

| ATF1508AS, ATF1508SE    | 128             |            |                             |

| ATF1516SE               | 256             |            |                             |

| ATF1502ASL, ATF1502SEL  | 32              |            |                             |

| ATF1504ASL, ATF1504SEL  | 64              | Yes        | 5 V Low Power Device        |

| ATF1508ASL, ATF1508SEL  | 128             |            |                             |

| ATF1516SEL              | 256             |            |                             |

| ATF1502ASV, ATF1502AE   | 32              |            |                             |

| ATF1504ASV, ATF1504AE   | 64              | Yes        | 3.3 V Standard Power Device |

| ATF1508ASV, ATF1508AE   | 128             |            |                             |

| ATF1516AE               | 256             |            |                             |

| ATF1502ASVL, ATF1502AEL | 32              |            |                             |

| ATF1504ASVL, ATF1504AEL | 64              | Yes        | 3.3 V Low Power device      |

| ATF1508ASVL, ATF1508AEL | 128             |            |                             |

| ATF1516AEL              | 256             |            |                             |

## Table 2-1. Atmel's ATF15xx Family of CPLDs

The macrocell architecture of the ATF1502xx, ATF1504xx, ATF1508xx and ATF1516xx is identical and differs slightly from that of the ATF1500A.

The ATF1500A (non-ISP device) is a globally connected part in that every pin can be routed to any other pin whereas the ATF1502AS (ISP capable) has a specific number of pins, feedback signals that can be routed to a Logic Array Blocks (LAB) via a Universal Interconnect Matrix [UIM]. Each LAB consists of 16 MCs.

Some highlights of the the ATF1500A device are:

- 32 I/O pins each connected to a macrocell [MC]

- 1 Global Clock or dedicated input pin

- 1 Global Reset or dedicated input pin

- 2 Global Output Enable or dedicated input pins

- All I/O pin and registered feedbacks connected to a Global Input Bus

- All Foldback Logic connected to a Regional Foldback Bus

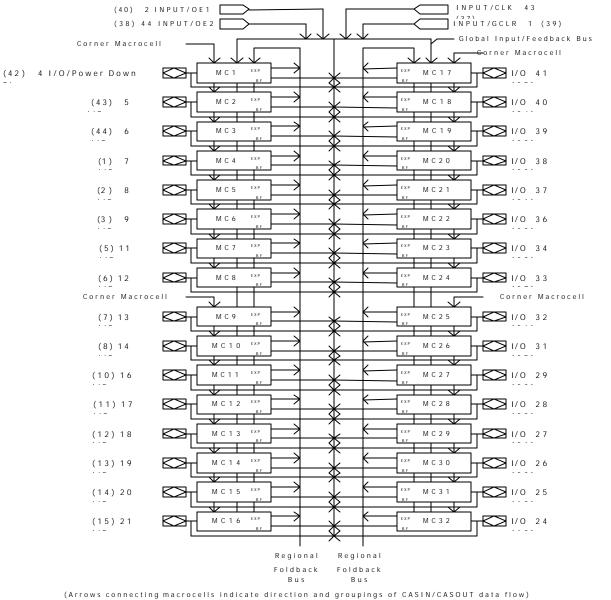

All inputs connected to the Global Input Bus are available to *every* MC in the device. All inputs connected to the Foldback Bus are available to a group of 16 MCs. Figure 2-1 shows the block diagram of the device.

(Allows connecting matrocers mutate unection and groupings of CASIN/CASOOF data now)

Corner Macrocells that cannot borrow product terms from adjacent macrocell are: (4,13,32,41) for PLCC. (7,26,35,42) for TQFP

Figure 2-1. ATF1500A Block Diagram

# 2.1 Macrocell [MC] Features

Specific features of each MC include:

| ATF1500A Macrocell                                 | ATF15xx Macrocell                                  |

|----------------------------------------------------|----------------------------------------------------|

| Global or Product Term controlled Output Enable    | Global [GOE0-GOE5]or Product Term controlled       |

| originate from the Input Pins                      | Output Enable originate from the Switch Matrix     |

| Global or Product Term controlled Reset inputs     | Global or Product Term controlled Reset inputs     |

| Global or Product Term controlled Clock inputs     | 3 Global Clocks or Product term Clock input        |

| Product-Term controlled Clock Enable and Preset    | Product-Term controlled Clock Enable and Preset    |

| inputs                                             | inputs                                             |

| 5 product terms per MC                             | 5 product terms per MC                             |

| Foldback and Cascade Logic                         | Foldback and Cascade logic                         |

| Independently configurable D/T/L Flip-flop         | Independently configurable D/T/L Flip-flop.        |

| Combinatorial Output with a Buried Register option | Combinatorial Output with a Buried Register option |

|                                                    | or Buried Combinatorial ouput with Registered      |

|                                                    | Output.                                            |

| Pin controlled or Automatic Power Down Control     | Pin controlled or Automatic Power Down Control     |

| options                                            | options                                            |

| Slew Rate Control on each output                   | Slew Rate Control on each output                   |

| Programmable Pin Keeper Circuits                   | Programmable Pin Keeper Circuits                   |

| The ATF1500A is a non-ISP device                   | 4 JTAG port pins that allow for ISP                |

|                                                    | Open Collector Outputs                             |

|                                                    | Fast Input from the I/O pin                        |

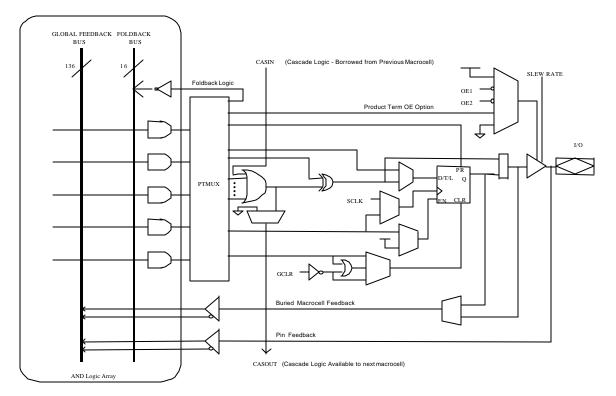

Figure 2-2 shows the ATF1500A MC in more detail.

Figure 2-2 ATF1500A Macrocell

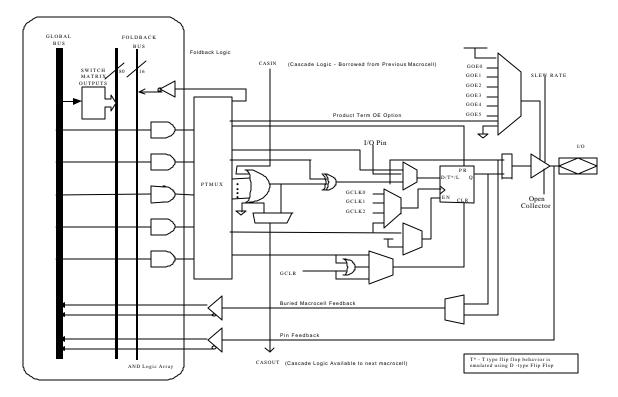

This MC is the same for ATF1502xx, ATF1504xx, ATF1508xx, ATF1516xx

# Figure 2-3 ATF15xx Macrocell

Figure 2-3 shows the MC architecture for the ATF15xx MC.

# 2.2 Foldback Logic

Each ATF15xx/ATF1500A MC contains foldback logic nodes which allow complex functions requiring additional logic to be implemented. All foldback logic nodes are connected to the Foldback bus. The ATF15xx/ATF1500A contains two foldback busses each allocated to a group of 16 MCs. Foldback logic nodes for the first group containing macrocells MC1 through MC16 are connected to one of the foldback busses. The Foldback logic nodes for the second group of macrocells, MC17 through MC32, are connected to the other foldback bus. See Figure(s) 1 and 2 for more details.

# 2.3 Cascade Logic

Cascade logic allow logic to be borrowed from an adjacent MC. It is available for all macrocells, except the corner macrocells MC1, MC9, MC17 and MC25. This feature is useful for designs which require large product term fan-in such as state machines or high performance designs where speed is important. Each macrocell can borrow up to 5 product terms from an adjacent macrocell. Several macrocells can be cascaded together to provide up to 40 products terms for a single macrocell.

# 2.4 Power Down Control

All devices that belong to the ATF15xx Family have a Pin(s) {PD1, PD2}, which when asserted will power down the array and consume very low power. For example, the ATF1502AS is available in both standard and Low Power versions (ATF1502AS, ATF1502ASL respectively). The ATF1502AS has a Pin-Controlled power down pin option which, when enabled, allows the user to power down the device to a zero power mode where it draws a standby current in the microampere range. The ATF1502ASL low power device has

an Automatic power down feature. This feature powers down the device when no transitions occur on *any*.input, internal feedbacks or I/O pins. The ATF1502xx fitter has a command option to enable the Pin-Controlled power down feature. Please refer to Section 4.2.9 for more information.

# 2.5 Slew Rate Control

Each macrocell output on the ATF15xx has a programmable slew rate control bit. This bit can be used to to reduce system noise by slowing down the output that do not need to operate a maximum speed. All outputs default to the slower switching rate unless specified as fast switching in the ATF15xx fitter Slew Rate Control option. Please refer to Section 4.2.8 for more information on the specific strategy {**output\_fast**}.

# 2.6 Logic Doubling

The term 'Logic\_doubling' refers to the efficient, flexible CPLD architecture now available with second generation fitters and applies to all ATF15xx members except the ATF1500A which is a 100% connected CPLD. The ATF15xx Family has a number of features that address connectivity and reusability problems.

- More crosspoint Multiplexer (MUXs) available for input node fan-in

- Wider MUX channels into the Logic Array Blocks (LABs)

- Dual, independent feedback paths for each macrocell. The buried and pin-driver paths are split, so a register output may be buried while independently driving a combinatorial pin, or vice versa.

- Every MC may have separate Output Enable (product term controlled).

- Selectable Global Clock polarity, either falling or rising edge

- Global RESET can combine (OR) with a local product term

# Using the ATF15xx Fitter

This section describes how to install and use the Atmel ATF15xx device fitter with PROCHIP, ABEL(ATMEL-SYNARIO) and CUPL PLD development software.

# **3.1 INSTALLATION**

The ATF15xx family of fitters are available for download from the Atmel website. {File Fit15xx.zip has the latest versions of Fitters that were released.} If you have any questions about obtaining these files please send an email to <u>pld@atmel.com</u> or call the Atmel PLD Applications Hotline at (408)436-4333.

# 3.1.1 PROCHIP DESIGNER

If you have already installed the Prochip Design tool, you can simply update the <Prochip>\PLDFIT Folder with a later version. Simply unzip the Fit15xx.zip file into this folder. Automatic updates to Prochip are also planned via the web.

# 3.1.2 ATMEL-WINCUPL

For customers who have previously installed Atmel-WinCupl Ver. 5.x, the FIT15xx.zip file can always be unzipped into the <Wincupl>\Wincupl\Fitters Folder. The current version of Atmel-Wincupl available for download off the website as a single file always contains the latest versions of the Device Fitters.

# 3.1.3 ALTIUM (PROTEL) TOOLS

The Design Explorer 99SE tool from ALTIUM (formerly called PROTEL) which is bundled in with the Prochip Design tool does not require a separate update, so long as the Fitters are being referenced from the Prochip tool.

If Design Explorer 99SE is installed as a separate tool (or if you have the full version of the tool from PROTEL), then the default location for the Fitters is in the <Programs>\Design Explorer 99 SE\library\pld folder.

## 3.1.4 ATMEL SYNARIO

If you have ATMEL SYNARIO V4.11 (has ABEL 6.x), the ATF15xx fitter software is included in the Atmel Device Kit for the appropriate tool. A Patch file {SNPCH411.exe} is available off the Atmel website. This is a single file install and will automatically copy the Fitters to the appropriate folders.

# 3.1.5 LEGACY VERSIONS OF ABEL (4.2x-5.x), CUPL (4.5x)

If you have Atmel-CUPL (V4.5b) you will need to install the fit1500.exe from the fit15xx.zip file. You can thus design with the ATF1500A device only. Similarly, Data I/O ABEL (V4.10 - 5.10) or Atmel-ABEL (4.2x-5.10) users will need to install the ATF1500 fitter. The older versions of ABEL (or stand alone Data I/O versions from the early nineties) do not have device support for the ATF15xx family, in particular the ATF1502xx or the ATF1504xx.

\_\_\_\_

# 3.2 Device Support

All device packages as listed in the appropriate data sheet for an ATF15xx are supported. The Atmel ATF1500 fitter supports both the ATF1500A PLCC-44 and TQFP-44 packages. Specific device names (mnemonics) for ABEL(ATMEL-SYNARIO) and CUPL(applicable to WinCUPL/PROTEL) are listed in Section 3.2.2.

# 3.2.1 Legacy ABEL (DOS Versions)

The ATF1500A is supported in legacy versions of ABEL (V4.10 -5.1) by the device mnemonics listed below. The ATF1500 which was the first device introduced is no longer in production and the replacement part is the ATF1500A.

Device mnemonics are useful if the fitting process is run from the DOS prompt (ATMEL-SYNARIO).

# 3.2.2 ATMEL ATF15xx Device Names (mnemonics)

Table 3-1 lists the device mnemonics that must be specified when running the fitter manually from the DOS command line. The ATMEL WinCUPL device mnemonics listed are applicable to the header section of a CUPL source file only. However it is not important to remember the device menmonic when running ATMEL WinCUPL 5.2x. {Device names can be viewed by Package type from the Options...Devices Tab}

Atmel Synario also does not require the USER to specify a device mnemonic. Simply select the appropriate Atmel device from the list of ATMEL PLDs from the Project Sources window and proceed to generate the Fitter Report and JEDEC file used to program the device.

Select the In-system programming (ISP) device type from Table 3-1, when the JTAG port (4 pins) are to be exclusively used only for ISP operation.

The appropriate device mnemonic can also be specified when running the fitter from the DOS prompt.

Examples of running the Fitter in different Environments.

- ➡ FIT1502 filename.tt2 -dev p1502c44 -str JTAG=ON Filename.tt2 is an intermediate PLA file created by the ABEL Compiler.

- ➡ FIT1502 filename.tt2 -cupl -dev p1502c44 -str JTAG=on -str preassign=keep Filename.tt2 is an intermediate PLA file created by the ATMEL WinCUPL tool. Note that there is a slight difference between the ABEL PLA and CUPL PLA files.

- ➡ FIT1502 -i filename.edf -ifmt EDIF -lib aprim.lib -dev p1502c44 -str JTAG=off If the input file is an EDIF file (EDIF version 2.0) created by a VHDL compiler (PEAKFPGA/PROCHIP)

- ⇒ FIT1502 -c filename.cmd

The command file contains the list of all strategies and can be used if the command string is too long.

| ATMEL DEVICE            | ABEL Device Mnemonic         | ATMEL WinCUPL                    |

|-------------------------|------------------------------|----------------------------------|

|                         | (Device type when manually   | Device Mnemonic                  |

|                         | running fitter from the DOS  | (Applicable to Header section or |

|                         | prompt)                      | for the Protel Tool)             |

| ATF1500/L - PLCC44      | p1500                        | f1500                            |

| ATF1500/L -TQFP44       | p1500t                       | f1500t                           |

| ATF1500A/AL/ABV - PLCC  | p1500a                       | f1500a                           |

| ATF1500A/AL/ABV -TQFP   | p1500at                      | f1500at                          |

| ATF1502xx - PLCC44      | p1502c44                     | f1502plcc44                      |

| ATF1502xx - ISP PLCC44  | p1502c44 (Use -str JTAG=on)  | f1502ispplcc44                   |

| ATF1502xx -TQFP44       | p1502t44                     | f1502tqfp44                      |

| ATF1502xx -ISP TQFP44   | p1502t44 (Use -str JTAG=on)  | f1502isptqfp44                   |

| ATF1504xx - PLCC44      | p1504c44                     | f1504plcc44                      |

| ATF1504xx - ISP PLCC44  | p1504c44 (Use -str JTAG=on)  | f1504ispplcc44                   |

| ATF1504xx -TQFP44       | p1504t44                     | f1504tqfp44                      |

| ATF1504xx -ISP TQFP44   | p1504t44 (Use -str JTAG=on)  | f1504isptqfp44                   |

| ATF1504xx - PLCC68      | p1504c68                     | f1504plcc68                      |

| ATF1504xx - ISP PLCC68  | p1504c68 (Use -str JTAG=on)  | f1504ispplcc68                   |

| ATF1504xx - PLCC84      | p1504c84                     | f1504plcc84                      |

| ATF1504xx - ISP PLCC84  | p1504c84 (Use -str JTAG=on)  | f1504plcc84                      |

| ATF1504xx - TQFP100     | p1504t100                    | f1504tqfp100                     |

| ATF1504xx - ISP TQFP100 | p1504t100 (Use -str JTAG=on) | f1504isptqfp100                  |

| ATF1504xx - PQFP100     | p1504q100                    | f1504pqfp100                     |

| ATF1504xx - ISP PQFP100 | p1504q100 (Use -str JTAG=on) | f1504isppqfp100                  |

| ATF1508xx - PLCC84      | p1508c84                     | f1508plcc84                      |

| ATF1508xx -ISP PLCC84   | p1508c84 (Use -str JTAG=on)  | f1508ispplcc84                   |

| ATF1508xx -PQFP100      | p1508q100                    | f1508qfp100                      |

| ATF1508xx - ISP PQFP100 | p1508q100 (Use -str JTAG=on) | f1508ispqfp100                   |

| ATF1508xx -TQFP100      | p1508t100                    | f1508tqfp100                     |

| ATF1508xx - ISP TQFP100 | p1508t100 (Use -str JTAG=on) | f1508isptqfp100                  |

| ATF1508xx -PQFP160      | p1508q160                    | f1508pqfp160                     |

| ATF1508xx-ISP PQFP160   | p1508q160 (Use -str JTAG=on) | f1508isppqfp160                  |

Table 3-1. ATF15xx Device Mnemonics

# 3.3 Pin/Node Maps for the ATF15XX Family.

The pin and node assignments for **ATF1500A** in PLCC and TQFP package are shown in Table 3-2. This table also shows the node assignment for the Foldback logic and Buried registers (feedback node) available in each macrocell [MC]. These node numbers are the same for ABEL, CUPL and VHDL.

| MC | Foldback Node<br>Number | Feedback Node<br>Number | Pinout<br>44-Pin PLCC | Pinout<br>44-Pin TQFP |

|----|-------------------------|-------------------------|-----------------------|-----------------------|

| 1  | 45                      | 77                      | 4                     | 42                    |

| 2  | 46                      | 78                      | 5                     | 43                    |

| 3  | 47                      | 79                      | 6                     | 44                    |

| 4  | 48                      | 80                      | 7                     | 1                     |

| 5  | 49                      | 81                      | 8                     | 2                     |

| 6  | 50                      | 82                      | 9                     | 3                     |

| 7  | 51                      | 83                      | 11                    | 5                     |

| 8  | 52                      | 84                      | 12                    | 6                     |

| 9  | 53                      | 85                      | 13                    | 7                     |

| 10 | 54                      | 86                      | 14                    | 8                     |

| 11 | 55                      | 87                      | 16                    | 10                    |

| 12 | 56                      | 88                      | 17                    | 11                    |

| 13 | 57                      | 89                      | 18                    | 12                    |

| 14 | 58                      | 90                      | 19                    | 13                    |

| 15 | 59                      | 91                      | 20                    | 14                    |

| 16 | 60                      | 92                      | 21                    | 15                    |

| 17 | 61                      | 93                      | 41                    | 35                    |

| 18 | 62                      | 94                      | 40                    | 34                    |

| 19 | 63                      | 95                      | 39                    | 33                    |

| 20 | 64                      | 96                      | 38                    | 32                    |

| 21 | 65                      | 97                      | 37                    | 31                    |

| 22 | 66                      | 98                      | 36                    | 30                    |

| 23 | 67                      | 99                      | 34                    | 28                    |

| 24 | 68                      | 100                     | 33                    | 27                    |

| 25 | 69                      | 101                     | 32                    | 26                    |

| 26 | 70                      | 102                     | 31                    | 25                    |

| 27 | 71                      | 103                     | 29                    | 23                    |

| 28 | 72                      | 104                     | 28                    | 22                    |

| 29 | 73                      | 105                     | 27                    | 21                    |

| 30 | 74                      | 106                     | 26                    | 20                    |

| 31 | 75                      | 107                     | 25                    | 19                    |

| 32 | 76                      | 108                     | 24                    | 18                    |

Table 3-2. ATF1500A Pin/Node List

Table 3-3 shows the Pin and Node assignments for the **ATF1502xx** device in PLCC and TQFP package. Feedback and Foldback nodes numbers are listed though it is preferred that the fitter be allowed to arrive at the best possible fit without preassigning any Pinnode numbers.

| МС    | LAB | Feedback<br>Node<br>Number | Foldback<br>Node<br>Number | Signal Name | Pinout<br>44-Pin PLCC | Pinout<br>44-Pin TQFP |

|-------|-----|----------------------------|----------------------------|-------------|-----------------------|-----------------------|

| INPUT |     | none                       | none                       | (OE2/GCLK2) | 2                     | 40                    |

| INPUT |     | none                       | none                       | (GCLK1)     | 43                    | 37                    |

| INPUT |     | none                       | none                       | (GCLR)      | 1                     | 39                    |

| INPUT |     | none                       | none                       | (OE1)       | 44                    | 38                    |

| 1     | Α   | 601                        | 301                        |             | 4                     | 42                    |

| 2     |     | 602                        | 302                        |             | 5                     | 43                    |

| 3     |     | 603                        | 303                        |             | 6                     | 44                    |

| 4     |     | 604                        | 304                        |             | 7 (TDI)               | 1(TDI)                |

| 5     |     | 605                        | 305                        |             | 8                     | 2                     |

| 6     |     | 606                        | 306                        |             | 9                     | 3                     |

| 7     |     | 607                        | 307                        |             | 11                    | 5                     |

| 8     |     | No Casout 608              | 308                        |             | 12                    | 6                     |

| 9     |     | 609                        | 309                        |             | 13(TMS)               | 7(TMS)                |

| 10    |     | 610                        | 310                        |             | 14                    | 8                     |

| 11    |     | 611                        | 311                        |             | 16                    | 10                    |

| 12    |     | 612                        | 312                        |             | 17                    | 11                    |

| 13    |     | 613                        | 313                        |             | 18                    | 12                    |

| 14    |     | 614                        | 314                        |             | 19                    | 13                    |

| 15    |     | 615                        | 315                        |             | 20                    | 14                    |

| 16    |     | No Casout 616              | 316                        |             | 21                    | 15                    |

| 17    | В   | 617                        | 317                        |             | 41                    | 35                    |

| 18    |     | 618                        | 318                        |             | 40                    | 34                    |

| 19    |     | 619                        | 319                        |             | 39                    | 33                    |

| 20    |     | 620                        | 320                        |             | 38(TDO)               | 32(TDO)               |

| 21    |     | 621                        | 321                        |             | 37                    | 31                    |

| 22    |     | 622                        | 322                        |             | 36                    | 30                    |

| 23    |     | 623                        | 323                        |             | 34                    | 28                    |

| 24    |     | No Casout 624              | 324                        |             | 33                    | 27                    |

| 25    |     | 625                        | 325                        |             | 32(TCK)               | 26(TCK)               |

| 26    |     | 626                        | 326                        |             | 31                    | 25                    |

| 27    |     | 627                        | 327                        |             | 29                    | 23                    |

| 28    |     | 628                        | 328                        |             | 28                    | 22                    |

| 29    |     | 629                        | 329                        |             | 27                    | 21                    |

| 30    |     | 630                        | 330                        |             | 26                    | 20                    |

| 31    |     | 631                        | 331                        |             | 25                    | 19                    |

| 32    |     | No Casout 632              | 332                        |             | 24                    | 18                    |

## Table 3-3. ATF1502xx Pin/Node List

Table 3-4 lists the Pin and Node numbers for the **ATF1504xx** device in various packages. It is preferred that Foldback node numbers as well as Buried Feedback node numbers are not preassigned in the Source files so that the Fitter can fit the Design in a manner that allows for optimum use of resources within the Device.

| MC    | LAB | Feedback       | Foldback       | Signal Name |        | Piı               | nout for      | ATF1504       | xx                |                   |

|-------|-----|----------------|----------------|-------------|--------|-------------------|---------------|---------------|-------------------|-------------------|

|       |     | Node<br>Number | Node<br>Number |             | 44-Pin | 44-Pin            | 68-Pin        | 84-Pin        | 100-Pin           | 100-Pin           |

| INPUT |     | nono           | nono           | (OE2/GCLK2) | 2      | <b>TQFP</b><br>40 | <b>PLCC</b> 2 | <b>PLCC</b> 2 | <b>PQFP</b><br>92 | <b>TQFP</b><br>90 |

| INPUT |     | none<br>none   | none           | (GCLK1)     | 43     | 37                | 67            | 83            | 92<br>89          | 90<br>87          |

| INPUT |     |                | none           | (GCLRT)     | 43     | 37                | 1             | 03<br>1       | 89<br>91          | 89                |

| INPUT |     | none           | none           | (OE1)       | 44     | 39                | 68            | 84            | 90                | 88                |

| 1     | А   | 601            | 301            |             | 12     | 6                 | 18            | 22            | 90<br>16          | 14                |

| 2     | ~   | 602            | 302            |             | -      | -                 | -             | 22            | 10                | 14                |

| 3     |     | 603            | 303            |             | 11     | 5                 | 17            | 20            | 13                | 13                |

| 4     |     | 604            | 304            |             | 9      | 3                 | 15            | 18            | 14                | 12                |

| 5     |     | 605            | 305            |             | 8      | 2                 | 14            | 17            | 11                | 9                 |

| 6     |     | 606            | 306            |             | -      | -                 | 13            | 16            | 10                | 8                 |

| 7     |     | 607            | 307            |             | -      | -                 | -             | 15            | 8                 | 6                 |

| 8     |     | No Casout 608  | 308            |             | 7      | 1                 | 12            | 14            | 6                 | 4                 |

| 9     |     | 609            | 309            |             | -      | -                 | 10            | 12            | 4                 | 100               |

| 10    |     | 610            | 310            |             | -      | -                 | -             | 11            | 3                 | 99                |

| 11    |     | 611            | 311            |             | 6      | 44                | 9             | 10            | 100               | 98                |

| 12    |     | 612            | 312            |             | -      | -                 | 8             | 9             | 99                | 97                |

| 13    |     | 613            | 313            |             | -      | -                 | 7             | 8             | 98                | 96                |

| 14    |     | 614            | 314            |             | 5      | 43                | 5             | 6             | 96                | 94                |

| 15    |     | 615            | 315            |             | -      | -                 | -             | 5             | 95                | 93                |

| 16    |     | No Casout 616  | 316            |             | 4      | 42                | 4             | 4             | 94                | 92                |

| 17    | В   | 617            | 317            |             | 21     | 15                | 33            | 41            | 39                | 37                |

| 18    |     | 618            | 318            |             | -      | -                 | -             | 40            | 38                | 36                |

| 19    |     | 619            | 319            |             | 20     | 14                | 32            | 39            | 37                | 35                |

| 20    |     | 620            | 320            |             | 19     | 13                | 30            | 37            | 35                | 33                |

| 21    |     | 621            | 321            |             | 18     | 12                | 29            | 36            | 34                | 32                |

| 22    |     | 622            | 322            |             | -      | -                 | 28            | 35            | 33                | 31                |

| 23    |     | 623            | 323            |             | -      | -                 | -             | 34            | 32                | 30                |

| 24    |     | No Casout 624  | 324            |             | 17     | 11                | 27            | 33            | 31                | 29                |

| 25    |     | 625            | 325            |             | 16     | 10                | 25            | 31            | 27                | 25                |

| 26    |     | 626            | 326            |             | -      | -                 | -             | 30            | 25                | 23                |

| 27    |     | 627            | 327            |             | -      | -                 | 24            | 29            | 23                | 21                |

| 28    |     | 628            | 328            |             | -      | -                 | 23            | 28            | 22                | 20                |

| 29    |     | 629            | 329            |             | -      | -                 | 22            | 27            | 21                | 19                |

| 30    |     | 630            | 330            |             | 14     | 8                 | 20            | 25            | 19                | 17                |

| 31    |     | 631            | 331            |             | -      | -                 | -             | 24            | 18                | 16                |

| 32    |     | No Casout 632  | 332            |             | 13     | 7                 | 19            | 23            | 17                | 15                |

| 33    | С   | 633            | 333            |             | 24     | 18                | 36            | 44            | 42                | 40                |

| 34    |     | 634            | 334            |             | -      | -                 | -             | 45            | 43                | 41                |

| 35    |     | 635            | 335            |             | 25     | 19                | 37            | 46            | 44                | 42                |

| 36    |     | 636            | 336            |             | 26     | 20                | 39            | 48            | 46                | 44                |

| 37    |     | 637            | 337            |             | 27     | 21                | 40            | 49            | 47                | 45                |

| 38    |     | 638            | 338            |             | -      | -                 | 41            | 50            | 48                | 46                |

| 39    |     | 639            | 339            |             | -      | -                 | -             | 51            | 49                | 47                |

| 40    |     | No Casout 640  | 340            |             | 28     | 22                | 42            | 52            | 50                | 48                |

| 41    |     | 641            | 341            |             | 29     | 23                | 44            | 54            | 54                | 52                |

| 42    |     | 642            | 342            |             | -      | -                 | -             | 55            | 56                | 54                |

| 43    |     | 643            | 343            |             | -      | -                 | 45            | 56            | 58                | 56                |

| 44    |     | 644            | 344            |             | -      | -                 | 46            | 57            | 59                | 57                |

| 45    |     | 645            | 345            |             | -      | -                 | 47            | 58            | 60                | 58                |

| 46    |     | 646            | 346            |             | 31     | 25                | 49            | 60            | 62                | 60                |

| 47    |     | 647            | 347            |             | -      | -                 | -             | 61            | 63                | 61                |

| 48    |     | No Casout 648  | 348            |             | 32     | 26                | 50            | 62            | 64                | 62                |

|    | ATF1504xx Pin/Node Worksheet Cont'd |               |          |             |        |        |        |        |         |         |  |

|----|-------------------------------------|---------------|----------|-------------|--------|--------|--------|--------|---------|---------|--|

| MC | LAB                                 | Feedback      | Foldback | Signal Name |        | Pinout |        |        |         |         |  |

|    |                                     | Node          | Node     |             | 44-Pin | 44-Pin | 68-Pin | 84-Pin | 100-Pin | 100-Pin |  |

|    |                                     | Number        | Number   |             | PLCC   | TQFP   | PLCC   | PLCC   | PQFP    | TQFP    |  |

| 49 | D                                   | 649           | 349      |             | 33     | 27     | 51     | 63     | 65      | 63      |  |

| 50 |                                     | 650           | 350      |             | -      | -      | -      | 64     | 66      | 64      |  |

| 51 |                                     | 651           | 351      |             | 34     | 28     | 52     | 65     | 67      | 65      |  |

| 52 |                                     | 652           | 352      |             | 36     | 30     | 54     | 67     | 69      | 67      |  |

| 53 |                                     | 653           | 353      |             | 37     | 31     | 55     | 68     | 70      | 68      |  |

| 54 |                                     | 654           | 354      |             | -      | -      | 56     | 69     | 71      | 69      |  |

| 55 |                                     | 655           | 355      |             | -      | -      | -      | 70     | 73      | 71      |  |

| 56 |                                     | No Casout 656 | 356      |             | 38     | 32     | 57     | 71     | 75      | 73      |  |

| 57 |                                     | 657           | 357      |             | 39     | 33     | 59     | 73     | 77      | 75      |  |

| 58 |                                     | 658           | 358      |             | -      | -      | -      | 74     | 78      | 76      |  |

| 59 |                                     | 659           | 359      |             | -      | -      | 60     | 75     | 81      | 79      |  |

| 60 |                                     | 660           | 360      |             | -      | -      | 61     | 76     | 82      | 80      |  |

| 61 | ]                                   | 661           | 361      |             | -      | -      | 62     | 77     | 83      | 81      |  |

| 62 | ]                                   | 662           | 362      |             | 40     | 34     | 64     | 79     | 85      | 83      |  |

| 63 | ]                                   | 663           | 363      |             | -      | -      | -      | 80     | 86      | 84      |  |

| 64 |                                     | No Casout 664 | 364      |             | 41     | 35     | 65     | 81     | 87      | 85      |  |

# Table 3-4. ATF1504xx Pin/Node List

Table 3-5 lists the Pin and Node numbers for the **ATF1508xx** device in various packages. It is preferred that Foldback node numbers as well as Buried Feedback node numbers are not preassigned in the Source files.

| MC    | LAB | Feedback      | Foldback | Signal Name | Р      | Pinout for ATF1508xx |         |         |  |

|-------|-----|---------------|----------|-------------|--------|----------------------|---------|---------|--|

|       |     | Node          | Node     |             | 84-Pin | 100-Pin              | 100-Pin | 160-Pin |  |

|       |     | Number        | Number   |             | PLCC   | PQFP                 | TQFP    | PQFP    |  |

| INPUT |     | none          | none     | (OE2/GCLK2) | 2      | 92                   | 90      | 142     |  |

| INPUT |     | none          | none     | (GCLK1)     | 83     | 89                   | 87      | 139     |  |

| INPUT |     | none          | none     | (GCLR)      | 1      | 91                   | 89      | 141     |  |

| INPUT |     | none          | none     | (OE1)       | 84     | 90                   | 88      | 140     |  |

| 1     | Α   | 601           | 301      |             |        | 4                    | 2       | 160     |  |

| 2     |     | 602           | 302      |             |        |                      |         |         |  |

| 3     |     | 603           | 303      |             | 12     | 3                    | 1       | 159     |  |

| 4     |     | 604           | 304      |             |        |                      |         | 158     |  |

| 5     |     | 605           | 305      |             | 11     | 2                    | 100     | 153     |  |

| 6     |     | 606           | 306      |             | 10     | 1                    | 99      | 152     |  |

| 7     |     | 607           | 307      |             |        |                      |         |         |  |

| 8     |     | No Casout 608 | 308      |             | 9      | 100                  | 98      | 151     |  |

| 9     |     | 609           | 309      |             |        | 99                   | 97      | 150     |  |

| 10    |     | 610           | 310      |             |        |                      |         |         |  |

| 11    |     | 611           | 311      |             | 8      | 98                   | 96      | 149     |  |

| 12    |     | 612           | 312      |             |        |                      | -       | 147     |  |

| 13    |     | 613           | 313      |             | 6      | 96                   | 94      | 146     |  |

| 14    |     | 614           | 314      |             | 5      | 95                   | 93      | 145     |  |

| 15    |     | 615           | 315      |             |        |                      |         |         |  |

| 16    |     | No Casout 616 | 316      |             | 4      | 94                   | 92      | 144     |  |

| 17    | В   | 617           | 317      |             | 22     | 16                   | 14      | 21      |  |

| 18    |     | 618           | 318      |             |        |                      |         |         |  |

| 19    |     | 619           | 319      |             | 21     | 15                   | 13      | 20      |  |

| 20    |     | 620           | 320      |             |        |                      |         | 19      |  |

| 21    |     | 621           | 321      |             | 20     | 14                   | 12      | 18      |  |

| 22    |     | 622           | 322      |             |        | 12                   | 10      | 16      |  |

| 23    |     | 623           | 323      |             |        |                      |         |         |  |

| 24  |     | No Casout 624 | 324          |              | 18        | 11      | 9       | 15      |

|-----|-----|---------------|--------------|--------------|-----------|---------|---------|---------|

| 25  |     | 625           | 325          |              | 17        | 10      | 8       | 14      |

|     |     | ATI           | F1508xx Pin/ | Node Workshe | et Cont'd |         |         |         |

| MC  | LAB | Feedback      | Foldback     | Signal Name  |           | Pin     | out     |         |

|     |     | Node          | Node         |              | 84-Pin    | 100-Pin | 100-pin | 160-Pin |

|     |     | Number        | Number       |              |           | PQFP    | TQFP    | PQFP    |

| 26  | В   | 626           | 326          |              |           |         |         |         |

| 27  |     | 627           | 327          |              | 16        | 9       | 7       | 13      |

| 28  |     | 628           | 328          |              |           |         |         | 12      |

| 29  |     | 629           | 329          |              | 15        | 8       | 6       | 11      |

| 30  |     | 630           | 330          |              |           | 7       | 5       | 10      |

| 31  |     | 631           | 331          |              |           |         |         |         |

| 32  |     | No Casout 632 | 332          |              | 14        | 6       | 4       | 9       |

| 33  | С   | 633           | 333          |              |           | 27      | 25      | 41      |

| 34  |     | 634           | 334          |              |           |         |         |         |

| 35  |     | 635           | 335          |              | 31        | 26      | 24      | 33      |

| 36  |     | 636           | 336          |              |           |         |         | 32      |

| 37  |     | 637           | 337          |              | 30        | 25      | 23      | 31      |

| 38  |     | 638           | 338          |              | 29        | 24      | 22      | 30      |

| 39  |     | 639           | 339          |              |           |         |         |         |

| 40  |     | No Casout 640 | 340          |              | 28        | 23      | 21      | 29      |

| 41  |     | 641           | 341          |              |           | 22      | 20      | 28      |

| 42  |     | 642           | 342          |              |           |         |         |         |

| 43  |     | 643           | 343          |              | 27        | 21      | 19      | 27      |

| 44  |     | 644           | 344          |              |           |         |         | 25      |

| 45  |     | 645           | 345          |              | 25        | 19      | 17      | 24      |

| 46  |     | 646           | 346          |              | 24        | 18      | 16      | 23      |

| 47  |     | 647           | 347          |              |           |         |         |         |

| 48  |     | No Casout 648 | 348          |              | 23        | 17      | 15      | 22      |

| 49  | D   | 649           | 349          |              | 41        | 39      | 37      | 59      |

| 50  |     | 650           | 350          |              |           |         |         |         |

| 51  |     | 651           | 351          |              | 40        | 38      | 36      | 58      |

| 52  |     | 652           | 352          |              |           |         |         | 57      |

| 53  |     | 653           | 353          |              | 39        | 37      | 35      | 56      |

| 54  |     | 654           | 354          |              |           | 35      | 33      | 54      |

| 55  |     | 655           | 355          |              |           |         |         |         |

| 56  |     | No Casout 656 | 356          |              | 37        | 34      | 32      | 53      |

| 57  |     | 657           | 357          |              | 36        | 33      | 31      | 52      |

| 58  |     | 658           | 358          |              |           |         |         |         |

| 59  |     | 659           | 359          |              | 35        | 32      | 30      | 51      |

| 60  |     | 660           | 360          |              |           |         |         | 50      |

| 61  |     | 661           | 361          |              | 34        | 31      | 29      | 49      |

| 62  |     | 662           | 362          |              |           | 30      | 28      | 48      |

| 63  |     | 663           | 363          |              |           |         |         |         |

| 64  | 1   | No Casout 664 | 364          | T            | 33        | 29      | 27      | 43      |

| 128 | н   | 728           | 428          | T            | 81        | 87      | 85      | 137     |

| 127 | 1   | 727           | 427          |              |           |         |         |         |

| 126 | 1   | 726           | 426          |              | 80        | 86      | 84      | 136     |

| 125 | 1   | 725           | 425          |              | 79        | 85      | 83      | 135     |

| 124 | 1   | 724           | 424          |              |           |         |         | 134     |

| 123 | 1   | 723           | 423          |              | 77        | 83      | 81      | 132     |

| 122 | 1   | 722           | 422          |              |           |         | -       |         |

| 121 | 1   | No Casout 721 | 421          |              |           | 82      | 80      | 131     |

| 120 | 1   | 720           | 420          |              | 76        | 81      | 79      | 130     |

| 119 | 1   | 719           | 419          |              |           |         |         |         |

| 118 | 1   | 718           | 418          |              | 75        | 80      | 78      | 129     |

| 117 | 1   | 717           | 417          |              | 73        | 79      | 70      | 123     |

| 116 | 1   | 716           | 416          |              |           |         |         | 123     |

| 115 |     | 715           | 415      |             | 73        | 78      | 76   | 122     |

|-----|-----|---------------|----------|-------------|-----------|---------|------|---------|

| 114 |     | 714           | 414      |             |           |         | 10   |         |

| 113 |     | No Casout 713 | 413      |             |           | 77      | 75   | 121     |

| 112 | G   | 712           | 412      |             | 71        | 75      | 73   | 112     |

| 111 | •   | 711           | 411      |             |           |         |      |         |

| 110 |     | 710           | 410      |             |           | 74      | 72   | 111     |

|     |     |               |          | ode Workshe | at Cont'd |         |      |         |

| МС  | LAB | Feedback      | Foldback | Signal Name | et Cont u |         | out  |         |

| WIC | LAD | Node          | Node     | Signal Name | 84-Pin    | 100-Pin |      | 160-Pin |

|     |     | Number        | Number   |             | 04-F111   | PQFP    | TQFP | PQFP    |

| 109 | G   | 709           | 409      |             | 70        | 73      | 71   | 110     |

| 103 | U   | 708           | 408      |             |           |         |      | 109     |

| 100 |     | 707           | 407      |             | 69        | 72      | 70   | 108     |

| 107 |     | 706           | 406      |             |           |         | 10   |         |

| 105 |     | No Casout 705 | 405      |             | 68        | 71      | 69   | 107     |

| 100 |     | 704           | 404      |             | 67        | 70      | 68   | 107     |

| 104 |     | 703           | 403      |             |           |         |      |         |

| 103 |     | 702           | 402      |             |           | 69      | 67   | 105     |

| 102 |     | 701           | 401      |             | 65        | 67      | 65   | 103     |

| 100 |     | 700           | 400      |             |           |         |      | 100     |

| 99  |     | 699           | 399      |             | 64        | 66      | 64   | 101     |

| 98  |     | 698           | 398      |             |           |         |      |         |

| 97  |     | No Casout 697 | 397      |             | 63        | 65      | 63   | 100     |

| 96  | F   | 696           | 396      |             | 62        | 64      | 62   | 99      |

| 95  |     | 695           | 395      |             |           |         | -    |         |

| 94  |     | 694           | 394      |             | 61        | 63      | 61   | 98      |

| 93  |     | 693           | 393      |             | 60        | 62      | 60   | 97      |

| 92  |     | 692           | 392      |             |           |         |      | 96      |

| 91  |     | 691           | 391      |             | 58        | 60      | 58   | 94      |

| 90  |     | 690           | 390      |             |           |         |      |         |

| 89  |     | No Casout 689 | 389      |             |           | 59      | 57   | 93      |

| 88  |     | 688           | 388      |             | 57        | 58      | 56   | 92      |

| 87  |     | 687           | 387      |             |           |         |      |         |

| 86  |     | 686           | 386      |             | 56        | 57      | 55   | 91      |

| 85  |     | 685           | 385      |             | 55        | 56      | 54   | 90      |

| 84  |     | 684           | 384      |             |           |         |      | 89      |

| 83  |     | 683           | 383      |             | 54        | 55      | 53   | 88      |

| 82  |     | 682           | 382      |             |           |         |      |         |

| 81  |     | No Casout 681 | 381      |             |           | 54      | 52   | 80      |

| 80  | Е   | 680           | 380      |             | 52        | 52      | 50   | 78      |

| 79  |     | 679           | 379      |             |           |         |      |         |

| 78  |     | 678           | 378      |             |           | 51      | 49   | 73      |

| 77  |     | 677           | 377      |             | 51        | 50      | 48   | 72      |

| 76  |     | 676           | 376      |             |           |         |      | 71      |

| 75  |     | 675           | 375      |             | 50        | 49      | 47   | 70      |

| 74  |     | 674           | 374      |             |           |         |      |         |

| 73  |     | No Casout 673 | 373      |             | 49        | 48      | 46   | 69      |

| 72  |     | 672           | 372      |             | 48        | 47      | 45   | 68      |

| 71  |     | 671           | 371      |             |           |         |      |         |

| 70  |     | 670           | 370      |             |           | 46      | 44   | 67      |

| 69  |     | 669           | 369      |             | 46        | 44      | 42   | 65      |

| 68  |     | 668           | 368      |             |           |         |      | 64      |

| 67  |     | 667           | 367      |             | 45        | 43      | 41   | 63      |

| 66  |     | 666           | 366      |             |           |         |      |         |

| 65  |     | 665           | 365      |             | 44        | 42      | 40   | 62      |

# Table 3-5. ATF1508xx Pin/Node List

# 3.4 Operation

The ATF15xx family of fitters have been developed to run automatically in PROCHIP, ALTIUM (PROTEL) DESIGN EXPLORER 99SE Tool, ATMEL-SYNARIO V4.11 and ATMEL WinCUPL. Users can specify the device type in the source/Project file and the appropriate tool compiler will automatically execute the ATF15xx fitter software. You can customize fitter operation for ABEL or CUPL designs by using the DOS command line, PROPERTY statements or macros in the source file. These methods will be discussed in more detail later in this manual.

# 3.4.1 VHDL Designs (Prochip environment)

For VHDL Designs, you can compile the Source files using PROCHIP tools into a Netlist (EDIF 2.0). Once the EDIF file is generated, you can use the GUI from Prochip to invoke the **Device Fitter** properties window and select the *Global Device Parameters* or *Pin/Node options* to specify individual pin or MC properties. Users can click on the RUN FITTER button as shown in the Figure 3-1 to generate the Fitter Report File (.FIT) and the .JED (JEDEC programming file)

| Global Configuration<br>JTAG<br>JTAG<br>TDI Pullup<br>TMS Pullup<br>Power Save<br>Pin Power Down 1<br>Pin Power Down 2<br>Auto Wake<br>GCK1 Wake<br>GCK2 Wake<br>GCK3 Wake<br>Simulation<br>Generate Sim Files<br>Security<br>Secure Part | Power Reset <ul> <li>Large Hysteresis</li> <li>Small Hysteresis</li> </ul> Pin Fit Control           O Ignore           O keep           O Try           Device Logic Options           Pin Keeper           Optimize           Latch Synthesis           Global Output Enable           Global Reset | Logic Node Defaults<br>Fast Input<br>Power Save<br>Fast Slew<br>Soft Buffer<br>Enable Foldback<br>Force Foldback<br>Enable Cascade<br>Enable XOR Syn.<br>Open Collector<br>Logic Double<br>O if nesseccary<br>Always | Global Devic<br>Pin/Node Or |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| unFitter Set Defaults                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                       | Can                                                                                                                                                                                                                  | cel Help                    |

Figure 3-1

# 3.4.2 VHDL Designs (ATMEL-Synario environment)

In ATMEL-SYNARIO, Source vhdl (.vhd) files can be synthesized into PLA format (.tt2) files. The target device can be selected from a list of ATMEL devices. Alternatively, Fitters can also be run from the DOS prompt by clicking on the 'CTRL"-"ALT"-"D" keys simultaneously. Section 3.2.2 describes the syntax/command.

# 3.4.3 ABEL Designs (ATMEL-Synario and Legacy ABEL 5.1x)

In ATMEL-SYNARIO, Source ABEL (.abl) files can be synthesized into PLA format (.tt2) files. The target device can be selected from a list of ATMEL devices. Alternatively, Fitters can also be run from the DOS prompt by clicking on the 'CTRL"-"ALT"-"D" keys simultaneously. Section 3.2.2 describes the syntax/command.

In the DOS ABEL (Legacy ABEL 5.1x) environment if you are targetting the ATF1500A, enter the target device type by selecting the

#### Fit Options..

command from the ABEL SmartPart Menu. Enter the p1500a or p1500at device type and press F5 key to exit.

Then select the

Fit

command from the SmartPart Menu to run the fitter and create the JEDEC file.

An alternate way to target the ATF1500 device is to include the appropriate ABEL device type shown in Table 3-1 in your ABEL design file by using the *Device* Statement. Then select the *Fit* Command above from the SmartPart menu to run the fitter.

Windows ABEL (ABEL 6.x) or ATMEL-SYNARIO users should select the ATF1500A device in your project and execute the **Create Jedec File** Process. The fitter will be executed automatically.

## 3.4.4 CUPL/Schematic Designs (Prochip environment)

For CUPL/Schematic Designs, you can compile the Source files using PROCHIP tools. All Schematic files are first translated into a CUPL (.pld) file using the "virtual" device type. This file is then compiled into a PLA (.tt2) file. Once the PLA file is generated, you can use the GUI from Prochip to invoke the **Device Fitter** properties window and select the Global Parameters or Advanced options to specify individual pin or MC properties. Users can click on the RUN FITTER button to generate the Fitter Report File (.FIT) and the .JED (JEDEC programming file)

CUPL or Schematic Designs can alternatively be directly compiled using **DESIGN EXPLORER 99SE TOOL** from ALTIUM (formerly known as PROTEL).

## 3.4.5 CUPL (ATMEL- WinCUPL)

**ATMEL-WINCUPL** is the windows version of CUPL and is specific to the ATMEL device library only. All Atmel EPLDs are supported. Users can either specify the device mnemonic in the Header section as shown in Figure 3-2.

```

Name

Reglatch;

Partno

;

01;

Revision

8/11/95;

Date

Designer

PLD Expert;

Company

Atmel Corp.;

Location

None;

Assembly

None;

Device

F1500a; /*Device mnemonic is specified in the Header section*/

/* Example showing register and latch usage */

```

#### Figure 3-2

For a list of devices, users can reference the **Help.Atmel INFO** button from within ATMEL-WinCUPL. Users are not required to remember the device mnemonic and can alternatively select the appropriate Atmel Device and then proceed to Compile. As shown in Figure 3-3, users can click on the **OPTIONS** button and then select the **Devices** option

| 🛗 WinCupl: Atr                 | nel Version                                  |                             |

|--------------------------------|----------------------------------------------|-----------------------------|

| <u>F</u> ile <u>E</u> dit ⊻iew | <u>Options</u> <u>R</u> un <u>U</u> tilities | <u>W</u> indow <u>H</u> elp |

| 0 🛋 🖬 🖉                        | <u>C</u> ompiler Ctrl+W                      | 1 5 7 👪 🏧 🚥                 |

|                                | <u>D</u> evices Ctrl+D                       |                             |

| 🛗 C:\WINCUP                    | <u>S</u> imulator Ctrl+L                     | \REGLATCH.PLD               |

| Name                           | WinCUPL                                      |                             |

| Partno                         |                                              |                             |

| Revision                       | 01;                                          |                             |

| Date                           | 8/11/95;                                     |                             |

| Designer                       | PLD Expert;                                  |                             |

| Company                        | Atmel Corp.;                                 |                             |

| Location                       | None;                                        |                             |

| Assembly                       | None;                                        |                             |

| Device                         | F1500a;                                      |                             |

| /* Example s                   | howing register ar                           | nd latch usage */           |

Figure 3-3

This brings up the GUI as shown in Figure 3-4. All ATMEL EPLDs are classified by package type. Please **deselect** (**Uncheck**) the **Device in File** option so that the WinCupl Compiler will only use the Device type selected in this GUI for the compilation process.

| Device Selection                                                                                                                                  |                              |                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package Type<br>DIP<br>PLCC<br>PQFP<br>TQFP                                                                                                       | Manufacturer<br>Atmel        | Devices<br>ATF1500<br>ATF1500A<br>ATF1502AS PLCC44<br>ATF1502AS PLCC44-ISP<br>ATF1504AS PLCC44-ISP<br>ATF1504AS PLCC48<br>ATF1504AS PLCC68<br>ATF1504AS PLCC68-ISP |

| Device Information<br>Mnemonic: f1502plcc44<br>Pin Count: 44<br>Special Options: None<br>Alternate Part Numbers: ATF15<br>Related Mnemonics: None | 02AS, ATF1502ASL, ATF1502AS\ | /, ATF1502ASVL                                                                                                                                                     |

| Device Mnemonic<br>[1502plcc44                                                                                                                    | 🔽 Device In File             | <u>O</u> k <u>C</u> ancel                                                                                                                                          |

Figure 3-4

# 3.4.6 CUPL and MCUPL (Legacy versions of CUPL)

The following table lists the flow applicable to the old ATF1500/A devices. For new designs, we recommend that customers always use ATMEL-WinCUPL.

| MCUPL (Legacy CUPL V4.x) Flow                                                       | CUPL (Legacy CUPL4.7x)                                               |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| To use the ATF1500 fitter in MCUPL: select the,                                     | You may compile your design in CUPL from the                         |

|                                                                                     | DOS command line. Type,                                              |

| <d>evice selection</d>                                                              |                                                                      |

|                                                                                     | CUPL -J{option list} <filename> <return></return></filename>         |

| command from the main menu to choose the                                            |                                                                      |

| appropriate ATF1500 CUPL device type, if it is not                                  | at the command line. You must specify at least the <b>-</b> <i>J</i> |

| already included in your source file. Then Select,                                  | option. Additional options can be specified. To view                 |

|                                                                                     | these options type,                                                  |

| <c>ompile Design File</c>                                                           |                                                                      |

|                                                                                     | CUPL <return></return>                                               |

| Use F3 to change the DOS subdirectory, if                                           |                                                                      |

| necessary. Select the file and press <i><return></return></i> .                     | For example,                                                         |

|                                                                                     |                                                                      |

| An output options menu will appear. Select at least                                 | CUPL -jxf c:\fit1500\project\project.pld                             |

| the                                                                                 |                                                                      |

|                                                                                     | will instruct CUPL to compile the <i>project.pld</i> file            |

| <j>edec File Output</j>                                                             | located in the c:\fit1500\project\ directory. The -x                 |

|                                                                                     | and -f options specify expanded product terms and a                  |

| option to run the fitter. Press the <b>F5</b> key to start the compilation process. | fuse map listing to be produced by CUPL.                             |

# 3.4.7 Command Line

The ATF15xx fitter can also be executed from the DOS command line. The command line is shown below for ATF1500A and ATF1502AS. A detailed description of each option will be discussed in the section 4.0 of this manual.

| -o output_file_name (for *.tt3 and *.jed)-log report_file (*.doc)-err error_file (*.err)-device (p1500/ p1500t/ f1500/ f1500t)-preassign TRY/Keep/IGNore (pin preassignment<br>options)-silent (no message on screen)-2-2-3-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-4-5-6-6-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7< |