# Beschreibung und technische Daten: Minicomputer-Platine 68k1.2

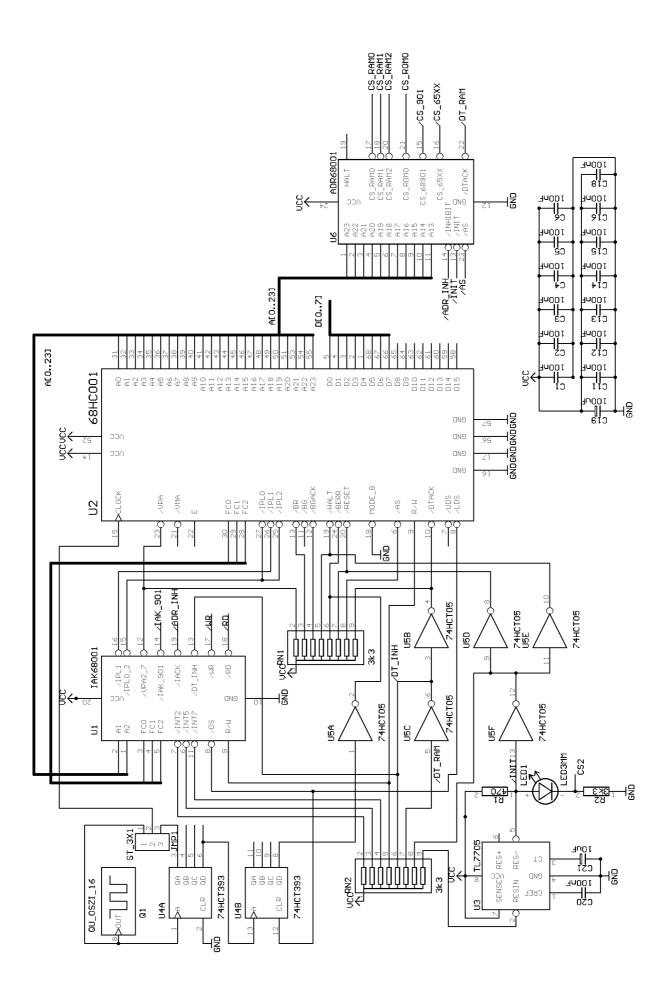

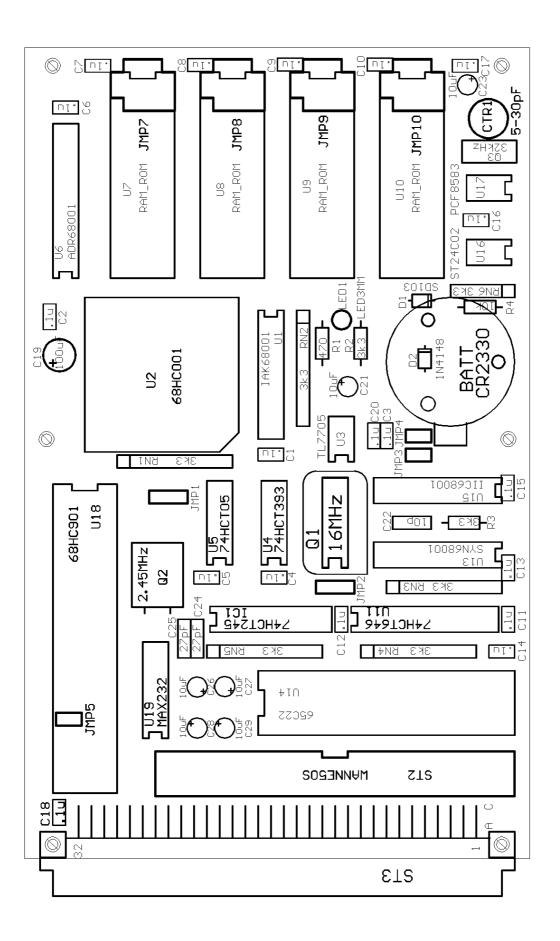

Auf einer Leiterplatte im Format 160 \* 100 mm² befinden sich neben der Motorola **CPU MC68HC001** folgende Schaltkreise:

**V**ersatile Interface **A**dapter **R65C22** mit je 2 x 8bit-Port, 4 Steuersignalen (handshake), 2 x Timer und Schieberegister;

**M**ulti **F**unction **P**erifheral **MC68HC901** mit 1 x 8bit-Port, 4 x Timer, serielle Schnittstelle und diversen Interruptmöglichkeiten (vektorisiert);

4 x 28 Pin Fassungen für **RAM 6264-62256** mit Batteriepufferung und **EPROM 2764-27512**;

MAX232 (optional) ser. Schnittstellentreiber

PCF8583 (optional) IIC-Uhrenbaustein mit RAM

**ST24C02** (optional) (-4, -8) IIC-EEPROM mit 256, 512 oder 1024 bytes

**TL7705** Resetschaltung sowie Logik-Bausteine für Adressdekodierung, Interruptverarbeitung, Synchronisierung der 65Cxx-Peripherie, IIC-Bus Port, Takterzeugung und eine Lithiumbatterie zur Pufferung von RAM und Uhr.

Als Stromversorgung wird eine einzige Spannungsquelle 5 Volt benötigt. Die Versorgungspannung der V.24-Treiber wird auf der Rechnerkarte erzeugt.

Es werden weitgehend Bausteine in CMOS- oder stromsparender Ausführung verwendet. Die Stromaufnahme liegt daher bei 8MHz-CPU-Takt bei typ. 180mA, 5 Volt; die Stromaufnahme erhöht sich nur leicht, wenn eine 12MHz oder 16MHz CPU eingesetzt wird.

Alle Signale von **VIA** und **MFP** sind auf eine 64-pol. VG-Leiste (a+c) geführt und teilweise auf einem 50-pol. Adapterstecker für Huckepack-Platinen vorhanden. Zudem steht ein gepufferter Adress- und Datenbus (A0-A7, D0-D7, /CS0, /CS1, R/W, Phi2) zum direkten Anschluß von externen 65xx/68xx-Schaltkreisen zur Verfügung.

#### CPU MC68HC001:

Dies ist eine 68000 CPU in CMOS Technik, die sich statisch auf 8 oder 16-bit Datenbusbreite einstellen läßt. Der Adressraum umfaßt 16MB. Sie wird in dieser Schaltung wie eine 68008 CPU (8-Bit Datenbusbreite) mit erweitertem Adressraum verwendet. Die Interrupts sind auf Ebenen 2, 5 und 7 begrenzt. Es können CPUs mit 8, 12 oder 16MHz Clock-Frequenz eingesetzt werden, ohne daß wait-states eingefügt werden müssen.

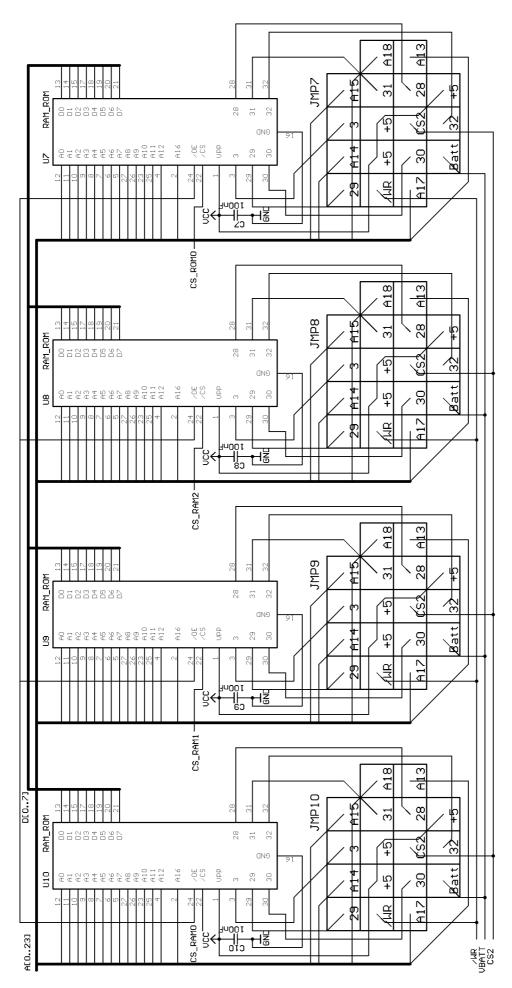

#### RAM/EPROM:

Es sind 4 Fassungen vorhanden, in die 28-polige Speicherbausteine gesteckt werden können. Zu jeder Fassung gibt es ein 17-poliges Feld zur Konfiguration des verwendeten Speicherbausteins. Fassung U10 muß immer mit RAM (ab Adresse 0x0) und U7 immer mit den Start-EPROM (Vektoren für stack/reset) bestückt werden. Die zwischenliegenden Fassungen können beliebig verwendet werden. Mit dem Adressdekoder 'ADR68001' wird folgende Standard-Adressbelegung vorgegeben:

| U10 | 0x000000 - 0x01FFFF | immer RAM, 8k - 128k  | typ. RAM 6264    |

|-----|---------------------|-----------------------|------------------|

| U9  | 0x020000 - 0x03FFFF | RAM / EPROM max. 128k | typ. RAM 6264    |

| U8  | 0x040000 - 0x05FFFF | RAM / EPROM max. 128k | typ. EPROM 27256 |

| U7  | 0x100000 - 0x17FFFF | immer EPROM max. 512k | typ. EPROM 27256 |

Die Bausteine 6264 (8k) und 628128 (128k) können wegen ihres CS2-Eingangs batteriegepuffert werden. Somit lassen sich mit der 68k1.2-Platine Anwendungen mit 384k gepuffertem RAM und 512k EPROM realisieren.

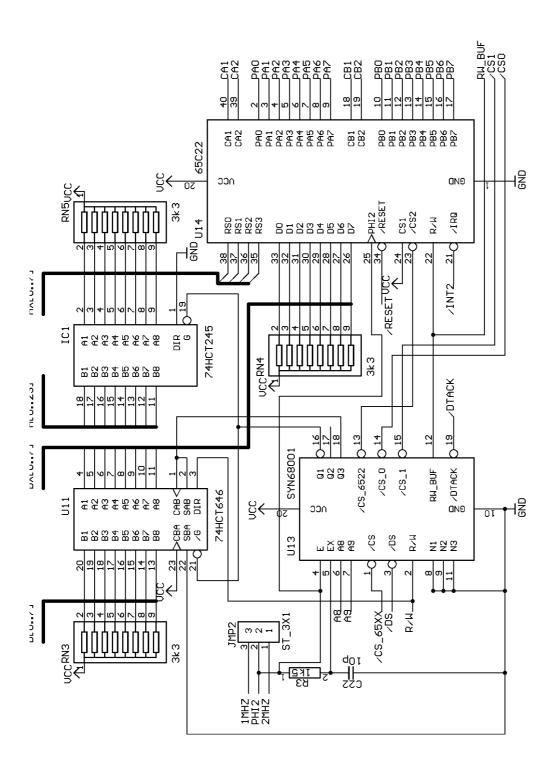

#### VIA R65C22:

Dies ist ein sehr vielseitig einsetzbarer Baustein, der 2 x 8bit-Ports, 2 x Timer, Kontrolleitungen und ein synchrones Schieberegister beinhaltet. Für nähere Information wird auf das Datenblatt verwiesen.

Die Register der VIA sind an den fortlaufenden Byte-Adressen ab der Basisadresse 0xFFFFF00 ansprechbar.

Alle Signale der VIA sind auf die VG-Leiste und den 50-pol. Erweiterungsstecker geführt. Für den Betrieb der VIA und weiterer 65xx/68xx-Bausteine wird auf der Karte ein synchrones Interface zur Verfügung gestellt, welches mit 1 oder 2MHz (standard) Takt-Frequenz arbeitet. Für Interrupts ist der AUTOINT 2 durch das GAL 'IAK68001' vorgesehen.

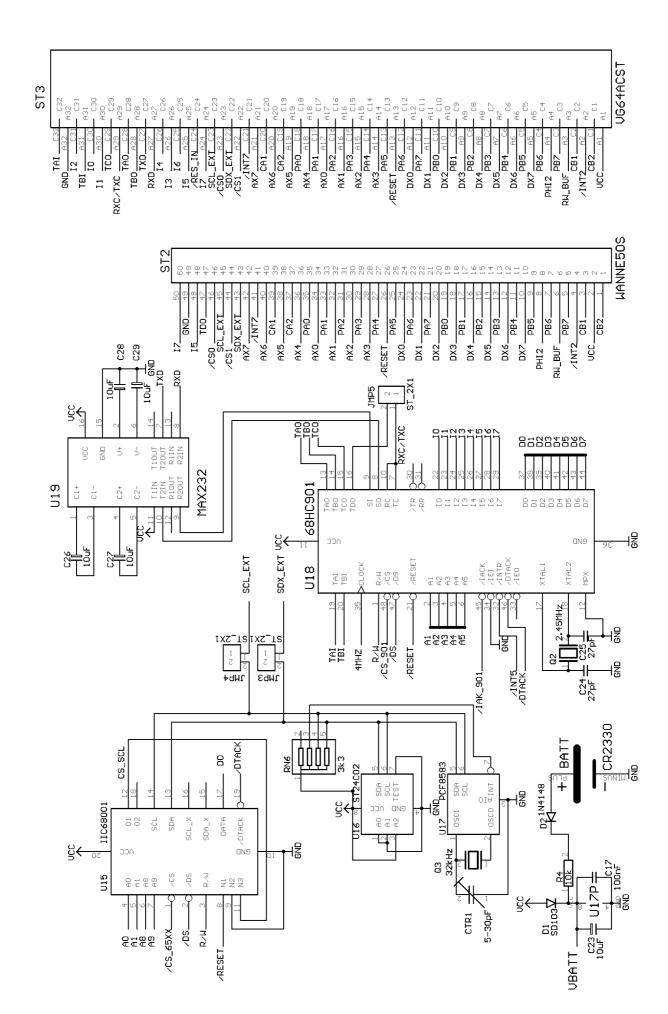

#### MFP MC68HC901:

Dieser Baustein beinhaltet ein 8bit I/O-Port, 4 x Timer und eine serielle Schnittstelle mit diversen Interruptmöglichkeiten. Die Timer, die ser. Schnittstelle und jede Leitung des I/O-Ports können Interrupts über insgesamt 16 Vektoren auslösen. Die Interruptlogik GAL 'IAK68001' verwendet für den MFP die INT5-Ebene mit einzelnen Vektoren.

Der Baustein MC68HC901 ist ab der Basisadresse 0xFFFFC000 an geraden oder ungeraden Adressen ansprechbar, wobei der Abstand zum nächsten Register jeweils zwei Byte beträgt.

Der Baudrate x 16-Takt der seriellen Schnittstelle wird normalerweise über TIMER D (Brücke JMP5) und den Quarzoszillator 2,457 MHz erzeugt. Die Taktfrequenz des Oszillators wird auch für Timer A - C verwendet. Hierzu weitere Informationen im Datenblatt zum MFP.

# IIC-Bus (optional):

Mit dem GAL 'IIC68001' wird ein quasi-bidirektionaler 2 bit-Port für IIC-Bus Bausteine gebildet, um externe Bausteine oder die auf der Rechnerkarte verwendeten Bausteine Uhr/RAM und EEPROM anzusprechen.

Um die IIC-Bus-Signale SCL und SDA extern verwenden zu können, müssen die Brücken JMP3 und JMP4 gesteckt/gelötet sein.

Es werden jeweils bit 0 der Adressen 0xFFFFD00 (SCL) und 0xFFFFD01 (SDA) verwendet. In Verbindung mit den zugehörigen pullup-Widerständen ergibt sich ein Eingang, wenn eine '1' in das betreffende Register geschrieben wird und ein low-Ausgang, wenn eine '0' geschrieben wird. Die Ports verhalten sich wie rücklesbare open-collector-Ausgänge.

Das GAL 'IIC68001' befindet sich zwar im 65xx-Adressbereich, generiert aber selbst ein /DTACK-Signal, um die Zugriffe zu beschleunigen. Das GAL kann auch entfallen, wobei die Zugriffe auf diesen Adressbereich auf den Phi2-Takt synchronisiert werden und keinen Bus-Error auslösen.

# Uhr/RAM PCF8583 (optional):

Dieser Baustein wird über die IIC-Bus-Adresse 0xA0 angesprochen und enthält eine Uhr, Alarmregister und 240 Byte RAM. Nähere Information hierzu im Datenblatt des Bausteins. Für die Uhr ist ein 32kHz-Quarz mit Abgleichtrimmkondensator vorhanden, mit dem die Taktfrequenz der Uhr genau eingestellt werden kann.

Die Taktfrequenz ist abgeglichen, wenn an Pin 7 des Uhrenbausteins ein exaktes 1Hz Signal gemessen wird. Beim Abgleich sollten keine Zugriffe auf die Uhr per Programm stattfinden, da Pin 7 auch der Interruptausgang der Uhr ist und unter Umständen dann kein 1Hz-Signal liefert.

Die Uhr und das interne RAM sind ab 1 V betriebsbereit und stellen geringe Ansprüche an die Batteriepufferung.

## **EEPROM** (optional):

Es können Bausteine ST24C02, ST24C04, ST24C08 und gleichwertige anderer Hersteller (Xicor) von 256 bis 1024 Byte verwendet werden, die über den IIC-Bus ansprechbar sind. Die Basisadresse auf dem IIC-Bus ist 0xA8. Die Bausteine stellen je nach Größe eine oder mehrere Speicherseiten ab dieser Basisadresse zur Verfügung. Beim sequenziellen Lesen wird der interne Adresszähler automatisch auf die nächste Seite gestellt. Beim Schreiben muß die IIC-Bus-Adresse der jeweiligen Speicherseite angepaßt werden. Ferner erlauben die meisten Bausteine ein sogenanntes 'page-write', beim dem bis zu 16 Byte in einer Programmierperiode (ca. 5ms) geschrieben werden können. Eine entsprechnende Treibersoftware kann diese Optimierungen für den Anwender tranparent halten.

# ser. Schnittstelle, MAX232 (optional):

Normalerweise ist kein Schnittstellentreiber für V.24-Pegel bestückt. Die Signale TxD und RxD werden durch Leiterbahnen auf der Lötseite (unter der Fassung U19) überbrückt, sodaß die Signale des MC68HC901 direkt auf die Steckerleiste herausgeführt sind.

Mit dem Schnittstellentreiber MAX232 (oder ähnliche Typen) werden die Signale TxD und RxD vom 68HC901 auf V.24-Pegel angepaßt.

Der Takt für die ser. Schnittstelle wird normalerweise von Timer D über JMP5 an RxC/TxC geführt. An RxC/TxC kann auch ein externer Takt (TTL/CMOS) gelegt werden; JMP5 ist dann zu entfernen.

#### Pufferbatterie:

Der Baustein PCF8583 (optional) und die RAM-Typen 6264 und 628128 können mit Batteriepufferung versehen werden.

Hier wird normalerweise eine Lithiumzelle CR2330 mit 250mAh verwendet (geringe Bauhöhe). Die CR2330 bietet einen Datenerhalt von typ. 10 Jahren (bei 2 x RAM 6264 und max. 2 µA Leckstrom); da die Leckströme von RAMs bei höheren Temperaturen aber stark zunehmen, kann diese Zeit unter anderen Bedingungen auch geringer ausfallen.

#### ext. 65xx-Bus:

Zum Anschluß externer Bausteine der Serien R65xx oder MC68xx stehen an der VG-Leiste die Signale A0-A7, D0-D7, Phi2, R/W, /INT2, /RESET und zwei Ausgänge /CS0 und /CS1 zur Verfügung. Die Signale stehen synchron zu Phi2 an und sind gegenüber den CPU-Signalen gepuffert. Normalerweise wird mit JMP2 der Takt auf 2MHz eingestellt; es können jedoch auch 1MHz gewählt werden oder ein externes Signal an Phi2 angelegt werden, wobei dann JMP2 offen bleibt.

# Interrupts:

Mit dem GAL 'IAK68001' werden die Interrupts wie folgt dekodiert:

/INT2 Autoint2 für 65C22 und externe Bausteine /INT5 Vektor-Interrupt für 68901 /INT7 Autoint7 für externe Bausteine, NMI

#### I/O-Adressen:

| /CS_65C22 | 0xFFFFFF00 byteweise ansprechbar |

|-----------|----------------------------------|

| /CS0      | 0xFFFFFC00 byteweise ansprechbar |

| /CS1      | 0xFFFFFE00 byteweise ansprechbar |

|           |                                  |

IIC\_SCL 0xFFFFD00 bit 0 (optional)

IIC SDA 0xFFFFD01 bit 0 (optional)

/CS 68HC901 0xFFFFC000 byte-Zugriff im word-Abstand

### Jumper:

Die Jumper auf der 68k1.2-Karte dienen zum einen der Konfiguration der Fassungen für RAM und EPROM, sowie einigen Grundeinstellungen:

JMP1 Anwahl der CPU-Frequenz auf '8' oder '16' MHz JMP2 Anwahl der 65xx-Taktfrequenz 1 oder 2 MHz, oder extern JMP3 IIC-SDA Signal an VG-Leiste für ext. Verwendung (optional) JMP4 IIC-SCL Signal an VG-Leiste für ext. Verwendung (optional) JMP5 ser. Takt von MFP Timer D oder externes Signal JMP7, JMP8, JMP9, JMP10 Einstellung für RAM/EPROM, Beiblatt

**64-pol. VG-Leiste**:

An der VG-Leiste sind sämtliche I/O-Signale von VIA und MFP, sowie zusätzliche Adress-, Daten- und Steuerleitungen herausgeführt:

| Reihe a             | Pin-Nr. | Reihe c                     |

|---------------------|---------|-----------------------------|

| Vcc +5V             | 1       | CB2-6522                    |

| /INT2-Eingang       | 2       | CB1-6522                    |

| R/W-gepuffert       | 3       | PB7-6522                    |

| Phi2                | 4       | PB6-6522                    |

| D7                  | 5       | PB5-6522                    |

| D6                  | 6       | PB4-6522                    |

| D5                  | 7       | PB3-6522                    |

| D4                  | 8       | PB2-6522                    |

| D3                  | 9       | PB1-6522                    |

| D2                  | 10      | PB0-6522                    |

| D1                  | 11      | PA7-6522                    |

| D0                  | 12      | PA6-6522                    |

| /RESET-Ausg.        | 13      | PA5-6522                    |

| A3                  | 14      | PA4-6522                    |

| A2                  | 15      | PA3-6522                    |

| A1                  | 16      | PA2-6522                    |

| A0                  | 17      | PA1-6522                    |

| A4                  | 18      | PA0-6522                    |

| A5                  | 19      | CA2-6522                    |

| A6                  | 20      | CA1-6522                    |

| A7                  | 21      | /INT7                       |

| /CS1                | 22      | frei (IIC-SDA ext.)         |

| /CS0                | 23      | frei (IIC-SCL ext.)         |

| 17-68901            | 24      | /RESET-Eing.                |

| 15-68901            | 25      | I6-68901                    |

| I3-68901            | 26      | I4-68901                    |

| RxD-68901 (MAX232 o | . ,     | TxD-68901 (MAX232 optional) |

| Timer B out-68901   | 28      | Timer A out-68901           |

| RxC/TxC-68901       | 29      | Timer C out-68901           |

| I1-68901            | 30      | 10-68901                    |

| Timer B in-68901    | 31      | 12-68901                    |

| GND, 0 Volt         | 32      | Timer A in-68901            |

# **50-pol. Steckverbinder** (Wanne):

Mit einem 50-Poligen Steckverbinder lassen sich Signale an eine huckepack montierte Platine weiterleiten. Hier können weitere Bausteine wie I/O oder AD/DA-interfaces untergebracht werden. Für diese Zusatplatine sind Befestigungsbohrungen vorhanden.

| Pin 1            | Vcc +5 Volt  | CB2-6522                    |

|------------------|--------------|-----------------------------|

| Pin 3<br>Pin 4   |              | CB1-6522                    |

| Pin 5            | R/W-gepuffer | PB7-6522                    |

| Pin 7            |              | PB6-6522                    |

| Pin 8<br>Pin 9   |              | PB5-6522                    |

| Pin 10<br>Pin 11 |              | PB4-6522                    |

| Pin 12<br>Pin 13 |              | PB3-6522                    |

| Pin 14<br>Pin 15 |              | PB2-6522                    |

| Pin 16<br>Pin 17 |              | PB1-6522                    |

| Pin 18<br>Pin 19 |              | PB0-6522                    |

| Pin 20<br>Pin 21 |              | PA7-6522                    |

| Pin 22<br>Pin 23 |              | PA6-6522                    |

| Pin 24<br>Pin 25 |              | PA5-6522                    |

| Pin 27           |              | J.<br>PA4-6522              |

| Pin 28<br>Pin 29 |              | PA3-6522                    |

| Pin 30<br>Pin 31 |              | PA2-6522                    |

| Pin 32<br>Pin 33 |              | PA1-6522                    |

| Pin 34<br>Pin 35 |              | PA0-6522                    |

| Pin 36<br>Pin 37 |              | CA2-6522                    |

| Pin 38<br>Pin 39 |              | CA1-6522                    |

| Pin 30<br>Pin 41 | A6           | /INT7                       |

| Pin 42<br>Pin 43 |              | frei (IIC-SDA opt.)         |

| Pin 44<br>Pin 45 | /CS1-Ausg.   | frei (IIC-SCL opt.)         |

| Pin 46<br>Pin 47 | /CS0-Ausg.   | Timer D out-68901 (RxC/TxC) |

| Pin 48<br>Pin 49 | 15-68901     | GND, 0 Volt                 |

|                  | 17-68901     | ,                           |

#### Technische Daten:

Supply Voltage Vcc 5 Volt +/- 5%

Supply Current Icc 180 mA typ. (220 mA max.)

Input Low Voltage IoL 0,4 V typ. (-0,3 V min., 0,8 V max.)

Input High Voltage IoH 2,4 V typ. (2 V min., Vcc+0,3 V max.)

Input Low Current IIL

D0-D7, I0 - I7, RxD, CA1, CA2, CB1, CB2, PB0 - PB7, PA0 - PA7,

RxC/TxC, TB-in, TA-in +/- 10  $\mu$ A max.

/INT2, /INT7, /RES 1,6 mA

Input High Current IHL

D0-D7, I0 - I7, RxD, CA1, CA2, CB1, CB2, PB0 - PB7, PA0 - PA7, RxC/TxC, TB-in, TA-in

RxC/TxC, TB-in, TA-in +/- 10  $\mu$ A max.

/INT2, /INT7, /RES 0,8 mA @2,4 V, 0 mA @Vcc

Output Low Current OIL

D0 - D7, A0 - A7, /RES,Phi2 4 mA

PA0 - PA7, PB0 - PB7,

CA2, CB1, CB2, 3,2 mA /CS1, /CS2, R/W 10 mA 10 - I7, TA-out - TD-out, TxD 1,6 mA

Output High Current OIH

D0 - D7, A0 - A7, Phi2 -4 mA

PA0 - PA7, PB0 - PB7,

CA2, CB1, CB2, -0,2 mA /CS1, /CS2, R/W -10 mA 10 - 17, TA-out - TD-out, TxD -0,4 mA

CPU - Clock Fclk 8 MHz typ. (16 MHz max.)

I/O - Clk Fphi2 2 MHz typ.

Lithium Batterie PANASONIC CR2330 P, 250 mAh

Batterie Endurance typ. 5 Years @20°C

Ambient Temperature operating 0 to 75°C

storage -40 to 95°C

Dimension LxWxT 167 x 100 x 15 mm<sup>3</sup>

A13 A18 A18 A13 A18 A13 A15 <sub>8</sub> 28 31 28 A15 מ 31 Batt 32 +5 E27256 Ψ E274001 528128 CS2 Batt 32 32 CS2 <del>수</del> CS2 <del>ا</del> <del>ا</del> ო 30 A14 Batt A14 30 A14 +5 30 A17 /WR A17 /WR A13 A13 A18 A18 A13 A18 A15 A15 **1**82 <sub>28</sub> A15 78 31 31 31 E272001 E27128 62256 Jumper für RAM / EPROM CS2 32 32 CS2 Batt 32 CS2 <del>ا</del> <del>+</del> ო Batt Batt A14 30 A14 30 30 A14 + /WR A17 A17 A17 /WR 29 뜻 A13 A13 A13 A18 A18 A18 A15 A15 28 A15 28 6264\_BAT 31 Batt 32 +5 31 +2 31 + 5 E271001 E2764 المًا CS2 32 CS2 CS2 Batt 32 <del>+</del> <del>수</del> ო Batt 30 30 A14 A14 A14 <del>ا</del> A17 A17 /WR A17 /WR /WR 29 8 A13 A18 A13 A18 A13 A18 28 28 A15 A15 Ŋ 528128\_B 31 31 31 Œ E27512 30 CS2 CS2 Batt 32 Batt 32 CS2 32 6264 +5 + 2 <del>+</del> l<sub>ო</sub> ო ო Batt 30 H14 A14 A14 30 <del>+</del>2 A17 A17 MR A17 ÀК