## M50530-XXXFP

24. Mei 1991

### DOT MATRIX LIQUID CRYSTAL DISPLAY CONTROLLER-DRIVER

### **DESCRIPTION**

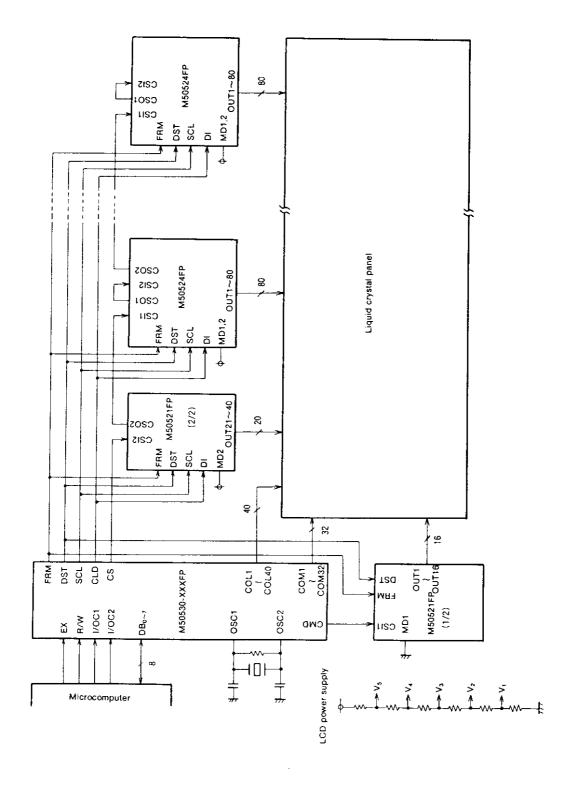

The M50530-XXXFP is an LSI for a dot matrix liquid crystal display control drive which has been developed by making use of the silicon gate CMOS process, and can control multi-digit data and directly drive a dot matrix liquid crystal display of 256 font types including alphanumerics, kana characters and symbols by a simple control from  $\mu c$  and  $\mu$  b.

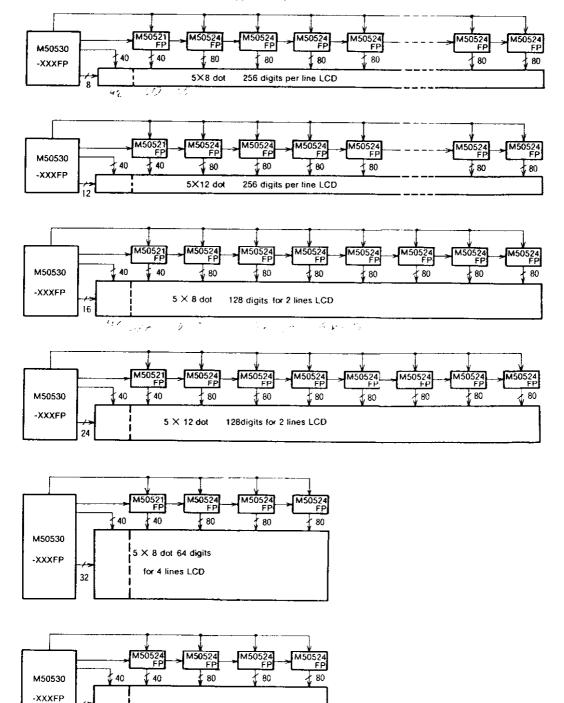

The M50530-XXXFP offers a system for controlling and driving a dot matrix liquid crystal display, and also expands the number of display digits by the simultaneous use of the IC for the liquid crtstal drive, M50521FP or M50524FP.

By using the M50530-XXXFP it has been possible to create a liquid crystal display system which is compact, has low power consumption and is very versatile.

### **FEATURES**

- Interfacing (It is possible to interface directly with a 4bit μc and an 8-bit μc. It is possible to interface directly with 8085 μp.)

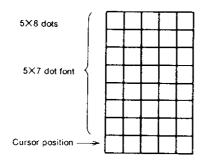

- Characters (256 font types with 5×8 dots or 5×12 dots (cursor is common to both))

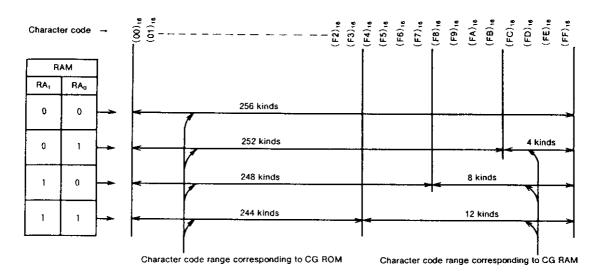

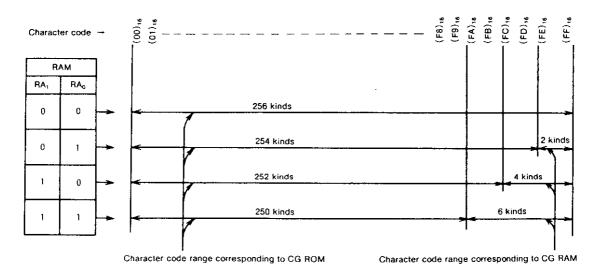

- Memory (Generally for a display data RAM and for a character generation RAM, it is possible to use

a total of 256 words, with 9 bits to a word, and to select one configuration out of the 4 types described below that offer maximum and minimum configurations.)

- Display Data RAM (hereafter referred to as DD RAM)

9 bits to a word (of these, 1 bit is used to underline)

- ····· 4 types from a maximum of 256 words to a minimum of 160 words

- Character generator RAM (hereafter referred to as CG RAM)

- 5×7 dots······4 types from a minimum of 0 to a maximum of 12 characters

- or 5 × 11 dots ······ 4 types from a minimum of 0 to a maximum of 6 characters

- Character generator ROM (hereafter referred to as CG ROM)

- 5×7 dots······4 types from a maximum of 256 to a minimum of 244 characters

- or 5×11 dots······4 types from a maximum of 256 to a minimum of 250 characters

- Instructions (The following comprehensive instructions are given.)

- Cursor address set-up for DD/CG RAM

- · Display start address set-up

- · Data write and read from RAM

- · Display shift and cursor shift

- Interface changeover between 8-bit μc/4-bit μc

- Font changeover between 5×8 dots /5×12 dots

- Duty changeover between (1/8, 1/12), (1/16, 1/24),

and (1/32, 1/48)

- Selection between DD/CG RAM configurations

- · Underline set-up for each character

- Display ON/OFF, cursor display ON/OFF, underline display ON/OFF, character blink, and cursor blink

- · Blink frequency set-up

- Display address home and cursor address home

- · Clearing entire display

- Display difgit No. :

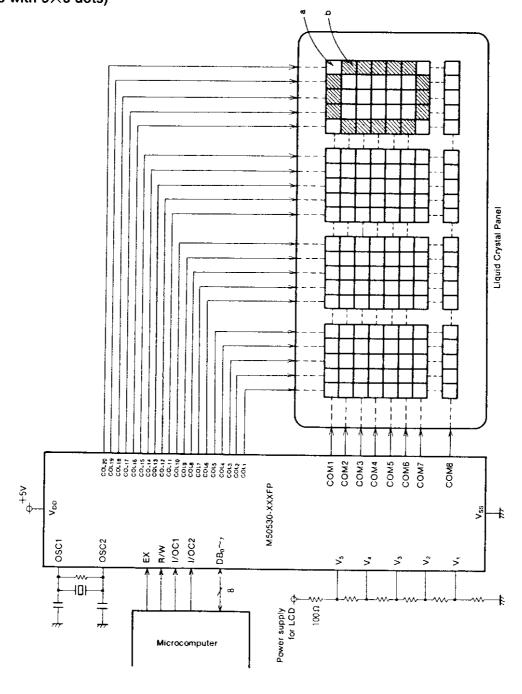

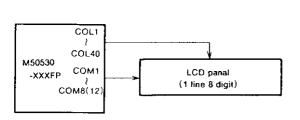

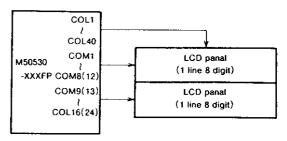

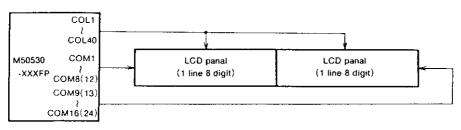

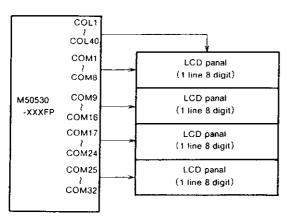

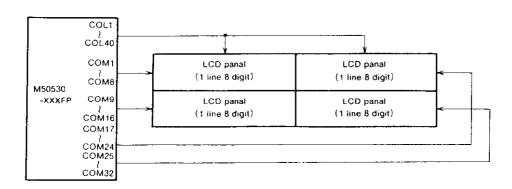

- 1 chip system (8 digits for 1 line, 8 digits for 2 lines, and 8 digits for 4 lines)

- Maximum system configuration (The 4 following types of maximum system configuration are available for 1 line, 2 line, and 4 lines respectively.)

- 1 line 256 digits, 244 digits, 192 digits, and 160 digits 2 lines ·· 128 digits, 112 digits, 96 digits, and 80 digits

- 4 line ..... 64 digits, 56 digits, 48 digits, and 40 digits

- · Internally provided for liquid crystal display drive circuit

- Common signal: 32 lines (corresponds to 4-line portion for 1/32 duty)

- Column signal : 40 lines (corresponds to 8-digit portion for 5 lines per digit)

- By using the IC for the liquid crystal drive M50521FP or M50524FP, it is possible to expand the display to the maximum number of digits.

- Automatic reset at power cut-off

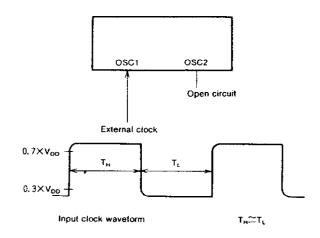

- Built-in oscillator (An external resistor or an external ceramic filter)

- Oscillation frequency 2.58MHz (for a frame frequency of about 70Hz)

- Column data transfer speed (1.29Mbit/set (for oscillation frequency of 2.58MHz))

- Blink frequency (About 0.5Hz, 1Hz, 2Hz, and 4Hz (for oscillation frequency of 2.58 MHz))

- Supply voltage for logic circuit : (+4.5~5.5 V)

- Output voltage of liquid crystal drive : (+3~14 V)

- On-resistance of liquid crystal drive:

$500\Omega(14V)$  and  $2k\Omega(5V)$ , maximum

- Low power consumption: Siticon gate CMOS process

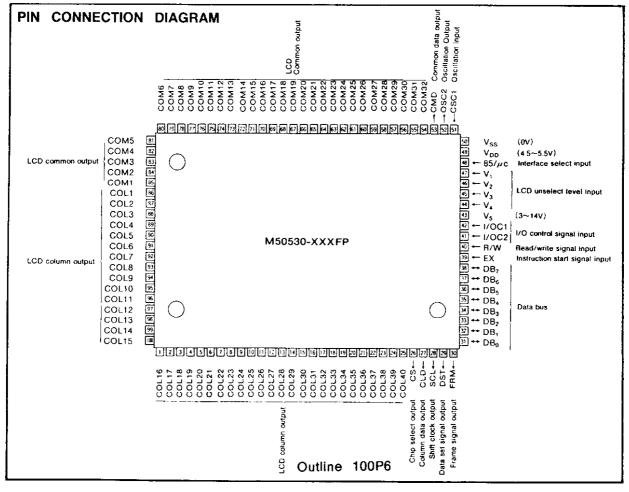

- Package: 100-pin plastic flat QUIP, lead pitch 0.65mm

### **APPLICATION**

OA apparatus (portable personal computer, electical type-writer e.t.c), Information apparatus (Telephone, Fax e.t.c).

### **FUNCTIONAL DESCRIPTION**

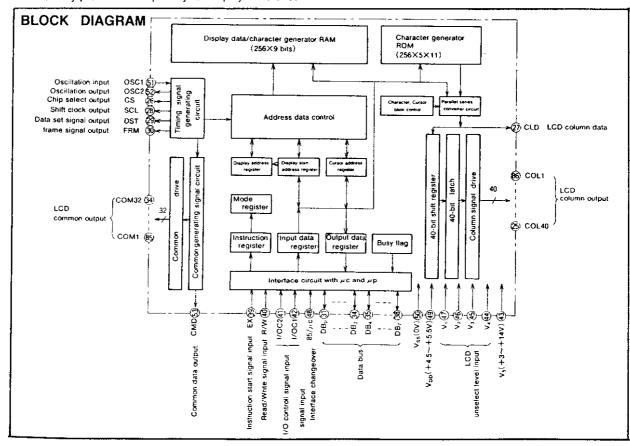

The LSI M50530-XXXFP is controlled by instructions from a  $\mu c$  or  $\mu p$  on the outside. In other words, the  $\mu c$  or  $\mu p$  takes the role of master processor and M50530-XXXFP takes the role of slave processor. M50530-XXXFP can control completely the liquid crystal display (LCD).

When transferring data between the  $\mu c$  or  $\mu p$  and the internal RAM within the M50530-XXXFP first the RAM address is set by an instruction in the cursor address register, then, either external data is written by an instruction in the internal RAM via the internal input data register or data is read by an instruction from the RAM to the outside via the output data register.

M50530-XXXFP has various execution condition modes for instructions such as function construction, display, reading, writing etc. In this way, the efficiency of execution of the instruction has been improved. These different modes are stored by the mode setting instructions in the mode register, and they are used in subsequent instructions as execution conditions.

When RAM data is displayed by LCD, the address of the RAM data to be displayed as the first digit on the left-hand side of the LCD is set with the display start address. First, set by instruction the first digit in the display start address register to the RAM address desired for display. Data is displayed by LCD from this address to successively higher digits.

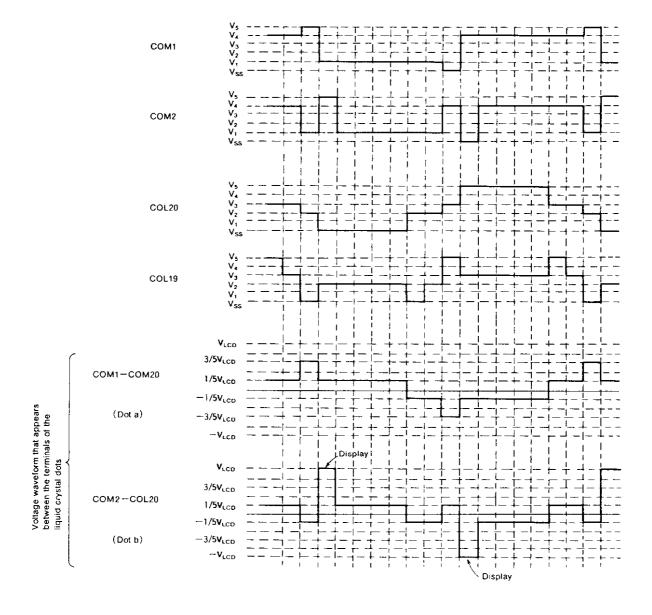

As regards the LCD drive, a common signal is generated in the timing generation circuit on the scanning side to drive the common side of the LCD via the common signal drive.

The RAM data for display, designated by the address in the display address register is read on the column data side as a character code. The data is then converted to a character pattern in the character generator of the ROM or RAM.

Then, by sending the 5-bit data in the line, which corresponds to the common scanning signal in the line matrix of the character pattern, to the shift register as a column signal, the column side of the LCD is driven via the column singal drive.

In order to display all of the display data by LCD: 1) the display address register is incremented for each of the common signals; 2) display data is read successively from the RAM; 3) column signals for all lilnes of the display are sent, by repeated conversion and transfer, to the column drive; and 4) the column side is driven.

The LCD operation is independent of the execution of an instruction from the outside and is processed within a prescribed time, so that no flickering will be generated in the display regardless of the presence of instructions being executed.

One chip of the M50530-XXXFP can directly drive an 8-digit LCD for 1 line, 2 lines, and 4 lines. However, if a LCD with more digits is desired, it is necessary to connect an external IC for the LCD drive; either M50521FP or M50524FP. These ICs for LCD drive can drive a LCD as a common signal drive or column signal drive. Furthermore, when a large number of these ICs are used, the system is designed such that the data signals can be received only by the IC that is supplied with the chip select signal. This design allows the system can be operated with low power consumption.

The LCD contents are present for a prescribed frame time which is determined by the oscillation frequency, and the time is constant independent of the line number of the display, duty ratio, digit number of the display, and character font.

## TERMINAL DESCRIPTION

| Pin                            | Name                           | 1/0 | Function                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|--------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 85/μc                          | Interface changeover signal    | 1   | This is used as a signal for changing over the interface between $\mu c$ and $\mu p$ . It should be set to "1" for 8085 $\mu p$ and to "0" for $\mu c$ mode.                                                                                                                                                                                                                                                                            |

| 1/001                          | Input/output<br>control signal | 1   | In the $\mu c$ mode, this is used as the control signal for sending an instruction from the $\mu c$ to the M50536 XXXFP, and is used as part of the instruction code. In the 8085 $\mu p$ mode, it is connected to the $\overline{WR}$ signal the 8085 $\mu p$ .                                                                                                                                                                        |

| I/OC2                          | Input/output<br>control signal | 1   | In the $\mu c$ mode, this is used as the control signal for sending an instruction from the $\mu c$ to the M50536 XXXFP, and is used as part of the instruction code. In the 8085 $\mu p$ mode, it is connected to the IO/M sign of the 8085 $\mu p$ .                                                                                                                                                                                  |

| R/W                            | Write/read signal              | l   | In the $\mu c$ mode, this is used as the control signal for sending an instruction from the $\mu c$ to the M50536 XXXFP, and is used as part of the instruction code. It is set to "0" for write instruction and to "1" for read in struction. In the 8085 $\mu$ p mode, it is connected to the RD signal of the 8085 $\mu$ p.                                                                                                          |

| EX                             | Instruction start signal       | 1   | In the $\mu c$ mode, this is used as the signal for the $\mu c$ to cause the M50530-XXXFP to start the execution an instruction. In the 8085 $\mu p$ mode, it is connected to the ALE signal of the 8085 $\mu p$ .                                                                                                                                                                                                                      |

| DB <sub>7</sub> ~<br>DB₄       | Data bus                       | 1/0 | These represent the 4 upper lines of the 8 line data buses. They are in tri-state bidirectional mode whice enables inputting as well as outputting. These are used for instruction data transfer between the M50530 XXXFP and the $\mu c$ or $\mu p$ . When interfacing with the $\mu c$ is 4 bits, the lower 4 bits data are also transferre by these 4 lines of data buses. The DB <sub>7</sub> is also used for reading a busy flag. |

| DB₃∼<br>DB₀                    | Data bus                       | 1/0 | These are the 4 lower lines of the 8 line data buses. They are in tri-state bidirectional mode which enable inputting as well as outputting. These are used for instruction data transfer between the M50530-XXXF and the $\mu c$ or $\mu p$ . When interfacing with the $\mu c$ is 4 bits, these 4 lines are not used.                                                                                                                 |

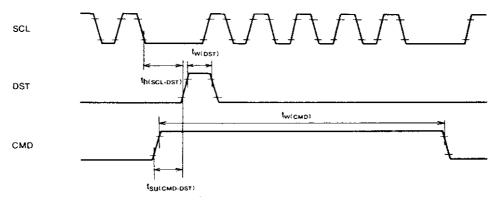

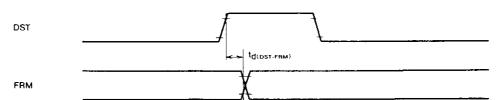

| DST                            | Data set signal                | 0   | Signal for setting serial data sent to the drive IC to a latch.                                                                                                                                                                                                                                                                                                                                                                         |

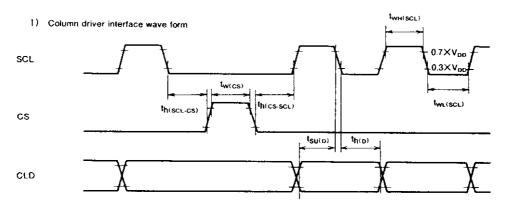

| SCL                            | Shift clock signal             | 0   | Clock for successively shifting a serial data set sent to drive IC.                                                                                                                                                                                                                                                                                                                                                                     |

| FRM                            | Frame signal                   | 0   | Display frame signal. Used as a changeover signal for driving the liquid crystal by AC power.                                                                                                                                                                                                                                                                                                                                           |

| cs                             | Chip select signal             | 0   | Signal for selecting the column drive IC. Data will be transferred only to the drive IC to which this signal supplied.                                                                                                                                                                                                                                                                                                                  |

| CMD                            | Common data signal             | 0   | Common data signal to be sent to the common drive tC. Connected to chip select of the drive IC.                                                                                                                                                                                                                                                                                                                                         |

| CLD                            | Column data signal             | 0   | Column data signal to be sent to column drive IC.  Sends a character pattern serially. Value "0" corresponds to non-selection while "1" corresponds to selection.                                                                                                                                                                                                                                                                       |

| COM1~<br>COM32                 | LCD Common signat              | 0   | Common signal for driving the scanning side of the liquid crystal. Common signals that are not used are a given the non-select waveform. For instance, if the duty is 1/16, then COM17 to COM32 will always begiven non-select waveforms.                                                                                                                                                                                               |

| COL1~<br>COL40                 | LCD Column signal              | 0   | Column signal for driving the data side of the liquid crystal. Drives the respective 8-digit portion of the RAN display data of the display start address for each line.                                                                                                                                                                                                                                                                |

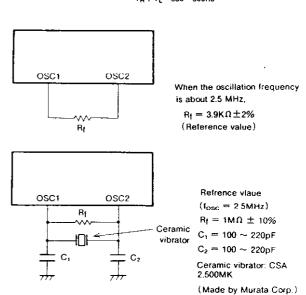

| OSC1,<br>OSC2                  | Oscillation input/output       | 1/0 | Terminal for oscillating internal clock. Connected to a resistor or a ceramic filter. Clock input from outside is supplied to OSC1.                                                                                                                                                                                                                                                                                                     |

| V <sub>1</sub> ~V <sub>5</sub> | Power supply(LCD)              | ŀ   | Power supply for driving liquid crystal display. Voltages $V_{SS}$ , $V_1$ , $V_4$ , and $V_5$ are common while $V_{SS}$ , $V_2$ , $V_3$ and $V_5$ are for column.                                                                                                                                                                                                                                                                      |

| V <sub>DD</sub>                | Power supply(Logic)            | ı   | Power supply for the logic circuit, +5V                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>ss</sub>                | Power supply(GND)              | ı   | Ground power supply, 0V                                                                                                                                                                                                                                                                                                                                                                                                                 |

# FUNCTIONAL EXPLANATION OF EACH BLOCK

In the description below, the following abbreviations will be used:

Display data RAM: DD RAM

Character generator RAM : CG RAM Character generator ROM : CG ROM

Display data/character generator RAM: DD/CG RAM

In abbition, the designations of instructions will follow the abbreviations given in the instruction list. Use will also be made of the instruction code names in the instruction list.

The relationship between the binary logic values and the voltage levels is as given below.

Binary number 0: Low voltage level Binary number 1: High voltage level

Furthermore, the following notations will be employed.

( ) n means that the numerical value within the parentheses is that of the n-ary notation, namely, the number system in which n is used as the radix.

R( )n means the content of the RAM address ( )n. It should be noted that unless otherwise stated, numerical values without suffix are meant for decimal notation. For instance.

$(8F)_{16} \equiv (10001111)_2 \equiv (143)_{10} \equiv 143$ , and  $R(8F)_{16} \equiv R(10001111)_2 \equiv R(143)$  means the content of the address 143 to the RAM.

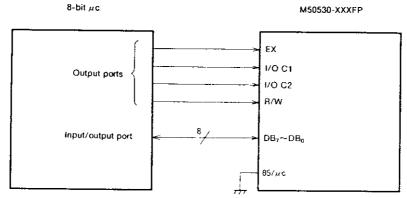

# 1 INTERFACE CIRCUITS FOR $\mu$ c AND $\mu$ D

These are the circuits for controlling input and output when instructions and data are transferred between the M50530-XXXFP and external  $\mu c$  or  $\mu p$  that control the M50530-XXXFP.

By means of the input signal  $85/\mu c$ , it is possible to select either  $8085~\mu p$  or  $\mu c$  as an external control.

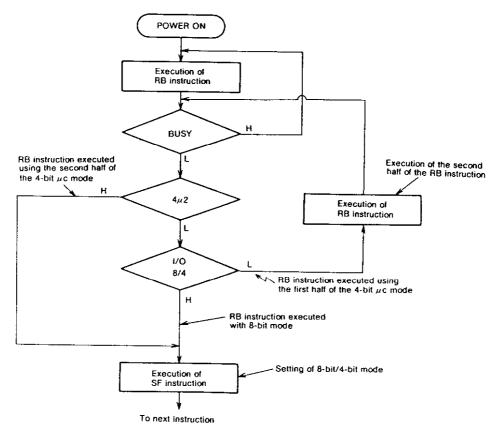

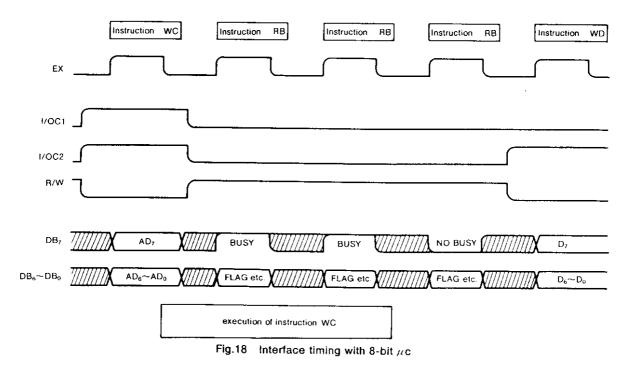

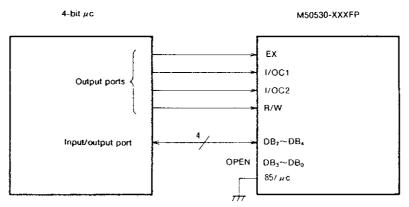

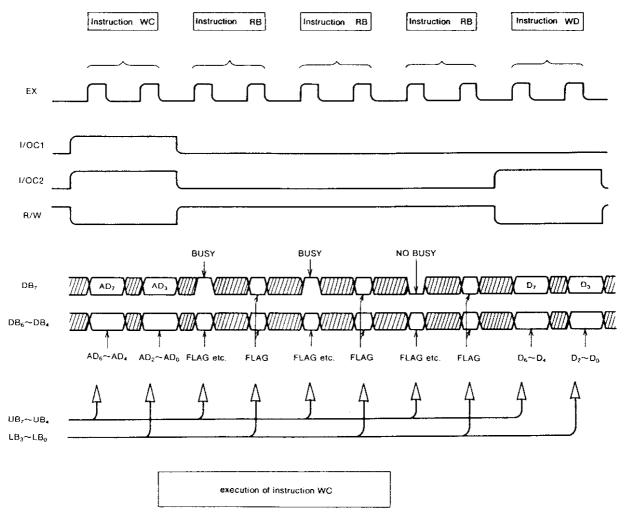

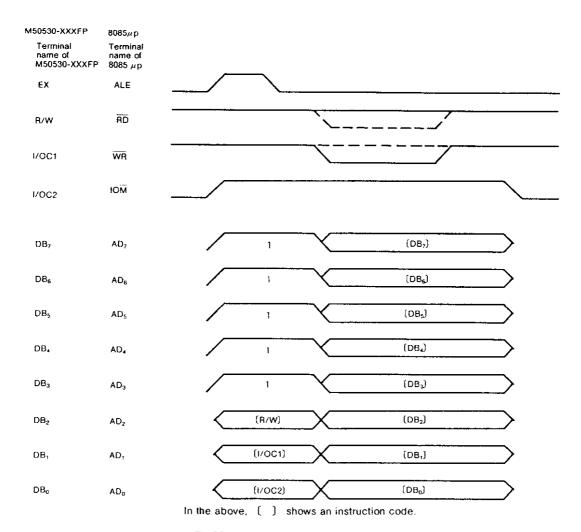

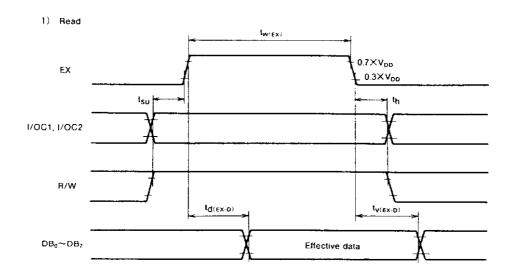

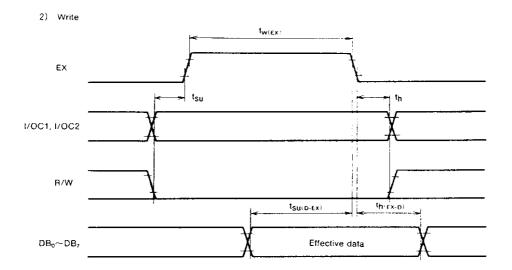

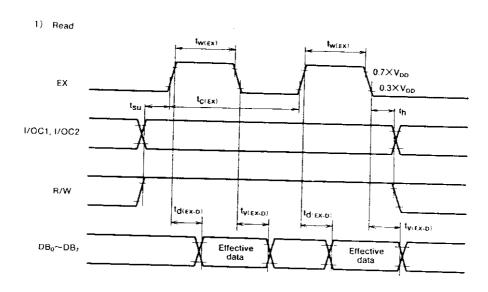

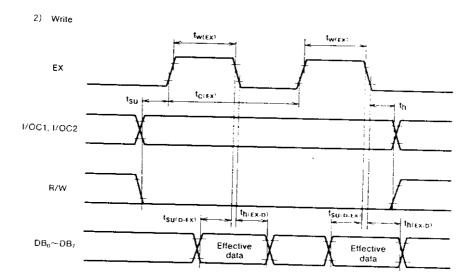

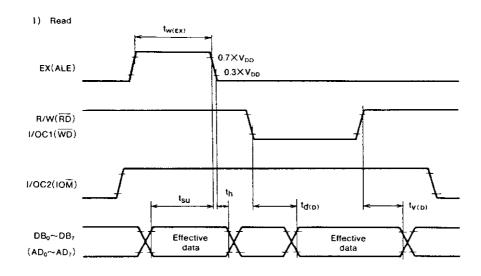

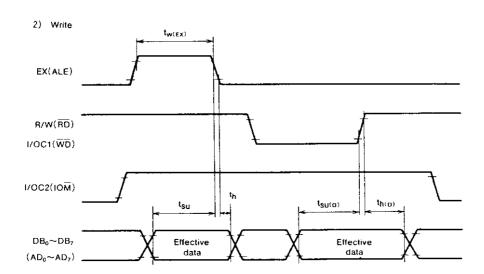

When  $\mu c$  is selected, it is further possible to select 8-bit  $\mu$ c or 4-bit  $\mu c$  by the instruction SF. For the transfer of an instruction code from the 8-bit  $\mu c$  to the M50530-XXXFP, the input signals I/OC1, I/OC2, R/W, and the input/output signals DB<sub>7</sub> to DB<sub>0</sub>, are used and the input signal EX are used for starting the execution of the instruction. For the transfer of an isntruction code from the 4-bit  $\mu c$  to the M50530-XXXFP, the input signals I/OC1, I/OC2, R/W, and the input/output signals DB<sub>7</sub> to DB<sub>4</sub>, are used twice. The input signal EX are also used twice for starting the execution of the instruction. In other words, in the 8-bit  $\mu c$ , the data buses DB<sub>7</sub> to DB<sub>0</sub> with 8 bits are used, and in the case of the 4-bit  $\mu c$ , the data buses DB<sub>7</sub> to DB<sub>4</sub> with 4 bits are used.

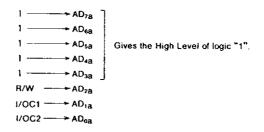

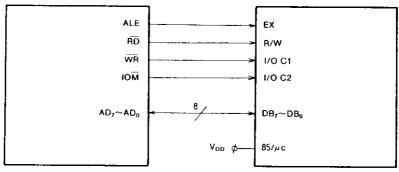

When the 8085  $\mu p$  is selected, by connecting the signals AD<sub>7</sub> to AD<sub>0</sub>, ALE, RD, WR, and IO/M of the 8085  $\mu p$  to the signals DB<sub>7</sub> to DB<sub>0</sub>. EX, R/W, I/OC1 and I/OC2, respectively, of the M50530-XXXFP, it is possible to control directly the M50530-XXXFP by producing an instruction code for M50530-XXXFP using the input/output instructions for 8085  $\mu p$ .

The external  $\mu c$  and  $\mu p$  and the M50530-XXXFP operate asynchronously. Accordingly, there is no need for the inputs from the  $\mu c$  and  $\mu p$  to be synchronous with the internal clock of M50530-XXXFP. Furthermore, the handling of the interface for the signals from the external  $\mu c$  and  $\mu p$ , or the execution of the instructions from the  $\mu c$  and  $\mu p$ , will in no way affect the LCD processing within M50530-XXXFP. Therefore, no flickering will be generated in the display due to inputs from the  $\mu c$  and  $\mu p$ .

### 2 BUSY FLAG

When the M50530-XXXFP is executing an instruction, the busy flag will show  $(1)_2$ .

When the busy flag is at  $(1)_2$ , no instruction from the  $\mu p$  or  $\mu c$  will be accepted. Therefore, it is necessary to give an instruction to M50530-XXXFP after confirming that the busy flag is  $(0)_2$ .

However, the busy flag read instruction alone, RB, can always be used even when another instruction is being executed, and by using the instruction RB, the condition of the busy flag can be read from  $DB_7$  and  $DB_3$ .

# 3 INSTRUCTION REGISTER AND MODE REGISTER

An instruction from the  $\mu p$  or  $\mu c$  enters the instruction register via the  $\mu c$  and  $\mu p$  interface circuits. The instruction is executed when its content has been decoded.

Among the included instructions are those which can set up the following modes.

Instruction SF : 8-bit/4-bit interface

$5 \times 8$  dots /  $5 \times 12$  dots font display line number, RAM region

Instruction SE : Cursor shift mode, display shift mode

Instruction SD: Display mode, blink mode Instruction SU: Underline write mode

Instruction SB : Blink frequency

The mode register stores the information of these modes. These modes are used as conditions for execution of the instructions.

# 4 INPUT REGISTER AND OUTPUT REGISTER

The input data is entered into the input data register by the write instructions WC, WS, WD, and WU, and is transferred to the interior upon execution of the instruction.

Output data is outputted from the output data register to the  $\mu p$  or  $\mu c$  by the read instructions RC, RS, and RD. The output data for these instructions is prepared beforehand in the output data register.

### 5 CURSOR ADDRESS REGISTER

This is the register for specifying the DD/CG RAM address. In order to write data into the RAM using the instruction WD, or read data from the RAM using the instruction RD, or

add an underline to the RAM using instruction WU, it is necessary to set, beforehand, the address of the RAM in the cursor address register. With the instruction WC it is possible to set data in the cursor address register. Also the content of the cursor address register can be read using the isntruction RC.

By incrementing  $(\pm 1)$  or by decrementing  $(\pm 1)$  the content of the cursor address register using the instruction MA, it is possible to shift the cursor address to the RAM in the upward or the downward direction.

After writing or reading the data using the instructions WD or RD and the entry mode has been specified by the instruction SE, the content of the cursor address register can be automatically incremented (+1) or decremented (-1) as shown in table 1.

Table 1. Instruction SE and cursor address

|         | tion SE<br>NDITION | Automatic INC/DEC of the Cursor Address             |  |

|---------|--------------------|-----------------------------------------------------|--|

| (w) (R) |                    |                                                     |  |

| 0 0     |                    | No automatic inc or dec                             |  |

| 0 1     |                    | Inc or dec after execution of instruction RD        |  |

| 1 0     |                    | Inc or dec after execution of instruction WD        |  |

| 1       | 1                  | Inc or dec after execution of instruction RD and WD |  |

The increment and decrement of the cursor address register are executed within the display data region and the character generator region, respectively, of the RAM.

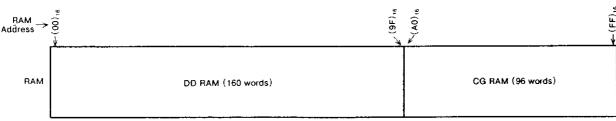

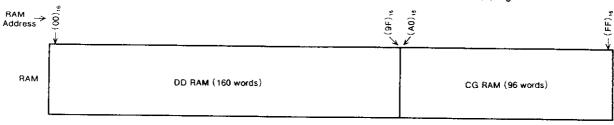

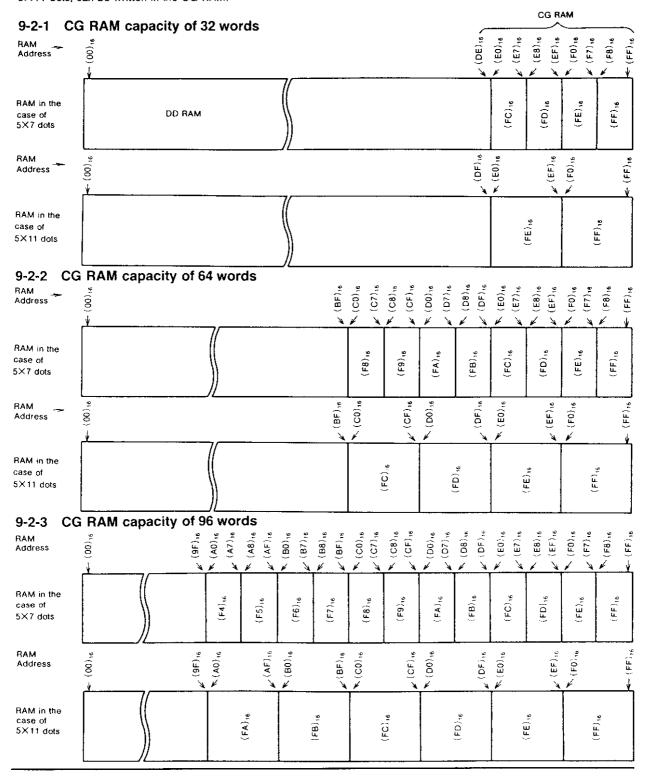

The Fig. 1 is an example (of 4 kinds of configurations) in which the RAM is divided into the display data region and

Fig.1 Example of dividing RAM

the character generation region. The increment and the decrement of the cursor address is as shown on the boundaries of the respective regions are as shown in table 2.

Table 2. Cursor Address

| RAM    | Cursor Address     |                    |                    |  |  |  |

|--------|--------------------|--------------------|--------------------|--|--|--|

| Region | Before inc/dec     | After inc          | After dec          |  |  |  |

|        | (00)16             | (01)16             | (9F) <sub>16</sub> |  |  |  |

| DD RAM | (9F) <sub>16</sub> | (00)16             | (9E) <sub>16</sub> |  |  |  |

|        | (A0) <sub>16</sub> | (A1) <sub>16</sub> | (FF) <sub>16</sub> |  |  |  |

| CG RAM | (FF) <sub>16</sub> | (AO) <sub>16</sub> | (FE) <sub>16</sub> |  |  |  |

The boundary conditions in the increment and the decrement of the cursor address are displayed in 2 lined and 4 lines so that the conditions will remain the same as in the above table even when the RAM region is further subdivided.

## 6 DISPLAY START ADDRESS REGISTER

This is the register for determining the relative relationship between the position of the displayed character in the LCD and the address of the DD RAM in which the character is written.

The content of the display start address register designates the address of the RAM in which the character code of the character to be displayed in the first digit on the left end of the LCD.

The range of the display start address varies with the size of the RAM region and the number of displayed lines.

In the case of 2-line display, the display start addressed for

the first line and the second line have a common value, and in the case of 4-line display, the display start addresses for the first through fourth lines have a common value. In the case of display of more than 2 lines, the value of the display start address of the first line is used as the value of the display start address. Accordingly, the range of the display start address is given depending upon the size of the RAM region and the number of display lines, as table 3.

Table 3. Range of display start address

| Instruc | ction SF DD RAM Region |                                                     | Range of Display Start Address         |                                        |                                        |  |  |

|---------|------------------------|-----------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|--|--|

| RA:     | RA₀                    | LUU HAM Hegion                                      | 1-line Display                         | 2-line Display                         | 4-line Display                         |  |  |

| 0       | 0                      | 256 words<br>(00) <sub>16</sub> ~(FF) <sub>16</sub> | (00) <sub>16</sub> ~(FF) <sub>16</sub> | (00) <sub>16</sub> ~(7F) <sub>16</sub> | (00) <sub>16</sub> ~(3F) <sub>16</sub> |  |  |

| 0       | 1                      | 224 words<br>(00) <sub>16</sub> ~(DF) <sub>16</sub> | (00) <sub>16</sub> ~(DF) <sub>16</sub> | (00) <sub>16</sub> ~(6F) <sub>16</sub> | (00)16~(37)16                          |  |  |

| 1       | 0                      | 192 words<br>(00) <sub>16</sub> ~(BF) <sub>16</sub> | (00) <sub>16</sub> ~(BF) <sub>16</sub> | (00) <sub>16</sub> ~(5F) <sub>16</sub> | (00) <sub>15</sub> ~(2F) <sub>16</sub> |  |  |

| 1       | 1                      | 160 words<br>(00) <sub>16</sub> ~(9F) <sub>16</sub> | (00) <sub>16</sub> ~(9F) <sub>16</sub> | (00) <sub>16</sub> ~(4F) <sub>16</sub> | (00) <sub>16</sub> ~(27) <sub>16</sub> |  |  |

By setting a display start address in the display start address register with the instruction WS, it is possible to display starting with the first digit of the LCD, from an arbitrary address of the DD RAM.

The content of the display start address register can be read with the instruction RS.

By incrementing (+1) or decrementing (-1) the content of the display start address register with the instruction MA, the position of the liquid crystal display with respect to the

RAM can be shifted upward or downward.

After writing or reading the data with the instruction WD or RD, it is possible to automatically increment  $(\pm 1)$  or decrement  $(\pm 1)$  the content of the display start address register by designating the entry mode with the instruction SE. This is shown in table 4.

Table 4. Instruction SE and display start address

| tristruc | tion SE                                      |                                                         |

|----------|----------------------------------------------|---------------------------------------------------------|

| DSP CO   | CONDITION   Automatic inc/dec of Display Sta |                                                         |

| (w)      | (R)                                          |                                                         |

| 0        | 0                                            | No automatic inc or dec                                 |

| 0        | 1                                            | fnc or dec after execution of the instruction RD        |

| 1        | 0                                            | Inc or dec after execution of the instruction WD        |

| 1        | 1                                            | Inc or declafter execution of the instructions RD and W |

The increment and the decrement of the content of the display start address register are executed within the data region for the first line in the display data region of the RAM. The relation between the RAM address and the content of the display start address register will now be explained, when the RAM is divided into 160 words of DD RAM and 96 words of the CG RAM (one of the 4 possible configurations).

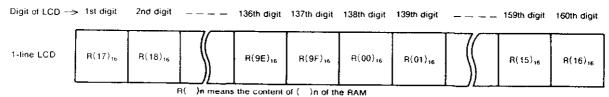

An example of the case of 1-line of LCD (for 160 words of DD RAM and 96 words of CG RAM); Fig. 2.

Fig.2 DD/CG RAM

When the content of the display start address register is (17)<sub>16</sub>, the liquid crystal display will be as Fig. 3.

Fig.3 Example of display address

Here, if the content of the display start address register is incremented  $(\pm 1)$ , the result becomes  $(18)_{16}$ , and the LCD display will be given by Fig. 4.

Fig.4 Example of display address

Visually, the content of the displayed content looks as if it is shifted to the left. Similarly, when the content of the display start address register is decremented, the displayed content looks as if it is shifted to the right. When the display start address is situated on the boundary of the display data region of the RAM, if the display start address is incremented or decremented, the result will be as shown in table 5.

Table 5. Change of display start address

| Display Start Address              |        |                    |  |  |  |  |

|------------------------------------|--------|--------------------|--|--|--|--|

| Before inc/dec After inc After dec |        |                    |  |  |  |  |

| (00)16                             | (01)16 | (9F) <sub>16</sub> |  |  |  |  |

| (9F) <sub>16</sub>                 | (00)16 | (9E)16             |  |  |  |  |

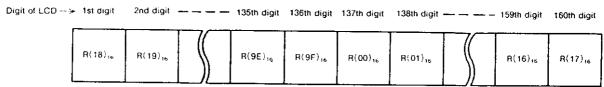

An example of the case of 2-line of LCD (for 160 words of DD RAM and 96 words of CG RAM); Fig. 5.

Fig.5 DD/CG RAM

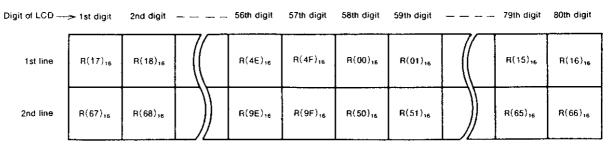

When the content of the display start address register is (17)<sub>16</sub>, the LCD is given by Fig. 6.

Fig.6 Example of display address

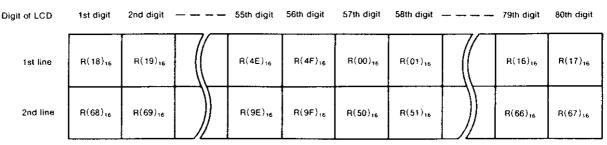

When the content of the display start address register is incremented, the result becomes (18) 16, and the LCD becomes as shown in Fig. 7

Fig.7 Example of display address

The displayed contents of the first and the second lines look visually as if they are simultaneously shifted to the left. Similarly, if the content of the display start address register is decremented, the displayed contents of the first and the second lines look as if they are shifted simultaneously to

the right. When the display start address is situated on the boundary of the display data region of the first line of the RAM, by incrementing or decrementing the display start address the result becomes as shown in table. 6.

Table 6. Change of display start address

| Display Start Address              |                    |                    |  |  |  |  |  |

|------------------------------------|--------------------|--------------------|--|--|--|--|--|

| Before inc/dec After inc After dec |                    |                    |  |  |  |  |  |

| (00)18                             | (01) <sub>16</sub> | (4F) <sub>16</sub> |  |  |  |  |  |

| (4F) <sub>16</sub>                 | (00)16             | (4E) <sub>16</sub> |  |  |  |  |  |

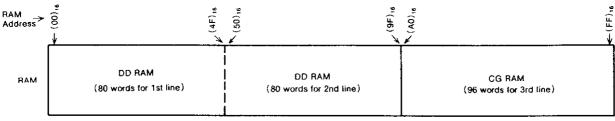

Case of 4-line LCD (for 160 words of DD RAM and 96 words of CG RAM); Fig. 8.

Fig.8 DD/CG RAM

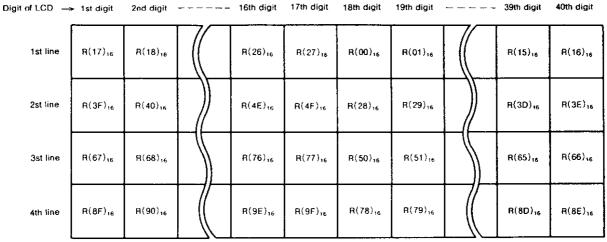

When the content of the display address register is (17)<sub>16</sub>, LCD will be as Fig. 9:

Fig.9 Example of display address

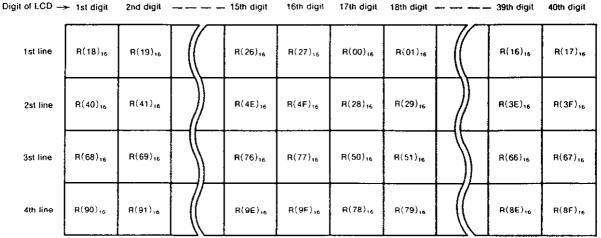

When the content of the display start address register is incremented, the result is  $(18)_{16}$ , and the LCD will be given by Fig. 10

Fig.10 Example of display address

The displayed content of the first, second, third and fourth lines look visually as if they are shifted sumultaneously to the left. Similarly, if the content of the display start address register is decremented, the displayed contents of the first, second, third and fourth lines look as if they are shifted simultaneously to the right. When the display start address is situated on the boundary of the display data region of the first line of the RAM, if the display start address is incremented or decremented, the result will be given by table 7

Table 7. Change of display start address

| Display Start Address |           |           |  |  |  |

|-----------------------|-----------|-----------|--|--|--|

| Before inc/dec        | After inc | After dec |  |  |  |

| (00)16                | (01)16    | (27)16    |  |  |  |

| (27)16                | (00)16    | (26),6    |  |  |  |

### 7 DISPLAY ADDRESS REGISTER

Thig is the register for designating the address of a displayed data of the RAM to be displayed by the liquid crystal.

To read all of the displayed data of the RAM during the times for the respective common signals, convert them to a character pattrern, and transfer them to the column driver; the content of the display address register is continuously and successively changed from the display start address, and the RAM address is scanned and designated.

### 8 ADDRESS DATA CONTROL

This is to execute display processig, instruction processing, and more for the address and data of the RAM and the ROM by controlling the cursor address register, display start address register, display address register, and so forth.

### 9 DISPLAY DATA/CHARACTER GENERATOR RAM (DD/CG RAM)

This is the RAM for storing the data and the character fonts for the character generator to be displayed by the liquid crystal. There are altogether 256 words, each word consisting of 9 bits. The 256 word RAM can be divided into a region to be used for display data (DD RAM) and a region to be used by the character generator (CG RAM). The division of the RAM into the DD RAM and the CG RAM is carried out by the instruction SF, and there are 4 kinds of divisions (table 8):

Table 8. Instruction SF and RAM word number

| Instruc                         | tion SF | RAM Word Number (9bits for a word |          |  |  |

|---------------------------------|---------|-----------------------------------|----------|--|--|

| R/                              | M       | DD RAM                            | !        |  |  |

| RA <sub>1</sub> RA <sub>0</sub> |         | DURAM                             | CG RAM   |  |  |

| 0                               | 0       | 256 words                         | 0 words  |  |  |

| 0                               | 1       | 224 words                         | 32 words |  |  |

| 1                               | 0       | 192 words                         | 64 words |  |  |

| 1                               | 1       | 160 words                         | 96 words |  |  |

## 9-1 Display Data RAM (DD RAM)

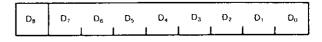

When 9 bits of a word in the RAM are used as a display data, 8 bits are used for display character code and the remaining 1 bit is used for underline display.

Data for designating whether there should be an underline, with one character as a unit.

Character code (display data) for designating one font out of 256 kinds.

Fig.11 RAM data.

## M50530-XXXFP

## DOT MATRIX LIQUID CRYSTAL DISPLAY CONTROLLER-DRIVER

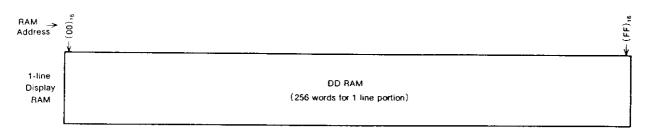

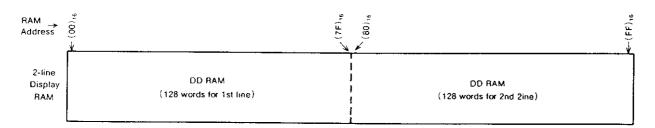

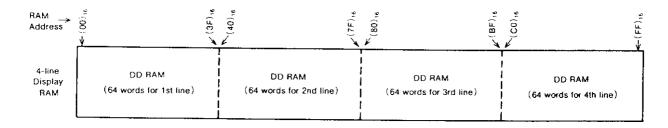

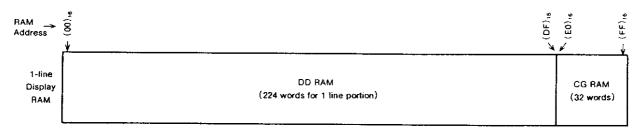

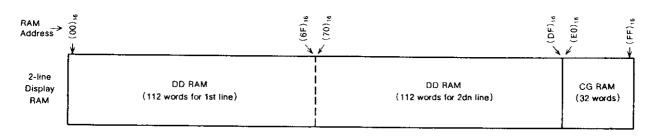

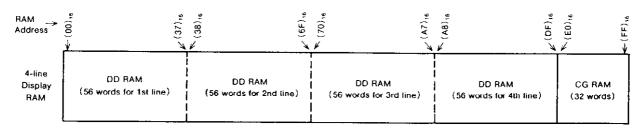

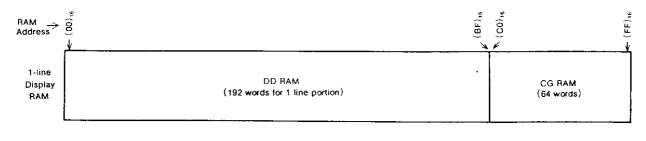

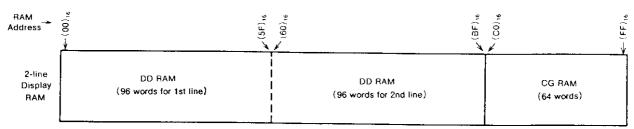

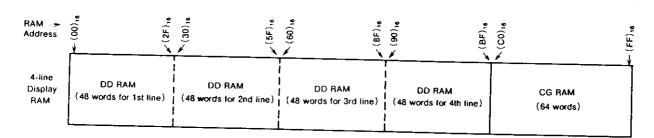

The DD RAM is given the composition of table 9 by the duty which designates one of 1-line display, 2-line display, and 4-line display, and the font setting instruction SF.

Next, the addresses for each display line of the DD RAM and the addresses of the CG RAM will be shown in the diagram (9-1-1  $\sim$  9-1-4) for each of these 4 kinds of RAM composition.

Table 9. Instruction SF and RAM composition

|                 | l               | 1-line Display     | 2-line Display     | 4-line Display    |

|-----------------|-----------------|--------------------|--------------------|-------------------|

| Instru-         | Font 1          | Duty 1/8           | Duty 1/16          | Duty 1/32         |

| SF              | 8/12 0          | Duty 1/12          | Duty 1/24          | Duty 1/48         |

|                 | DT <sub>1</sub> | 0                  | 0                  | 1                 |

| RA <sub>1</sub> | D <sub>To</sub> | 0.                 | 1                  | 0                 |

| 0               | 0               | 1 line×256 words   | 2 line X 128 words | 4 line X 64 words |

| 0               | 1               | 1 line X 224 words | 2 line X112 words  | 4 line × 56 words |

| 1               | 0               | 1 tine XT92 words  | 2 line × 96 words  | 4 line × 48 words |

| 1               | 1               | 1 line×160 words   | 2 line × 80 words  | 4 line X 40 words |

# 9-1-1 Case of 256 words for DD RAM and 0 word for CG RAM

# 9-1-2 Case of 224 words for DD RAM and 32 words for CG RAM

# 9-1-3 Case of 192 words for DD RAM and 64 words for CG RAM

# 9-1-4 Case of 160 words for DD RAM and 96 words for CG RAM

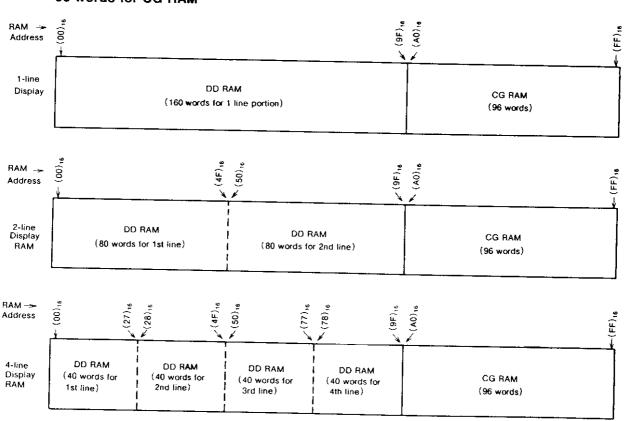

### 9-2 Character Generator RAM (CG RAM)

In the CG RAM the user can write an arbitrary font of  $5\times7$  dots or  $5\times11$  dots. A maximum of 12 character fonts in the case of  $5\times7$  dots, and a maximum of 6 fonts in the case of  $5\times11$  dots, can be written in the CG RAM.

The address of the CG RAM which is written a character font and the character code of the character font are made to correspond in a 1 to 1 fashion as shown in the diagram (9-2-1~9-2-4).

Next, an example of constructing a character font from an address and a data of the CG RAM for each character

code will be described.

### CHARACTER FONT OF 5X7 DOTS

Example for character code(FE)<sub>16</sub>

CG RAM upper addresses determined by character code

Example for character code(FF),6

| CG RAM Address |                |                |                |                |                |    |                |   |  |  |  |   |   |

|----------------|----------------|----------------|----------------|----------------|----------------|----|----------------|---|--|--|--|---|---|

| Α,             | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | Α, | A <sub>0</sub> |   |  |  |  |   |   |

|                |                |                |                |                | 0              | 0  | 0              |   |  |  |  |   |   |

|                |                |                |                |                | 0              | 0  | 1              |   |  |  |  |   |   |

|                |                |                |                |                | 0              | 1  | 0              |   |  |  |  |   |   |

|                | 1 1 1          | 1              | 0              | 0              | 1              | 1  |                |   |  |  |  |   |   |

| •              |                | •              | U              | 1              | 0              | 0  |                |   |  |  |  |   |   |

|                |                |                |                |                | 1              | 0  | 1              |   |  |  |  |   |   |

|                |                |                |                | 1              | 1              | 0  |                |   |  |  |  |   |   |

|                |                |                |                |                | 1              | 1  | 1              |   |  |  |  |   |   |

|                |                |                |                |                |                | 0  | 0              | 0 |  |  |  |   |   |

|                |                |                |                |                | 0              | 0  | 1              |   |  |  |  |   |   |

|                |                |                |                |                |                |    |                |   |  |  |  | 0 | 1 |

| 1              | ,              |                |                | 1              | 0              | 1  | 1              |   |  |  |  |   |   |

|                | •              | '              | •              | '              | 1              | 0  | 0              |   |  |  |  |   |   |

|                |                |                |                |                | 1              | 0  | 1              |   |  |  |  |   |   |

|                |                |                |                | ĺ              | 1              | 1  | 0              |   |  |  |  |   |   |

|                |                |                |                |                | 1              | 1  | 1              |   |  |  |  |   |   |

CG RAM Data D7 D6 D5 D4 D3 D2 D1 D0 0 0 0 0 Example for character 0 /// 0 /// 0 pattern "A" 0 0 0 0 0 0 0 0 0 0 0 0 0 Example for character 1 0 0 1 1 0 0 3 pattern "B" 0 0 0 0

The portion of the CG RAM marked with an "\*", namely, data  $D_7$   $D_6$   $D_5$  and data  $D_7 \sim D_0$  in which the address for  $A_2$   $A_1$   $A_0$  is  $(111)_2$ , will not be used as a pattern for a character font. However, it can be used for general data RAM.

### CHARACTER FONT OF 5×11 DOTS

|                                   | CG RAM Address |                |                |                |    |                |                |    |

|-----------------------------------|----------------|----------------|----------------|----------------|----|----------------|----------------|----|

|                                   | Α,             | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | Аз | A <sub>2</sub> | A <sub>1</sub> | Ao |

|                                   |                |                |                |                | 0  | 0              | 0              | 0  |

|                                   | 1              |                |                |                | 0  | 0              | 0              | 1  |

|                                   | -              |                |                |                | 0  | 0              | 1              | 0  |

|                                   |                |                |                |                | 0  | 0              | 1              | 1  |

| Example for character             |                |                |                |                | 0  | 1              | 0              | 0  |

| code(FE) <sub>16</sub>            | 1              |                |                |                | 1  | 0              | 1              | 0  |

|                                   |                |                |                | 1              | 0  | 1              | 1              | 0  |

|                                   | 1              | 1              | 1              | 0              | 0  | 1              | 1              | 1  |

|                                   |                | •              | •              |                | 1  | 0              | 0              | 0  |

|                                   |                |                |                |                | 1  | 0              | 0              | 1  |

|                                   |                |                |                | į              | 1  | 0              | 1              | 0  |

|                                   |                |                |                |                | 1  | 0              | 1              | 1  |

|                                   |                |                |                |                | 1  | 1              | 0              | 0  |

|                                   |                |                |                | :              | 1  | 1              | 0              | 1  |

| 00 B444                           |                |                |                | 1              | 1  | 1              | 1              | 0  |

| CG RAM upper addresses determined |                |                |                |                | 1  | 1_             | 1              | 1  |

| by character code                 | -              |                |                | 1              | 0  | 0              | 0              | 0  |

|                                   |                |                |                |                | 0  | 0              | 0              | 1  |

|                                   | ĺ              |                |                | i              | 0  | 0              | 1              | 0  |

|                                   |                |                |                | i              | 0  | 0              | 1              | 1  |

|                                   |                |                |                |                | 0  | 1              | 0              | 0  |

|                                   |                |                |                | - !            | 0  | 1              | 0              | 1  |

|                                   |                |                |                |                | 0  | 1              | 1              | 0  |

|                                   | 1              | t              | 1              | 1              | 0  | 1              | 1              | 1  |

|                                   |                | •              | •              | • :            | 1  | 0              | 0              | 0  |

| Example for character             |                |                |                |                | 1  | 0              | 0              | 1  |

| code(FF) <sub>16</sub>            |                |                |                |                | 1  | 0              | 1              | 0  |

|                                   |                |                |                |                | 1  | 0              | 1              | 1  |

|                                   |                |                |                |                | 1  | 1              | 0              | 0  |

| ŀ                                 |                |                |                | i              | 1  | 1              | 0              | 1  |

|                                   |                |                |                |                | 1  | 1              | 1              | 0  |

|                                   |                |                |                |                | 1  | 1              | 1              | 1  |

The portion marked with an "\*", namely data  $D_7$   $D_6$   $D_5$  and data  $D_7 \sim D_0$  in which the address  $A_3$   $A_2$   $A_1$   $A_0$  is in the range from  $(1011)_2$  to  $(1111)_2$ , will not be used as a pattern for character font. However, it can be used for general data RAM.

To write and read character pattern data for character font from the CG RAM, the address is set in the cursor address register with the instruction WC, analogous to the case of writing and reading a data from the DD RAM. Writing and reading are executed with the instructions WD and RD using 8 bits per word. Of the 8 bits in a word 5 bits are made to correspond to 5 dots in a line as character pattern data for the character font. The bits of the CG RAM data,  $(1)_2$  corresponds to the display selection by the LCD dots while  $(0)_2$  corresponds to the nondisplay selection. In the case of a character font of 5×7 dots, the bit is written 7 words for 7 line portions, and in the case of a character font of 5×11 dots, it is necessary to write the bit for 11 words for 11 line portions.

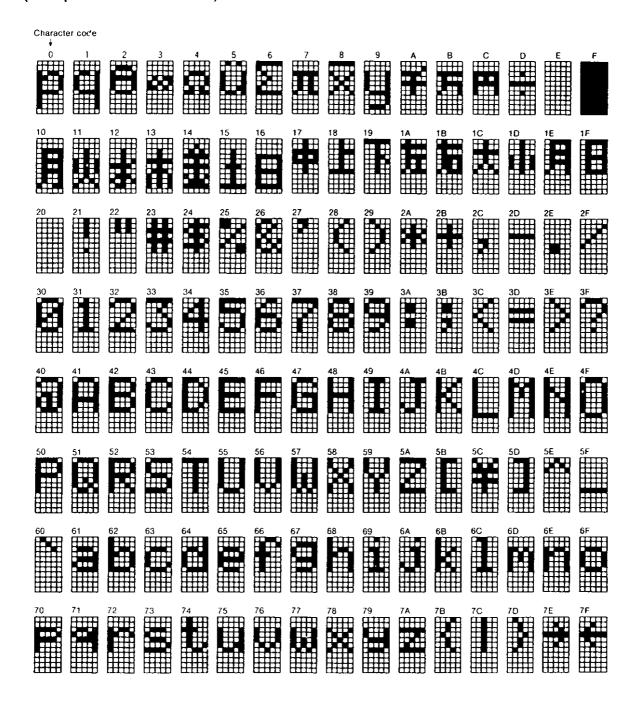

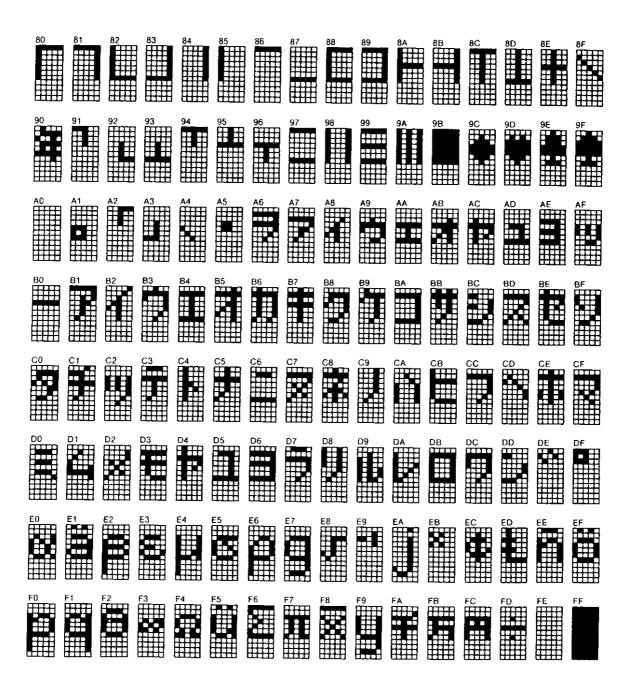

# 10 CHARACTER GENERATOR ROM (CG ROM)

This is the ROM for generating a fixed character tont from the character codes with display data 8 bits. The content of CG ROM (character fonts) is programable by mask ROM. 256 kinds of character fonts of  $5\times7$  dots or  $5\times11$  dots as dot-matrix characters can be stored.

These 256 kinds of font represent the sum of the number of the character fonts generated in the CG RAM and the number of the character fonts generated in the CG ROM. Accordingly, the number of fonts that can be generated in the CG RAM and the CG ROM varies depending upon the division ratio of the DD RAM and the CG RAM regions and also upon whether using  $5\times7$  dots or  $5\times11$  dots. Those combinations are shown in table 10.

The relationship between the range of the character codes corresponding to the CG RAM and the range of the character codes corresponding to the CG ROM will now be shown.

Of the character codes, the space code is a special code which is used for the clear display. All of the dot bits in the character font  $5\times11$  dots for the CG ROM content that corréspond to the space code are  $(0)_2$ , indicating nondisplay. And the space code must be set up between from character code  $(00)_{16}$  to  $(F3)_{16}$ .

When the DD RAM content is cleared by the autoclear or the instruction CH, all of the display data go to the space code.

Table 10. Display font number

| Dot Matrix  | Ins       | truction | SF              | CG                     | RAM                | CG ROM             |

|-------------|-----------|----------|-----------------|------------------------|--------------------|--------------------|

| Composition | Font 8/12 | ЯA,      | RA <sub>0</sub> | Memory Capacity(words) | Font Number(kinds) | Font Number(kinds) |

|             |           | 0        | 0               | 0                      | 0                  | 256                |

| 5×7         |           | 0        | 1               | 32                     | 4                  | 252                |

| dots        | ' [       | 1        | 0               | 64                     | 8                  | 248                |

|             | L i       | t        | 1               | 96                     | 12                 | 244                |

|             |           | 0        | 0               | 0                      | 0                  | 256                |

| 5×11        | n [       | 0        | 1               | 32                     | 2                  | 254                |

| dots        | ! " [     | 1        | 0               | 64                     | 4                  | 252                |

|             | [ ]       | 1        | 1               | 96                     | 6                  | 250                |

# CASE OF CHARACTER FONT OF 5×7 DOTS

# CASE OF CHARACTER FONT OF 5×11 DOTS

# 11 SERIES/PARALLEL CONVERSION CIRCUIT

This is the circuit for sending a parallel font pattern data from the CG ROM or the CG RAM to the column driver by converting it to a serial data.

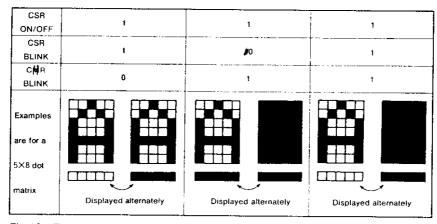

# 12 DISPLAY, CURSOR, AND BLINK CONTROLS

They control the ON/OFF of the LCD, cursor display, blinking display, and so forth. Various display modes given below can be set using the instruction SD.

- · ON/OFF of the entire display

- . ON/OFF of the cursor

- o ON/OFF of the underline display

- · Blinking of the cursor display

- Blinking of a character at the cursor position

By the use of the instruction SB, 1 blinking frequency can be selected out of the following 4 kinds.

0.5Hz 1Hz 2Hz 4Hz

(for an oscillation frequency of about 2.5MHz)

The cursor will be displayed on the lowest line of the font matrix as indicated below.

Fig.12. Position of character font and cursor.

The cursor display and the blinking display will be displayed at the digit position of the RAM display data which is designated by the cursor address register.

When the content of the cursor register is  $(69)_{16}$  and the content of the display start register is  $(17)_{16}$ , the display positions of the cursor and the blinking are as shown below.

• 1 line of LCD (for 160 words of DD RAM and 96 words of CG RAM)

Cursor position

| Digit of LCD | 1st digit           | 2nd digit           | <del></del> , | 81st digit          | 82nd digit          | 83rd digit          | 84th digit          | 59th digit          | 160th digit         |

|--------------|---------------------|---------------------|---------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| 1-line LCD   | R(17) <sub>16</sub> | R(18) <sub>16</sub> |               | R(67) <sub>16</sub> | R(68) <sub>16</sub> | R(69) <sub>16</sub> | R(6A) <sub>16</sub> | R(15) <sub>16</sub> | R(16) <sub>16</sub> |

• 2 lines of LCD (same conditions as above)

Cursor position

| Digit of LCD     | 1st digit           | 2 digit             | 3rd digit           | 4th digit           | 5th digit           | 77th dìgit           | 78th                | 79th digit          | 80th digit          |

|------------------|---------------------|---------------------|---------------------|---------------------|---------------------|----------------------|---------------------|---------------------|---------------------|

| LCD/<br>1st line | R(17) <sub>16</sub> | R(18) <sub>16</sub> | R(19) <sub>16</sub> | R(1A) <sub>16</sub> | R(18) <sub>16</sub> | R(13) <sub>16</sub>  | R(14) <sub>16</sub> | R(15) <sub>16</sub> | R(16) <sub>16</sub> |

| 2nd line         | R(67) <sub>16</sub> | R(68) <sub>16</sub> | R(69) <sub>16</sub> | R(6A) <sub>16</sub> | R(6B) <sub>16</sub> | FI(63) <sub>16</sub> | R(64) <sub>16</sub> | R(65) <sub>16</sub> | R(66) <sub>16</sub> |

• 4 lines of LCD (same conditions as above)

Cursor position

| Digit of LCD     | tst digit           | 2nd digit           | 3rd digit           | 4th digit            | 5th digit           | <br>37th digit      | 38th digit          | 39th digit          | 40th digit          |

|------------------|---------------------|---------------------|---------------------|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| LCD/<br>1st line | R(17) <sub>16</sub> | R(18) <sub>16</sub> | R(19) <sub>16</sub> | R(1A) <sub>16</sub>  | R(1B) <sub>16</sub> | R(13), <sub>6</sub> | R(14) <sub>16</sub> | R(15) <sub>16</sub> | R(16) <sub>16</sub> |

| 2nd line         | R(3F) <sub>16</sub> | R(40) <sub>16</sub> | R(41) <sub>16</sub> | R(42) <sub>16</sub>  | R(43) <sub>16</sub> | R(3B) <sub>16</sub> | R(3C) <sub>16</sub> | R(3D) <sub>16</sub> | R(3E) <sub>16</sub> |

| 3rd line         | R(67) <sub>16</sub> | R(68) <sub>16</sub> | R(69) <sub>16</sub> | R(6A) <sub>16</sub>  | R(6B) <sub>16</sub> | R(63) <sub>16</sub> | R(64) <sub>16</sub> | R(65) <sub>16</sub> | R(66) <sub>16</sub> |

| 4th line         | R(8F) <sub>16</sub> | R(90) <sub>16</sub> | R(91) <sub>16</sub> | FI(92) <sub>16</sub> | R(93) <sub>16</sub> | R(8B) <sub>16</sub> | R(8C) <sub>16</sub> | R(8D) <sub>16</sub> | R(8E) <sub>16</sub> |

## 13 COMMON SIGNAL OUTPUT CIRCUIT

There are 32 lines of common signal drive output which directly drive the common side of the LCD.

Therefore, it is possible to directly drive the common signals with the display duties ranging from 1/8 to 1/32. Further, by connecting a common driver for expansion, M50521FP or M50524FP in the outside, it becomes possible to drive common signals up to a duty of 1/48. The output signal CMD is the common signal to be sent to the external common driver.

The unused common drive outputs become nondisplay selection signals. For example, when duty is 1/16, the common outputs COM1~COM16 output common scanning signals, but COM17~COM32 always output nondisplay selection signals.

The instruction SF can set the character font and the duty, and the number of display lines and the effective common signal are given as shown in the Table. 11.

### 14 COLUMN SIGNAL OUTPUT CIRCUIT

The display data which is converted to a character font pattern is sent to a 40-bit shift register as serial pattern data, and is then latched.

The latched output controls the driver to output 40 lines of column signals that directly drive the fiquid crystal display. With the 40 lines of column signals it is possible to directly drive an 8 digit portion LCD for either a 1-line, 2-line, or 4-line display.

The number of displayed digits can be expanded by transferring the character font pattern data to an external column driver (M50521FP or M50524FP) from the column data output signal CLD. Depending upon the number of bits of the column driver (which is connected externally) it is possible to expand the character display from an arbitrary digit number to a maximum digit number.

### 15 TIMING SIGNAL GENERATING CIRCUIT

The oscillation circuit generates various kinds of internal timing signals to be used for display processing, instruction processing, and so forth.

In addition, the circuit generates timing signals for controlling the external LCD driver in order to expand the digit number of the LCD.

The processig of an instruction is executed totally independently of the LCD processing so that there will be no change in the processing time of LCD which is determined by the duty employed.

Further, the period for tiquid crystal to display all of the display patterns once, (the period of the common signal) depends only on the oscillation frequency. The period of the cursor/character display blinking, also depends only on the oscillation frequency.

Table 11. Effective common signal output

| <b>0</b> 1     | ln           | struction : | SF  |      | Number of     | Effective Common |

|----------------|--------------|-------------|-----|------|---------------|------------------|

| Character Font | Font<br>8/12 | DT,         | DΤο | Duty | Display Lines | Signal Output    |

|                |              | 0           | 0   | 1/8  | 1             | COM1~COM8        |

| 5 × 8 dots     | 1            | 0           | 1   | 1/16 | 2             | COM1~COM16       |

|                |              | 1           | 0   | 1/32 | 4             | COM1~COM32       |

|                | Ţ            | 0           | 0   | 1/12 | 1             | COM1~COM12       |

| 5 X12 dats     | 0            | 0           | 1   | 1/24 | 2             | COM1~COM24       |

|                | ĺ            | 1           | 0   | 1/48 | 4             | *COM1~COM32      |

<sup>By the use of an external common driver for expansion COM33~COM48 can be generated.

A second of the common driver for expansion COM33~COM48 can be generated.

By the use of an external common driver for expansion COM33~COM48 can be generated.

By the use of an external common driver for expansion COM33~COM48 can be generated.

By the use of an external common driver for expansion COM33~COM48 can be generated.

By the use of an external common driver for expansion COM33~COM48 can be generated.

By the use of an external common driver for expansion COM33~COM48 can be generated.

By the use of an external common driver for expansion COM33~COM48 can be generated.

By the use of the common driver for expansion COM33~COM48 can be generated.

By the common driver for expansion common driver for expansion COM33~COM48 can be generated.

By the common driver for expansion common driver for</sup>

### 16 OSCILLATOR

To generate an internal clock, it is possible to let the builtin oscillator induce self-oscillation by connecting a simple external part. It is also possible to input a clock to the oscillator from the outside.

### 16-1 Using an external clock

Input the external clock to the oscillator input terminal OSC1, and leave the oscillator output terminal OSC2 disconnected.

$T_H + T_L = 330 \sim 500 ns$

### 16-2 Using built-in oscillator

(16-2-1) The built-in oscillator can be set to oscillate by connecting an external resistor for oscillation between the terminals OSC1 and OSC2.

Try to minimize the wire length for connecting the resistor in order to reduce the external capacitance to be connected to the terminals OSC1 and OSC2.

(16-2-2) It is possible to set the built-in oscillator into oscillation by connecting a ceramic vibrator between the terminals OSC1 and OSC2 as in the figure.

Next, the oscillation frequency of the oscillator and the period of the common signal are related by the following equations:

equations:

$$T_{COM} = \frac{36864}{f_{OSC}}$$

Here,  $T_{COM}$ : Period of common signal (s)

$$f_{\text{COM}} = f_{\text{OSC}}$$

$f_{\text{COM}}$ : Inverse of  $T_{\text{COM}}$  (Hz)

$f_{\text{OSC}} = f_{\text{OSC}}$ : Oscillation frequency (Hz)

For example, to obtain 70Hz for  $f_{\text{COM}}$ ,  $f_{\text{OSC}}$  must be about 2.58MHz.

### 17 AUTOCLEAR

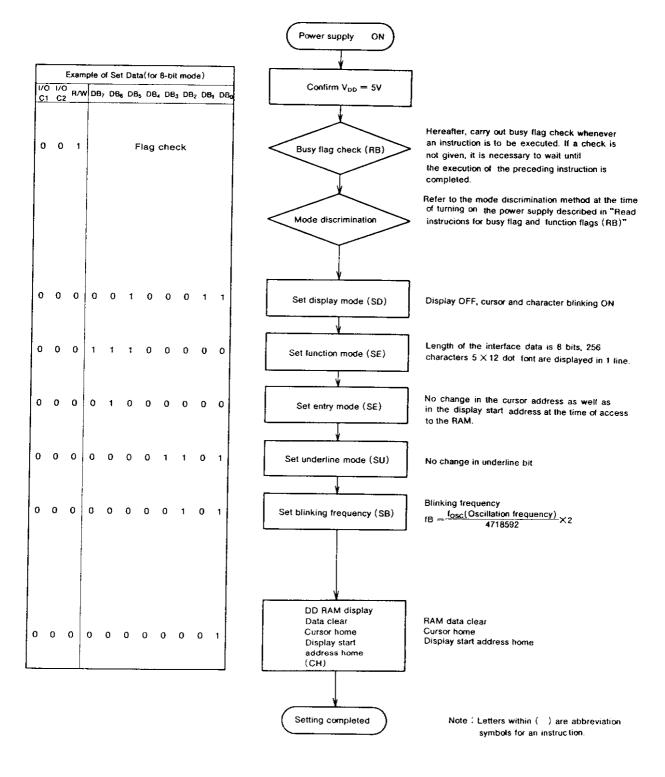

After closing the power supply, a built-in autoclear circuit is actuated to linitialize RAM and various kinds of mode flags. While the autoclear is in operation, the busy flag is set to  $(1)_2$ .

- $^{\circ}$  All of the 8bit display data of the RAM display data region are set to the space code, and all of the underline bits are set to  $(0)_2$ (nondisplaying)

- $^{\circ}$  The display start address and the cursor address are set to (00)  $_{16}.$

- The mode flags to be used for the instructions are initial-

ized as Fig. 13

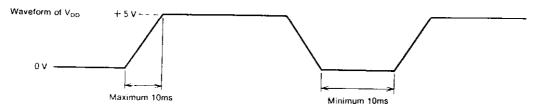

To operate the autoclear circuit without failure please be sure to let the power supply  $V_{DD}$  satisfy the conditions indicated in Fig. 14. When these conditions are not fulfilled, it is necessary to meet the conditions by the execution of instructions.

| Function mode                      | 1/00                    | FONT                   | DL              | JTY | R/     | AM.     |

|------------------------------------|-------------------------|------------------------|-----------------|-----|--------|---------|

| (Instruction SF)                   | 8/4                     | 8/12                   | DT <sub>1</sub> | DΤο | RA,    | RAo     |

|                                    | 1                       | 0                      | 0               | 0   | 0      | 0       |

| Entry mode                         | -                       |                        |                 |     | T .    |         |

| •                                  | CSR                     | CSR CQ                 | NOITION         | DSP | DSP CO | NOITION |

| (Instruction SE)                   | D/I                     | W                      | R               | D/I | W      | R       |

|                                    | 0                       | 0                      | 0               | 0   | 0      | 0       |

| Display mode                       | DSP                     | CSR                    | UND             | CSR | CHR    |         |

| (Instruction SD)                   |                         | ON/OFF                 |                 |     |        |         |

|                                    | 0                       | 0                      | 0               | 1   | 1      |         |

| Underline mode<br>(Instruction SU) | USR<br>ON/OFF<br>0      | UND<br>S/R             |                 |     |        |         |

| Blinking mode<br>(Instruction SB)  | BLINK<br>B <sub>1</sub> | FREQ<br>B <sub>0</sub> |                 |     |        |         |

Fig.13 Mode of initialization

Fig.14  $V_{DD}$  waveform

An example of a software initialization method is shown below.

## M50530-XXXFP

## DOT MATRIX LIQUID CRYSTAL DISPLAY CONTROLLER-DRIVER

## INSTRUCTION CODE

Instruction Code

|                  | Abbreviation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | for                    | PC PC                      | WC.                         | RS                         | WS                          | Ĉ.            | WD              |      | 88                             |      | SF                |               | SE             |     | S<br>S               | MA                                 |     | Su                 | I.W.                    |            | es<br>S                | ₩<br>H                                     | O T                                                                      | NOP          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------------|-----------------------------|----------------------------|-----------------------------|---------------|-----------------|------|--------------------------------|------|-------------------|---------------|----------------|-----|----------------------|------------------------------------|-----|--------------------|-------------------------|------------|------------------------|--------------------------------------------|--------------------------------------------------------------------------|--------------|

|                  | Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Time for               | 20μs                       | 20µs                        | 20µ8                       | 20µ\$                       | 20 μ s        | 20µs            |      | 0                              |      | 20µs              |               | 20,4\$         |     | 20µ\$                | 20µs                               |     | 20,4.\$            | 2043                    |            | 20 n s                 | 20µs                                       | 1.25ms                                                                   | 20µs         |

|                  | - Citatoria Cita | וופת לכווכאן בחוכנווכא | Read cursor address of RAM | Write cursor address of RAM | Read display start address | Write display start address | Read RAM data | Write RAM data  |      | Read busy flag and other flags |      | Set function mode |               | Set entry mode |     | Set display mode     | Shift cursor/display-start address |     | Set underline mode | Write RAM underline bit |            | Set blinking frequency | Cursor home and display start address home | Clear cursor of DD RAM display data home, and display start address home | No operation |

| 8 0              | Input to 1.St                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Output from LSI        | Output                     | Input                       | Output                     | fnput                       | Output        | Input           |      | Output                         |      | -<br>Judut        |               | indu           |     | ndu.                 | Input                              |     | Input              | Input                   |            | Input                  | Input                                      | Input                                                                    | Input        |