## **Application Note 1293**

#### Introduction

The bipolar junction transistor (BJT) is guite often used as a low noise amplifier in cellular, PCS, and pager applications due to its low cost. With a minimal number of external matching networks, the BJT can guite often produce an LNA with RF performance considerably better than an MMIC. Of equal importance is the DC performance. Although the device's RF performance may be quite closely controlled, the variation in device dc parameters can be quite significant due to normal process variations. It is not unusual to find a 2 or 3 to 1 ratio in device h<sub>FE</sub>. Variation in h<sub>FE</sub> from device to device will generally not show up as a difference in RF performance. In other words, two devices with widely different hFE's can have similar RF performance as long as the devices are biased at the same VCE and IC. This is the primary purpose of the bias network, i.e., to keep V<sub>CE</sub> and I<sub>C</sub> constant as the dc parameters vary from device to device.

Quite often the bias circuitry is overlooked due to its apparent simplicity. With a poorly designed fixed bias circuit, the variation in I<sub>C</sub> from lot to lot can have the same maximum to minimum ratio as the h<sub>FE</sub> variation from lot to lot. With no compensation, as h<sub>FE</sub> is doubled, I<sub>C</sub> will double. It is the task of the dc bias circuit to maximize the circuit's tolerance to h<sub>FE</sub> variations. In addition, transistor parameters can vary over temperature causing a drift in I<sub>C</sub> at temperature. The low power supply voltages typically available for handheld applications also make it more difficult to design a temperature stable bias circuit.

One solution to the biasing dilemma is the use of active biasing. Active biasing often makes use of an IC or even just a PNP transistor and a variety of resistors, which effectively sets  $V_{\text{CE}}$  and  $I_{\text{C}}$  regardless of variations in device  $h_{\text{FE}}$ . Although the technique of active biasing would be the best choice for the control of device to device variability and over temperature variations, the cost associated with such an arrangement is usually prohibitive.

Other biasing options include various forms of passive biasing. Various passive biasing circuits will be discussed along with their advantages and disadvantages.

### **Various BJT Passive Bias Circuits**

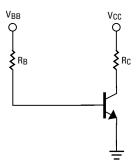

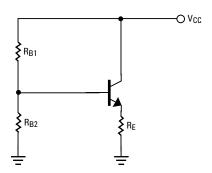

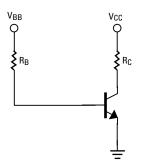

Passive biasing schemes usually consist of two to five resistors properly arranged about the transistor. Various passive biasing schemes are shown in Figure 1. The simplest form of passive biasing is shown as Circuit #1 in Figure 1. The collector current I<sub>C</sub> is simply h<sub>FE</sub> times the base current I<sub>B</sub>. The base current is determined by the value of R<sub>B</sub>. The collector voltage V<sub>CE</sub> is determined by subtracting the voltage drop across resistor R<sub>C</sub> from the power supply voltage  $V_{CC}$ . As the collector current is varied, the V<sub>CE</sub> will change based on the voltage drop across R<sub>C</sub>. Varying h<sub>EE</sub> will cause I<sub>C</sub> to vary in a fairly direct manner. For constant  $V_{CC}$  and constant  $V_{BE}$ ,  $I_{C}$ will vary in direct proportion to hFE. As an example, as hFE is doubled, collector current, IC, will also double. Bias circuit #1 provides no compensation for variation in device h<sub>FE</sub>.

Figure 1A. Circuit #1 - Non-stabilized BJT Bias Network

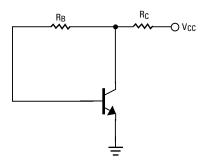

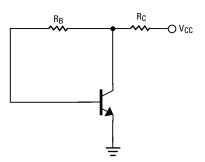

Bias circuit #2 provides voltage feedback to the base current source resistor R<sub>B</sub>. The base current source is fed from the voltage V<sub>CE</sub> as opposed to the supply voltage V<sub>CC</sub>. The value of the base bias resistor R<sub>B</sub> is calculated based upon nominal device V<sub>BE</sub> and the desired V<sub>CE</sub>. Collector resistor R<sub>C</sub> has both I<sub>C</sub> and I<sub>B</sub> flowing through it. The operation of this circuit is best explained as follows. An increase in  $h_{\text{FE}}$  will tend to cause  $I_{\text{C}}$  to increase. An increase in I<sub>C</sub> causes the voltage drop across resistor R<sub>C</sub> to increase. The increase in voltage across R<sub>C</sub> causes V<sub>CE</sub> to decrease. The decrease in V<sub>CE</sub> causes IB to decrease because the potential difference across base bias resistor R<sub>B</sub> has decreased. This topology provides a basic form of negative feedback which tends to reduce the amount that the collector current increases as h<sub>FE</sub> is increased.

Figure 1B. Circuit #2 – Voltage Feedback BJT Bias Network

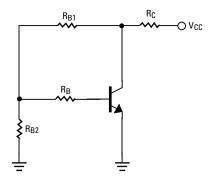

Figure 1C. Circuit #3 – Voltage Feedback with Current Source BJT Bias Network

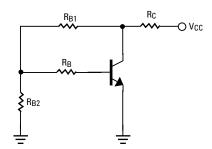

Bias circuit #3 has been quite often written up in past literature but predominately when very high  $V_{CC}$  (>15 V) and  $V_{CE}$  (>12 V) has been used [1]. The voltage divider network consisting of  $R_{B1}$  and  $R_{B2}$  provides a voltage divider from which resistor  $R_B$  is connected. Resistor  $R_B$  then determines the base current.  $I_B$  times  $I_{FE}$  provides  $I_C$ . The voltage drop across  $I_C$  is determined by the collector current  $I_C$ , the bias current  $I_B$ , and the current consumed by the voltage divider consisting of  $I_{CE}$  and  $I_{CE}$  This circuit provides similar voltage feedback to bias circuit #2.

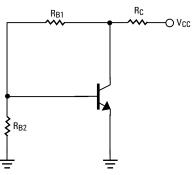

Bias circuit #4 is similar to bias circuit #3 with the exception that the series current source resistor  $R_B$  is omitted. This circuit is seen quite often in bipolar power amplifier design with resistor  $R_{B2}$  replaced by a series silicon power diode providing temperature compensation for the bipolar device. The current flowing through resistor  $R_{B1}$  is shared by both resistor  $R_{B2}$  and the emitter base junction  $V_{BE}$ . The greater the current through resistor  $R_{B2}$ , the greater the regulation of the emitter base voltage  $V_{BE}$ .

Figure 1D. Circuit #4 – Voltage Feedback with Voltage Source BJT Bias Network

Figure 1E. Circuit #5 – Emitter Feedback BJT Bias Network

Bias circuit #5 is the customary textbook circuit for biasing BJTs. A resistor is used in series with the device emitter lead to provide voltage feedback. This circuit ultimately provides the best control of  $h_{FE}$  variations from device to device and over temperature. The only disadvantage of this circuit is that the emitter resistor must be properly bypassed for RF. The typical bypass capacitor quite often has internal lead inductance which can create unwanted regenerative feedback. The feedback quite often creates device instability. Despite the problems associated with using the emitter resistor technique, this biasing scheme generally provides the best control on  $h_{FE}$  and over temperature variations.

The sections that follow begin with a discussion of the BJT model and its temperature dependent variables. From the basic model, various equations are developed to predict the device's behavior over h<sub>FE</sub> and temperature variations. This article is an update to the original article written by Kenneth Richter of Hewlett-Packard [2] and Hewlett-Packard Application Note 944-1 [3].

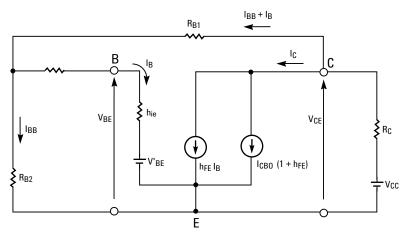

Figure 2. Gummel Poon model of BJT with Voltage Feedback and Constant Base Current Source Network

## **BJT Modeling**

The BJT is modeled as two current sources as shown in Figure 2. The primary current source is  $h_{FE}$   $l_B$ . In parallel is a secondary current source  $l_{CBO}$  (1+  $h_{FE}$ ) which describes the leakage current flowing through a reverse biased PN junction.  $l_{CBO}$  is typically 1x10-7 A @ 25°C for an Avago Technologies HBFP-0405 transistor. V  $l_{BE}$  is the internal base emitter voltage with  $l_{IE}$  representing the equivalent Hybrid PI input impedance of the transistor.  $l_{IE}$  is also equal to  $l_{IE}$  /  $l_{IE}$  where  $l_{IE}$  = 40 @ +25°C.  $l_{IE}$  will be defined as measured between the base and emitter leads of the transistor. It is equivalent to V'  $l_{IE}$  +  $l_{IE}$   $l_{IE}$   $l_{IE}$   $l_{IE}$   $l_{IE}$  approximately 0.78 V @ 25°C for the HBFP-0405 transistor.

The device parameters that have the greatest change as temperature is varied consist of h<sub>FE</sub>, V'  $_{BE}$ , and l<sub>CBO</sub>. These temperature dependent variables have characteristics which are process dependent and fairly well understood. h<sub>FE</sub> typically increases with temperature at the rate of 0.5% / °C. V'  $_{BE}$  has a typical negative temperature coefficient of -2 mV / °C. This indicates that V<sub>BE</sub> decreases 2 mV for every degree increase in temperature. l<sub>CBO</sub> typically doubles for every 10°C rise in temperature. Each one of these parameters contributes to the net resultant change in collector current as temperature is varied.

For each bias network shown in Figure 1, several sets of simplified circuit equations have been generated to allow calculation of the various bias resistors. These are shown in Figures 3, 4, 5, 6, and 7. Each of the bias resistor values is calculated based on various design parameters such as desired I<sub>C</sub>, V<sub>CE</sub>, power supply voltage V<sub>CC</sub> and nominal h<sub>FE</sub>. I<sub>CBO</sub> and h<sub>ie</sub> are assumed to be zero for the basic calculation of resistor values.

Additional designer provided information is required for the three circuits that utilize the voltage divider consisting of  $R_{B1}$  and  $R_{B2}$ . In the case of the bias network that uses voltage feedback with current source, the designer must pick the voltage across  $R_{B2}$  ( $V_{RB2}$ ) and the bias current through resistor  $R_{B2}$  which will be termed  $I_{RB2}$ .

Choose  $V_{CE} > V_{RB2} > V_{BE}$

Suggest  $V_{RB2} = 1.5 \text{ V}$

Suggest I<sub>RB2</sub> to be about 10% of I<sub>C</sub>

The voltage feedback with a voltage source network and the emitter feedback network also require that the designer choose  $I_{RB2}$ . As will be learned later, the ratio of  $I_C$  to  $I_{RB2}$  is an important ratio that plays a major part in bias stability.

An equation was then developed for each circuit that calculates collector current,  $I_C$ , based on nominal bias resistor values and typical device parameters including  $h_{FE}$ ,  $I_{CBO}$ , and  $V'_{BE}$ . MATHCAD version 7 was used to help develop the  $I_C$  equation. Although the  $I_C$  equation starts out rather simply, it develops into a rather lengthy equation for some of the more complicated circuits. MATHCAD helped to simplify the task.

$$R_B = \frac{V_{CC} - V_{BE}}{I_B} \qquad \qquad R_C = \frac{V_{CC} - V_{CE}}{I_C}$$

$$I_{C} = \frac{h_{FE} \bullet (V_{CC} - V'_{BE})}{h_{ie} + R_{B}} + I_{CBO} \bullet (1 + h_{FE})$$

Figure 3. Equations for Non-stabilized Bias Network

$$R_B = \frac{V_{CE} \cdot V_{BE}}{I_B} \qquad \qquad R_C = \frac{V_{CC} \cdot V_{CE}}{I_C + I_B}$$

$$I = \frac{h_{FE} \bullet (V_{CC} - V'_{BE}) + I_{CBO} \bullet (1 + h_{FE}) \bullet (h_{ie} + R_B + R_C)}{h_{ie} + R_B + R_C \bullet (1 + h_{FE})}$$

Figure 4. Equations for Voltage Feedback Bias Network

$$R_B = \; \frac{V_{RB2} \cdot V_{BE}}{I_B} \qquad \qquad R_C = \; \frac{V_{CC} \cdot V_{CE}}{I_C + I_{B2} + I_B} \label{eq:RB2}$$

$$R_{B1} = \frac{V_{CE} \cdot V_{RB2}}{I_{B2} + I_{B}} \qquad R_{B2} = \frac{V_{RB2}}{I_{B2}}$$

Designer must choose  $I_{B2}$  and  $V_{RB2}$  such that  $V_{CE} > V_{RB2} > V_{BE}$

$$I_{C} = \begin{bmatrix} -V'_{BE} \bullet (R_{B1} + R_{B2} + R_{C}) - R_{B2} \bullet [R_{C} \bullet I_{CB0} \bullet (1 + h_{FE}) - V_{CC}] \\ (R_{B} + h_{ie}) \bullet (R_{B1} + R_{B2} + R_{C}) + R_{B2} \bullet (h_{FE} \bullet R_{C} + R_{C} + R_{B1}) \end{bmatrix} \bullet h_{FE} + I_{CB0} \bullet (1 + h_{FE})$$

Figure 5. Equations for Voltage Feedback with Current Source Bias Network

$$R_{B2} = \frac{V_{BE}}{I_{B2}} \qquad R_{C} = \frac{V_{CC} - V_{CE}}{I_{C} + I_{B} + I_{B2}}$$

$$R_{B1} = \frac{V_{CE} - (I_{B2} \bullet R_{B2})}{I_{B} + I_{B2}}$$

Designer must choose  $I_{B2}$

$$I_{C} = \frac{-\frac{R_{C}}{h_{FE}} \bullet I_{CBO} - R_{C} \bullet I_{CBO} + \frac{R_{C}}{R_{B2}} \bullet V'_{BE} - \frac{R_{C}}{(R_{B2} \bullet h_{FE})} \bullet h_{ie} \bullet I_{CBO} - \frac{R_{C}}{R_{B2}} \bullet h_{ie} \bullet I_{CBO} - \frac{R_{B1}}{h_{FE}} \bullet I_{CBO} - \frac{R_{B1}}{h_{FE}} \bullet I_{CBO} - \frac{R_{B1}}{h_{FE}} \bullet I_{CBO} - \frac{R_{B1}}{h_{E}} \bullet I_{CBO} - \frac{R_{B1}}{h$$

Figure 6. Equations for Voltage Feedback with Voltage Source Bias Network

$$R_{E} = \frac{V_{CC} \cdot V_{CE}}{I_{C} \left(1 + \frac{1}{h_{FE}}\right)} \qquad R_{1} = \frac{V_{CC} \cdot I_{B2} \bullet R_{2}}{I_{B2} + I_{B}}$$

$$Pick I_{B2} \text{ to be } 10\% \text{ of } I_{C}$$

$$R_{B2} = \frac{V_{RB2}}{I_{B2}} \qquad V_{RB2} = V'_{BE} + (I_{B} + I_{C}) \bullet R_{E}$$

$$- \left[V'_{BE} \cdot \frac{1}{h_{FE}} \bullet h_{ie} \bullet I_{CBO} \cdot h_{ie} \bullet I_{CBO} \cdot \frac{R_{E}}{h_{FE}} \bullet I_{CBO} \cdot \frac{R_{E}}{R_{2}} \bullet I_{CBO} \cdot \frac{R_{1}}{R_{2}} \bullet V'_{BE} \cdot \frac{R_{1}}{(R_{2} \bullet h_{FE})} \bullet h_{ie} \bullet I_{CBO} \cdot \frac{R_{1}}{R_{2}}$$

$$\bullet h_{ie} \bullet I_{CBO} \cdot \frac{R_{1}}{R_{2}} \bullet \frac{R_{E}}{h_{FE}} \bullet I_{CBO} \cdot \frac{R_{1}}{R_{2}} \bullet R_{E} \bullet I_{CBO} \cdot \frac{R_{1}}{h_{FE}} \bullet R_{E} + \frac{R_{1}}{h_{FE}} \bullet R_{E} + \frac{R_{1}}{h_{FE}}$$

$$I_{C} = \frac{1}{h_{FE}} \bullet h_{ie} + \frac{R_{E}}{h_{FE}} + R_{E} + \frac{R_{1}}{(R_{2} \bullet h_{FE})} \bullet h_{ie} + \frac{R_{1}}{R_{2}} \bullet \frac{R_{E}}{h_{FE}} + \frac{R_{1}}{R_{2}} \bullet R_{E} + \frac{R_{1}}{h_{FE}}$$

Figure 7. Equations for Emitter Feedback Bias Network

# Design example using the Avago Technologies' HBFP-0405 BJT

The HBFP-0405 transistor will be used as a test example for each of the bias circuits. The Avago Technologies HBFP-0405 is described in an application note  $^{[4]}$  as a low noise amplifier for 1800 to 1900 MHz applications. The HBFP-0405 will be biased at a  $V_{CE}$  of 2.7 Volts and a drain current  $I_{C}$  of 5 mA. A power supply voltage of 3 volts will be assumed. The nominal  $h_{FE}$  of the HBFP-0405 is 80. The minimum is 50 while the maximum is 150. The calculated bias resistor values for each bias circuit are described in Table 1.

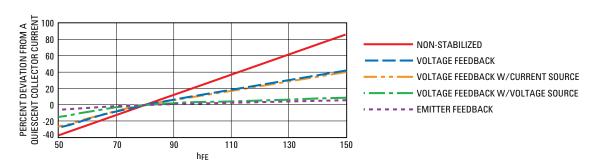

With the established resistor values,  $I_C$  is calculated based on minimum and maximum  $h_{FE}$ . The performance of each bias circuit with respect to  $h_{FE}$  variation is shown in Table 2. Bias circuit #1 clearly has no compensation for varying  $h_{FE}$  allowing  $I_C$  to increase 85% as  $h_{FE}$  is taken to its maximum. Circuit #2 with very simple collector feedback offers considerable compensation due to  $h_{FE}$  variations allowing an increase of only 42%.

Surprisingly, circuit #3 offers very little improvement over circuit #2. Circuit #4 provides considerable improvement in  $h_{FE}$  control by only allowing a 9% increase in  $I_C$ . Circuit #4 offers an improvement over the previous circuits by providing a stiffer voltage source across the base emitter junction. As will be shown later, this circuit has worse performance over temperature as compared to circuits #2 and #3. However, when both  $h_{FE}$  and temperature are considered, circuit #4 will appear to be the best performer for a grounded emitter configuration. As expected, circuit #5 provides the best control on  $I_C$  with varying  $h_{FE}$  allowing only a 5.4% increase in  $I_C$ . Results are very much power supply dependent and with higher  $V_{CC}$ , results may vary significantly.

Table 1. Bias resistor values for HBFP-0405 biased at  $V_{CE} = 2 \text{ V}$ ,  $V_{CC} = 2.7 \text{ V}$ ,  $I_C = 5 \text{ mA}$ ,  $h_{FE} = 80 \text{ for the various bias networks}$

| Resistor        | Non-stabilized<br>Bias Network | Voltage Feedback<br>Bias Network | Voltage Feedback<br>w/Current Source<br>Bias Network | Voltage Feedback<br>w/Voltage Source<br>Bias Network | Emitter Feedback<br>Bias Network |

|-----------------|--------------------------------|----------------------------------|------------------------------------------------------|------------------------------------------------------|----------------------------------|

| R <sub>C</sub>  | 140 Ω                          | 138 Ω                            | 126 Ω                                                | 126 Ω                                                |                                  |

| $R_B$           | 30770 Ω                        | 19552 Ω                          | 11539 Ω                                              | ·                                                    |                                  |

| R <sub>B1</sub> |                                |                                  | 889 Ω                                                | 2169 Ω                                               | 2169 Ω                           |

| R <sub>B2</sub> |                                |                                  | 3000 Ω                                               | 1560 Ω                                               | 2960 Ω                           |

| $R_{E}$         |                                |                                  |                                                      |                                                      | 138 Ω                            |

Table 2. Summary of  $I_C$  variation vs.  $h_{FE}$  for various bias networks for the HBFP-0405  $V_{CC}=2.7$  V,  $V_{CE}=2$  V,  $I_C=5$  mA,  $T_J=+25$ °C

| Bias<br>Circuit                                                          | Non-stabilized<br>Bias Network | Voltage Feedback<br>Bias Network | Voltage Feedback<br>w/Current Source<br>Bias Network | Voltage Feedback<br>w/Voltage Source<br>Bias Network | Emitter Feedback<br>Bias Network |

|--------------------------------------------------------------------------|--------------------------------|----------------------------------|------------------------------------------------------|------------------------------------------------------|----------------------------------|

| I <sub>C</sub> (mA) @<br>minimum<br>h <sub>FE</sub>                      | 3.14                           | 3.63                             | 3.66                                                 | 4.53                                                 | 4.70                             |

| I <sub>C</sub> (mA)<br>@ typical<br>h <sub>FE</sub>                      | 5.0                            | 5.0                              | 5.0                                                  | 5.0                                                  | 5.0                              |

| I <sub>C</sub> (mA) @<br>maximum<br>h <sub>FE</sub>                      | 9.27                           | 7.09                             | 6.98                                                 | 5.44                                                 | 5.27                             |

| Percentage<br>change in<br>I <sub>C</sub> from<br>nominal I <sub>C</sub> | +85%<br>-37%                   | +42%<br>-27%                     | +40%<br>-27%                                         | +9%<br>-9%                                           | +5.4%<br>-6%                     |

## **BJT Performance over Temperature**

Since all three temperature dependent variables (I<sub>CBO</sub>, h<sub>FE</sub>, and V'<sub>BE</sub>) exist in the I<sub>C</sub> equation, then differentiating the I<sub>C</sub> equation with respect to each of the parameters provides insight into their effect on I<sub>C</sub>. The partial derivative of each of the three parameters represents a stability factor. The various stability factors and their calculation are shown in Table 3. Each circuit then has three distinctly different stability factors which are then multiplied times a corresponding change in either V' BE, hFE, or I<sub>CBO</sub> and then summed. These changes or deltas in V' BE, hFE, and I<sub>CBO</sub> are calculated based on variations in these parameters due to manufacturing processes.

A comparison of each circuit's stability factors will certainly provide insight as to which circuit compensates best for each parameter. MATHCAD was again pushed into service to calculate the partial derivatives for each desired stability factor. The stability factors for each circuit are shown in Table 4.

The change in collector current from the nominal design value at 25°C is then calculated by taking each stability factor and multiplying it times the corresponding change in each parameter. Each product is then summed to determine the absolute change in collector current.

As an example, the collector current of the HBFP-0405 will be analyzed as temperature is increased from +25°C to +65°C. For the HBFP-0405, I<sub>CBO</sub> is typically 100 nA @ +25°C and typically doubles for every 10°C temperature rise. Therefore, I<sub>CBO</sub> will increase from 100 nA to 1600 nA at +65°C. The difference or  $\Delta$  I<sub>CBO</sub> will be 1600 - 100 = 1500 nA. The 1500 nA will then be multiplied times its corresponding I<sub>CBO</sub> Stability factor.

V'  $_{BE}$  @ 25°C was measured at 0.755 V for the HBFP-0405. Since V'  $_{BE}$  has a typical negative temperature coefficient of -2 mV /°C, V' $_{BE}$  will be 0.675 V @ +65°C. The difference in V'  $_{BE}$  will then be 0.675 - 0.755 = -0.08 V. The -0.08 V will then be multiplied times its corresponding V'  $_{BE}$  stability factor.

h<sub>FE</sub> is typically 80 @ +25°C and typically increases at a rate of 0.5% / °C. Therefore, h<sub>FE</sub> will increase from 80 to 96 @ +65°C making  $\Delta$  h<sub>FE</sub> equal to 96 - 80 = 16. Again the  $\Delta$  is multiplied times its corresponding stability factor.

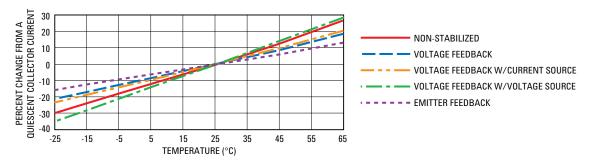

Once all stability terms are known, they can be summed to give the resultant change in collector current from the nominal value at +25°C. The results of the stability analysis are shown in Table 5. The non-stabilized circuit #1 allows I<sub>C</sub> to increase about 27% while circuits 2 and 3 show a 19 to 20% increase in Ic. Somewhat surprising is the fact that circuit #4 shows a nearly 30% increase in Ic with temperature. In looking at the contribution of the individual stability factors for circuit #4, one finds that V'BE is the major contributor. This is probably due to the impedance of the R<sub>B1</sub> and R<sub>B2</sub> voltage divider working against V' BE. It is also interesting to note that both circuit #2 and #3 have very similar performance over temperature. Both offer a significant improvement over circuit #1 and #4. As expected, circuit #5 offers the best performance over temperature by nature of emitter feedback. Emitter feedback can be used effectively if the resistor can be adequately RF bypassed without producing stability problems.

Table 3. Calculation of the Stability Factors and their combined effect on I<sub>C</sub>

$$I_{CBO} = \frac{\partial I_{C}}{\partial I_{CBO}} \quad h_{FE}, V'_{BE} = constant$$

$$V'_{BE} = \frac{\partial I_{C}}{\partial V'_{BE}} \quad I_{CBO}, h_{FE} = constant$$

$$h_{FE} = \frac{\partial I_{C}}{\partial h_{FE}} \quad I_{CBO}, V'_{BE} = constant$$

$\Delta I_C = SI_{CBO} \cdot \Delta I_{CBO} + SV'_{BE} \cdot \Delta V'_{BE} + Sh_{FE} \cdot \Delta h_{FE}$

First calculate the stability factors for V'BE, ICBO, and hFE.

Then, to find the change in collector current at any temperature, multiply the change from 25 C of each temperature dependent variable with its corresponding stability factor and sum.

The degree of control that each bias circuit has on controlling  $I_C$  due to  $h_{FE}$  variations and the intrinsic temperature dependent parameters has a lot to due with how the bias circuit is designed. Increasing the voltage differential between  $V_{CE}$  and  $V_{CC}$  can enhance the circuits' ability to control  $I_C$ . In handset applications, this becomes difficult with 3 volt batteries as power sources. The current that is allowed to flow through the various bias resistors can also have a major effect on  $I_C$  control.

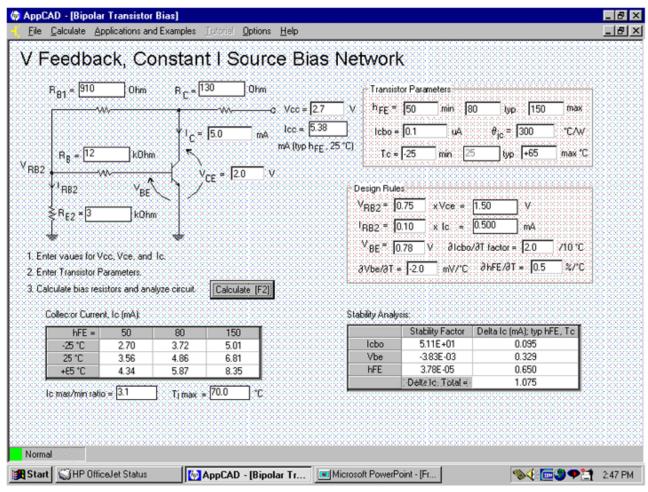

In order to analyze the various configurations, an AppCAD module was generated. AppCAD was created by Bob Myers of the Avago Technologies WSD Applications Department and is available free of charge via Avago Technologies' web site. AppCAD consists of various modules developed to help the RF designer with microstrip, stripline, detector, PIN diode, MMIC biasing, RF amplifier, transistor biasing and system level calculations, just to name a few. The AppCAD BJT biasing module allows the designer to fine tune each bias circuit design for optimum performance. AppCAD also allows the designer to input device variation parameters peculiar to a certain manufacturer's semiconductor process. A sample screen showing a typical bias circuit is shown in Figure 8. The data from AppCAD is used to create the graphs in the following sections.

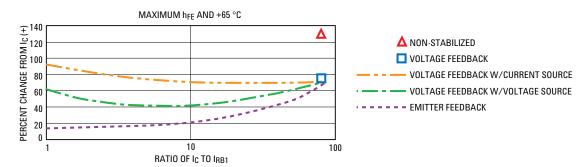

The first exercise is to graphically show the percentage change in  $I_C$  versus  $h_{FE}$ . AppCAD is used to calculate the resistor values for each of the five bias networks. The HBFP-0405 transistor is biased at a  $V_{CE}$  of 2 V,  $I_C$  of 5 mA, and  $V_{CC}$  of 2.7 V. Various values of  $h_{FE}$  are substituted into AppCAD. The results are shown in Figure 9. The data clearly shows that the Emitter Feedback and Voltage Feedback with Voltage Source networks are superior to the remaining circuits with regards to controlling  $h_{FE}$  at room temperature. These networks provide a 4:1 improvement over the other two Voltage Feedback networks.

AppCAD is then used to simulate a temperature change from  $T_J = -25^{\circ}C$  to  $+65^{\circ}C$  holding  $h_{FE}$  constant. Whereas the original Matchcad analysis assumed that  $T_C = T_J$ , AppCAD takes into account that T<sub>J</sub> is greater than T<sub>C</sub>. AppCAD calculates the thermal rise based on dc power dissipated and the thermal impedance of the device. The results of the analysis are shown in Figure 10. Somewhat surprising was the fact that the Voltage Feedback with Voltage Source network performed nearly as poorly as the non-stabilized circuit. This is due to VBE decreasing with temperature and the bias circuit trying to keep V<sub>BE</sub> constant. This is why power bipolar designers will utilize a silicon diode in place of R<sub>B2</sub> so that the bias voltage will track the V<sub>BE</sub> of the transistor. Depending on the impedance of the voltage divider network, VBE could actually rise causing IC to increase. The Emitter Feedback network performed very well as expected. The simple Voltage Feedback network appeared to be optimum when one considers the simplicity of the circuit.

Bias networks 3 through 5 make use of an additional resistor that shunts some of the total power supply current to ground. Properly chosen, this additional bias current can be used to assist in controlling  $I_C$  over temperature and  $I_F$  variations from device to device. AppCAD is set up such that the designer can make a few decisions regarding the amount of bias resistor current that is allowed to flow from the power supply. AppCAD is again used to analyze each bias circuit.

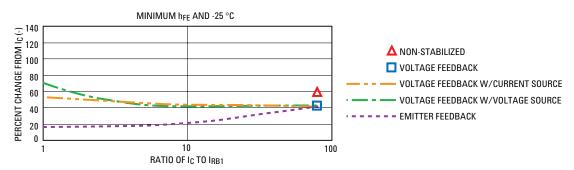

The graphs in Figures 11 and 12 plot the percentage change in  $I_C$  versus the ratio of  $I_C$  to  $I_{RB1}$ .  $I_{RB1}$  is the current flowing through resistor RB1 which is the summation of base current  $I_B$  and current flowing through resistor RB2. The maximum permissible ratio of  $I_C$  to  $I_{RB1}$  is limited by the  $h_{FE}$  of the transistor. Figure 11 represents the worst case condition where  $I_C$  increases at maximum  $h_{FE}$  and highest temperature. Figure 12 shows the opposite scenario where lowest  $I_C$  results from lowest  $h_{FE}$  and lowest temperature. The percentage change is certainly more pronounced at high  $h_{FE}$  and high temperature.

Figure 8. Avago Technologies' AppCAD module for BJT Biasing

Figure 9. Percent Change in Quiescent Collector Current vs. h<sub>FE</sub> for the HBFP-0405

$$V_{CC}$$

= 2.7 V,  $V_{CE}$  = 2 V,  $I_C$  = 5 mA,  $T_J$  = +25°C

Figure 10. Percent Change in Quiescent Collector Current vs. Temperature for the HBFP-0405

$V_{CC} = 2.7 \text{ V}, V_{CE} = 2 \text{ V}, I_{C} = 5 \text{ mA}, T_{J} = +25 ^{\circ}\text{C}$

Figure 11. Percent Change in Quiescent Collector Current vs. Ratio of  $I_C$  to  $I_{RB1}$  for Maximum  $h_{FE}$  and  $+65^{\circ}C$  for the HBFP-0405  $V_{CC}=2.7$  V,  $V_{CE}=2$  V,  $I_C=5$  mA,  $T_J=+25^{\circ}C$

Figure 12. Percent Change in Quiescent Collector Current vs. Ratio of  $I_C$  to  $I_{RB1}$  for Minimum  $h_{FE}$  and  $T_J = -25$ °C for the HBFP-0405  $V_{CC} = 2.7 \text{ V}, V_{CE} = 2 \text{ V}, I_C = 5 \text{ mA}$

Table 4.

## Stability Factors for Non-stabilized Bias Network #1

Collector current at any temperature (I<sub>C</sub>)

$$\frac{h_{FE} \bullet (V_{CC} \cdot V'_{BE})}{(h_{ie} + R_B)} + I_{CB0} \bullet (1 + h_{FE})$$

$$I_{CB0} \text{ Stability factor} \\ I_{CB0} = \frac{\partial I_{C}}{\partial I_{CB0}} \mid h_{FE}, V'_{BE} = \text{Constant}$$

$$V'_{BE} \text{ Stability factor} \\ V'_{BE} = \frac{\partial I_{C}}{\partial V'_{BE}} \mid I_{CB0}, h_{FE} = \text{Constant}$$

$$h_{FE} \text{ Stability factor} \\ h_{FE} \text{ Stability factor} \\ h_{FE} \text{ Stability factor}$$

$$h_{FE} \text{ Stability factor} \\ h_{FE} \text{ Stability factor}$$

$$h_{FE} \text{ Stability factor}$$

Table 4.

Stability Factors for Voltage Feedback Bias Network #2

| Collector current at any temperature (I <sub>C</sub> )                             | $h_{FE} \bullet (V_{CC} - V'_{BE}) + I_{CBO} \bullet (1 + h_{FE}) \bullet A$              |  |  |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|

|                                                                                    | $h_{ie} + R_B + R_C \bullet (1 + h_{FE})$                                                 |  |  |

| I <sub>CBO</sub> Stability factor                                                  | (1 + h <sub>FE</sub> ) • A                                                                |  |  |

| $I_{CBO} = \frac{\partial I_{CBO}}{\partial I_{CBO}}   h_{FE}, V'_{BE} = constant$ | $\overline{h_{ie} + R_B + R_C \bullet (1 + h_{FE})}$                                      |  |  |

| V' <sub>BE</sub> Stability factor                                                  | -h <sub>FE</sub>                                                                          |  |  |

| $V'_{BE} = \frac{\partial I_{C}}{\partial V'_{BE}}   _{CBO}, h_{FE} = constant$    | $h_{ie} + R_B + R_C \bullet (1 + h_{FE})$                                                 |  |  |

| h <sub>FE</sub> Stability factor                                                   | V <sub>CC</sub> - V' <sub>BE</sub> + A • I <sub>CBO</sub>                                 |  |  |

| $h_{FE} = \frac{\partial I_C}{\partial h_{EE}}  _{CBO}, V'_{BE} = constant$        | $\frac{1}{h_{FE} \bullet R_C + R_B + h_{ie} + R_C}$                                       |  |  |

| ,  dh <sup>E</sup> E                                                               | $R_{C} \bullet h_{FE} \bullet (V_{CC} - V'_{BE} + A \bullet I_{CBO}) + A \bullet I_{CBO}$ |  |  |

|                                                                                    | $(h_{FE} \bullet R_C + R_B + h_{ie} + R_C)^2$                                             |  |  |

|                                                                                    | Where:                                                                                    |  |  |

|                                                                                    | $A = h_{ie} + R_B + R_C$                                                                  |  |  |

Table 4.

Stability Factors for Voltage Feedback with Current Source Bias Network #3

Collector current at any temperature (I<sub>C</sub>)

$$h_{FE} \left[ \frac{V'_{BE} \bullet A - R_{B2} \bullet [R_{C} \bullet I_{CB0} \bullet (1 + h_{FE}) - V_{CC}]}{(R_{B} + h_{ie}) \bullet A + R_{B2} \bullet (h_{FE} \bullet R_{C} + R_{C} + R_{B1})} \right] + I_{CB0} \bullet (1 + h_{FE})$$

$$I_{CBO} = \frac{\partial I_C}{\partial I_{CBO}} | h_{FE}, V'_{BE} = constant$$

$$(1+h_{FE}) \cdot \frac{R_{B2} \bullet h_{FE} \bullet R_{C} \bullet (1+h_{FE})}{A \bullet (R_{B}+h_{ie}) + R_{B2} \bullet (h_{FE} \bullet R_{C}+R_{C}+R_{B1})}$$

V'BE Stability factor

$$V'_{BE} = \frac{\partial I_{C}}{\partial V'_{BE}} \mid_{CB0}, h_{FE} = constant$$

$$\frac{-h_{FE} \bullet A}{(R_B + h_{ie}) \bullet A + R_{B2} \bullet (h_{FE} \bullet R_C + R_C + R_{B1})}$$

h<sub>FE</sub> Stability factor

$$h_{FE} = \frac{\partial I_C}{\partial h_{FE}} \mid_{CBO}, V'_{BE} = constant$$

$$\frac{h_{FE} \bullet \left\{R_{B2} \bullet R_{C} \bullet \left[ \left(-R_{B2} \bullet V_{CC} + B\right) + R_{B2} \bullet R_{C} \bullet I_{CBO} \bullet \left(1 + h_{FE}\right) \right] \right\}}{D^{2}}$$

$$\frac{\left[B + R_{B2} \bullet \left[R_{C} \bullet I_{CBO} \bullet \left(1 + h_{FE}\right) \cdot V_{CC} + h_{FE} \bullet R_{C} \bullet I_{CBO}\right]\right]}{D} + I_{CBO}$$

Where:

$$A = R_{B1} + R_{B2} + R_{C}$$

$$B = V'_{BE} \bullet (R_{B1} + R_{B2} + R_{C})$$

$$C = (R_B + h_{ie}) \bullet (R_{B1} + R_{B2} + R_C)$$

$$D = (R_B + h_{ie}) \bullet (R_{B1} + R_{B2} + R_C) + R_{B2} \bullet (h_{FE} \bullet R_C + R_C + R_{B1})$$

## Table 4.

## Stability Factors for Voltage Feedback with Voltage Source Bias Network #4

Collector current at any temperature (I<sub>C</sub>)

$$\frac{I_{CB0} \bullet (-A) + I_{CB0} \bullet h_{ie} \bullet (-B) + D - V_{CC}}{C}$$

I<sub>CBO</sub> Stability factor

$$I_{CBO} = \frac{\partial I_{C}}{\partial I_{CBO}} \mid_{h_{FE}}, V'_{BE} = constant$$

$$\frac{\mathsf{h}_{\mathsf{ie}} \bullet \mathsf{B} + \mathsf{A}}{\mathsf{C}}$$

V'BE Stability factor

$$V'_{BE} = \frac{\partial I_{C}}{\partial V'_{BE}} \mid_{I_{CBO}}, h_{FE} = constant$$

$$\frac{-R_{C}}{R_{B2}} - \frac{R_{B1}}{R_{B2}} - 1$$

h<sub>FE</sub> Stability factor

$$h_{FE} = \frac{\partial I_{C}}{\partial h_{FE}} \parallel_{CBO}, V'_{BE} = constant$$

$$\frac{I_{CB0} \bullet \left[ \frac{-R_C}{h_{FE}^2} - \frac{R_{B1}}{h_{FE}^2} \right] + I_{CB0} \bullet h_{ie} \bullet E}{C}$$

$$\frac{I_{CB0} \bullet A + I_{CB0} \bullet h_{ie} \bullet B - D + V_{CC}}{C^2} \bullet \left[ \frac{-R_C}{h_{FE}^2} - \frac{R_{B1}}{h_{FE}^2} + h_{ie} \bullet E \right]$$

Where

$$A = \frac{R_{C}}{h_{FE}} + R_{C} + \frac{R_{B1}}{h_{FE}} + R_{B1}$$

$$B = \frac{R_C}{R_{B2} \bullet h_{FE}} + \frac{R_C}{R_{B2}} + \frac{R_{B1}}{R_{B2} \bullet h_{FE}} + \frac{R_{B1}}{R_{B2}} + \frac{1}{h_{FE}} + 1$$

$$C = R_C + \frac{R_C}{h_{FE}} + \frac{R_{B1}}{h_{FE}} + h_{ie} \bullet \left[ \frac{R_C}{R_{B2} \bullet h_{FE}} + \frac{R_{B1}}{R_{B2} \bullet h_{FE}} + \frac{1}{h_{FE}} \right]$$

$$D = \frac{R_C}{R_{B2}} \bullet V'_{BE} + \frac{R_{B1}}{R_{B2}} \bullet V'_{BE} + V'_{BE}$$

$$E = \frac{-R_C}{R_{B2} \bullet h_{FE}^2} - \frac{R_{B1}}{R_{B2} \bullet h_{FE}^2} - \frac{1}{h_{FE}^2}$$

Table 4.

## Stability Factors for Emitter Feedback Bias Network #5

Collector current at any temperature (I<sub>C</sub>)

$$\frac{\mathsf{h}_{\mathsf{ie}} \bullet \mathsf{I}_{\mathsf{CBO}} \bullet (\mathsf{-A}) + \mathsf{I}_{\mathsf{CBO}} \bullet (\mathsf{-B}) + \mathsf{D}}{\mathsf{C}}$$

I<sub>CBO</sub> Stability factor

$$I_{CBO} = \frac{\partial I_C}{\partial I_{CBO}} | h_{FE}, V'_{BE} = constant$$

V'<sub>BE</sub> Stability factor

$$V'_{BE} = \frac{\partial I_{C}}{\partial V'_{BE}} \mid_{CBO}, h_{FE} = constant$$

$$\frac{-1-\frac{R_1}{R_2}}{C}$$

h<sub>FE</sub> Stability factor

$$h_{FE} = \ \frac{\partial I_{C}}{\partial h_{FE}} \ \|_{CBO}, V'_{BE} = constant$$

$$\frac{I_{CBO} \bullet E + h_{ie} \bullet I_{CBO} \bullet \left[\frac{-1}{h_{FE}^2} - \frac{R_1}{R_2 \bullet h_{FE}^2}\right]}{C} - \frac{R_1}{R_2 \bullet R_1}$$

$$\frac{\mathsf{I}_{\mathsf{CB0}} \bullet \mathsf{B} + \mathsf{h}_{\mathsf{ie}} \bullet \mathsf{I}_{\mathsf{CB0}} \bullet \mathsf{A} - \mathsf{D}}{\mathsf{C}^2} \bullet \left[ \mathsf{h}_{\mathsf{ie}} \bullet \left( \frac{-1}{\mathsf{h}_{\mathsf{FE}}^2} - \frac{\mathsf{R}_1}{\mathsf{R}_2 \bullet \mathsf{h}_{\mathsf{FE}}^2} \right) + \mathsf{E} \right]$$

Where:

$$A = \frac{R_1}{R_2 \bullet h_{FE}} + \frac{R_1}{R_2} + \frac{1}{h_{FE}} + 1$$

$$B = \frac{R_1}{R_2} \cdot \frac{R_E}{h_{FE}} + \frac{R_1}{R_2} \bullet R_E + \frac{R_E}{h_{FE}} + R_E + \frac{R_1}{h_{FE}} + R_1$$

$$C = h_{ie} \bullet \left(\frac{1}{h_{FE}} + \frac{R_1}{R_2 \bullet h_{FE}}\right) + \frac{R_E}{h_{FE}} + R_E + \frac{R_1}{R_2} \bullet \frac{R_E}{h_{FE}} + \frac{R_1}{R_2} \bullet R_E + \frac{R_1}{h_{FE}}$$

$$D = V'_{BE} + \frac{R_1}{R_2} \bullet V'_{BE} - V_{CC}$$

$$E = \frac{-R_E}{h_{FE}^2} - \frac{R_1}{R_2} \bullet \frac{R_E}{h_{FE}^2} - \frac{R_1}{h_{FE}^2}$$

Table 5. Bias Stability Analysis at  $+65^{\circ}$ C using the HBFP-0405  $V_{CC}=2.7$  V,  $V_{CE}=2$  V,  $I_{C}=5$  mA

| Bias Circuit                                                       | #1 Non-<br>Stabilized      | #2 Voltage<br>Feedback     | #3 Voltage<br>Feedback<br>w/Current<br>Source | #4 Voltage<br>Feedback    | #5 Emitter<br>Feedback     |

|--------------------------------------------------------------------|----------------------------|----------------------------|-----------------------------------------------|---------------------------|----------------------------|

| I <sub>CBO</sub> Stability Factor                                  | 81                         | 52.238                     | 50.865                                        | 19.929                    | 11.286                     |

| V' BE Stability Factor                                             | -2.56653x 10 <sup>-3</sup> | -2.568011x10 <sup>-3</sup> | -3.956x10 <sup>-3</sup>                       | -0.015                    | -6.224378x10 <sup>-3</sup> |

| h <sub>FE</sub> Stability Factor                                   | 6.249877x10 <sup>-5</sup>  | 4.031x10 <sup>-5</sup>     | 3.924702x10 <sup>-5</sup>                     | 1.537669x10 <sup>-5</sup> | 8.707988x10 <sup>-6</sup>  |

| $\Delta$ I <sub>C</sub> due to I <sub>CBO</sub> (mA)               | 0.120                      | 0.078                      | 0.076                                         | 0.030                     | 0.017                      |

| $\Delta$ I <sub>C</sub> due to V' <sub>BE</sub> (mA)               | 0.210                      | 0.205                      | 0.316                                         | 1.200                     | 0.497                      |

| $\Delta$ I <sub>C</sub> due to h <sub>FE</sub> (mA)                | 0.999                      | 0.645                      | 0.628                                         | 0.246                     | 0.140                      |

| Total $\Delta$ I <sub>C</sub> (mA)                                 | 1.329                      | 0.928                      | 1.020                                         | 1.476                     | 0.654                      |

| Percentage change in<br>I <sub>C</sub> from nominal I <sub>C</sub> | 26.6%                      | 18.6%                      | 20.4%                                         | 29.5%                     | 13.1%                      |

Some of the actual predicted results are somewhat surprising. However, as expected, the bias network with emitter resistor feedback offers the best performance overall. For a ratio of  $I_C$  to  $I_{RB1}$  of 10 to 1 or less, the resultant change in collector current is less than 20%. The Voltage Feedback with Voltage Source network provides its best performance at an  $I_C$  to  $I_{RB1}$  ratio between 6 and 10 with a worst case change of 41% in collector current.

To complete the comparison, two additional points representing the Non-Stabilized and the Voltage Feedback networks have been added to the graphs. They are shown as single points because only the base current is in addition to the collector current. The Non-stabilized network has a +129% change while the Voltage Feedback network has an increase of 74.5%. It is also interesting to note that the Voltage Feedback with Current Source network really offers no benefit over the simpler Voltage Feedback network.

#### Conclusion

This paper has presented the circuit analysis of four commonly used stabilized bias networks and one non-stabilized bias network for the bipolar junction transistor. In addition to the presentation of the basic design equations for the bias resistors for each network, an equation was presented for collector current in terms of bias resistors and device parameters. The collector current equation was then differentiated with respect to the three primary temperature dependent variables resulting in three stability factors for each network. These stability factors plus the basic collector current equation give the designer insight as to how best bias any bipolar transistor for best performance over her and temperature variations. The basic equations were then integrated into an AppCAD module providing the circuit designer an easy and effective way to analyze bias networks for bipolar transistors.

#### References.

- 1. "A Cost-Effective Amplifier Design Approach at 425 MHz Using the HXTR-3101 Silicon Bipolar Transistor", Hewlett-Packard Application Note 980, 2/81 (out of print).

- 2. Richter, Kenneth. "Design DC Stability Into Your Transistor Circuits", Microwaves, December 1973, pp 40-46.

- 3. "Microwave Transistor Bias Considerations", Hewlett-Packard Application Note 944-1, 8/80, (out of print).

- 4. "1800 to 1900 MHz Amplifier using the HBFP-0405 and HBFP-0420 Low Noise Silicon Bipolar Transistors", Hewlett-Packard Application Note 1160, (11/98), publication number 5968-2387E.

For product information and a complete list of distributors, please go to our web site: **www.avagotech.com**