# MODEL 275 12 MHz PROGRAMMABLE ARBITRARY FUNCTION GENERATOR

## © 1984 Wavetek

THIS DOCUMENT CONTAINS INFORMATION PROPRIETARY TO WAVETEK AND IS SOLELY FOR INSTRUMENT OPERATION AND MAINTENANCE. THE INFORMATION IN THIS DOCUMENT MAY NOT BE DUPLICATED IN ANY MANNER WITHOUT THE PRIOR APPROVAL IN WRITING OF WAVETEK.

9045 Balboa Ave., San Diego, CA 92123 P. O. Box 85265, San Diego, CA 92138 Tel 619/279-2200 TWX 910/335-2007

## WARRANTY

Wavetek warrants that all products of its own manufacture conform to Wavetek specifications and are free from defects in material and workmanship when used under normal operating conditions and within the service conditions for which they were furnished.

The obligation of Wavetek hereunder shall expire one (1) year after delivery and is limited to repairing, or at its option, replacing without charge, any such product which in Wavetek's sole opinion proves to be defective within the scope of this Warranty. In the event Wavetek is not able to repair or replace defective products or components within a reasonable time after receipt thereof, Buyer shall be credited for their value at the original purchase price.

Wavetek must be notified in writing of the defect or nonconformity within the warranty period and the affected product returned to Wavetek's factory or to an authorized service center within thirty (30) days after discovery of such defect or nonconformity. Shipment shall not be made without prior authorization by Wavetek.

This is Wavetek's sole warranty with respect to the products delivered hereunder. No statement, representation, agreement or understanding, oral or written, made by an agent, distributor, representative or employee of Wavetek, which is not contained in this warranty, will be binding upon Wavetek, unless made in writing and executed by an authorized Wavetek employee. Wavetek makes no other warranty of any kind whatsoever, expressed or implied, and all implied warranties of merchantability and fitness for a particular use which exceed the aforestated obligation are hereby disclaimed by Wavetek and excluded from this agreement. Under no circumstances shall Wavetek be liable to Buyer, in contract or in tort, for any special, indirect, incidental or consequential damages, expenses, losses or delays however caused.

## **CONTENTS**

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 MODEL 275 1.2 ACCESSORIES 1.3. SPECIFICATIONS 1.3.1 Main Generator Waveforms (Functions) 1.3.2 Operational Modes (For All Functions Including ARB) 1.3.3 Operational Modes (ARB Only) 1.3.4 Frequency 1.3.5 Amplitude 1.3.6 Offset 1.3.7 Outputs 1.3.8 Inputs 1.3.9 Internal Trigger 1.3.10 ARB Characteristics 1.3.11 GPIB Programming 1.3.12 General 1.3.13 Options 1.3.14 Accessories | 1-1<br>1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4<br>1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| INSTALLATION AND INTERFACE                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.1 MECHANICAL INSTALLATION 2.2 ELECTRICAL INSTALLATION 2.2.1 Power Connection 2.2.2 Signal Connection 2.2.3 GPIB Connections 2.2.4 GPIB Address 2.2.5 Initial Checkout and Operation Verification                                                                                                                                                                                           | 2-1<br>2-1<br>2-1<br>2-2<br>2-2<br>2-2<br>2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OPERATION                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.2 Parameter Keys                                                                                                                                                                                                                                                                                                                                                                         | 3-1<br>3-1<br>3-7<br>3-7<br>3-7<br>3-7<br>3-8<br>3-8<br>3-9<br>3-9<br>3-9<br>3-10<br>3-10<br>3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                              | 1.1 MODEL 275 1.2 ACCESSORIES 1.3 SPECIFICATIONS 1.3.1 Main Generator Waveforms (Functions) 1.3.2 Operational Modes (For All Functions Including ARB) 1.3.3 Operational Modes (ARB Only) 1.3.4 Frequency 1.3.5 Amplitude 1.3.6 Offset 1.3.7 Outputs 1.3.8 Inputs 1.3.9 Internal Trigger 1.3.10 ARB Characteristics 1.3.11 GPIB Programming 1.3.12 General 1.3.13 Options 1.3.14 Accessories  INSTALLATION AND INTERFACE  2.1 MECHANICAL INSTALLATION 2.2 ELECTRICAL INSTALLATION 2.2.1 Power Connection 2.2.2 Signal Connection 2.2.2 GPIB Address 2.2.5 Initial Checkout and Operation Verification  OPERATION  3.1 INTRODUCTION TO OPERATION 3.2 FRONT PANEL CONTROLS AND CONNECTORS 3.3 POWER UP 3.4 LOCAL OPERATION 3.4.1 Action Keys 3.4.1.1 Tone Key 3.4.1.2 Status Key 3.4.1.1 Tone Key 3.4.1.5 Execute Key 3.4.1.5 Execute Key 3.4.1.6 Clear Entry Key 3.4.1.7 Local Key 3.4.1.8 SPQ Key 3.4.1.9 Command Recall Key 3.4.1.9 Command Recall Key 3.4.1.10 Arb Monitor Key 3.4.1.10 Command Recall Key 3.4.1.10 Command Recall Key 3.4.1.10 Command Recall Key 3.4.1.2 Command Recall Key 3.4.1.3 Cursor Keys |

| 3.4.2.1.3 Offset Key                                   |      |

|--------------------------------------------------------|------|

| 3.4.2.1.4 Burst Key                                    |      |

| 3.4.2.1.5 Function Key                                 |      |

| 3.4.2.1.6 Mode Key                                     |      |

| 3.4.2.2 Trigger Controls                               |      |

| 3.4.2.2.1 Internal/External Key                        |      |

| 3.4.2.2.2 Rate Key                                     |      |

| 3.4.2.2.3 Level Key                                    |      |

| 3.4.2.2.4 Slope Key                                    |      |

| 3.4.2.3 Arbitrary Waveform Controls                    |      |

| 3.4.2.3.1 Address Key                                  |      |

| 3.4.2.3.2 Data Key                                     |      |

| 3.4.2.3.3 Auto Line Key                                |      |

| 3.4.2.3.4 Start/Stop Key                               |      |

|                                                        |      |

| 3.4.2.4.1 Store Key                                    |      |

| 3.4.2.4.3 Output Control                               |      |

| 3.4.2.4.4 GPIB Controls                                |      |

| 3.4.3 Numeric Keys.                                    |      |

| 3.4.3.1 Parameter Termination and Execution            |      |

| 3.4.3.2 Errors                                         |      |

| 3.4.4 Parameter Entry                                  |      |

| 3.4.5 Arbitrary Waveform Controls                      |      |

| 3.4.5.1 Waveform Entry with AUTO LINE Key              |      |

| 3.4.5.2 Point-by-Point Waveform Entry                  |      |

| 3.4.5.3 Multiple Arbitrary Waveform                    |      |

| 3.4.5.4 Checking and Monitoring Arbitrary Waveform     |      |

| 3.4.6 Stored Settings                                  |      |

| 3.4.6.1 Storage of Setting                             |      |

| 3.4.6.2 Deletion of Stored Settings                    |      |

| 3.4.6.3 Recall of Stored Setting                       |      |

| 3.4.6.4 Modification of Stored Setting                 |      |

| 3.4.6.5 Recall of Consecutive Stored Settings          |      |

| 3.4.6.6 Recall of Last Power Off Condition             |      |

| 3.4.6.7 Stored Performance Verification                | 3-25 |

| 3.4.6.8 Calibration Procedure                          | 3-26 |

| 3.4.6.9 Front Panel Lockout                            | 3-26 |

| 3.4.6.10 Arbitrary Waveform Sync Polarity              | 3-26 |

| 3.4.6.11 Ramp-to-Start Rate                            | 3-27 |

| 3.4.7 VCG Operation                                    |      |

| 3.5 REMOTE OPERATION                                   |      |

| 3.5.1 ASCII Control Codes                              |      |

| 3.5.2 Setting Instrument GET, SRQ and Talk Modes       |      |

| 3.5.2.1 Setting the Talk Mode                          |      |

| 3.5.2.2 Setting the SRQ Mode                           |      |

| 3.5.2.3 Setting the GET Mode                           |      |

| 3.5.3 Setting the End of String (Terminator) Character |      |

| 3.5.4 Remote Control of Instrument Display             |      |

| 3.5.5 Differences Between Controllers                  |      |

| 3.5.6 Sending Instrument Commands                      | 3-31 |

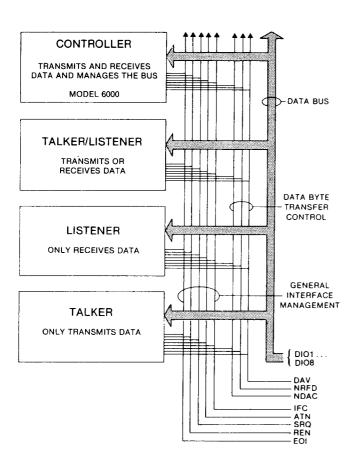

|           | 3.5.7 Reading Instrument Responses 3.5.7.1 Talk Command 3.5.7.2 Serial Poll 3.5.8 SRQ Interrupts 3.5.9 Sample Demonstration Programs 3.6 THE GENERAL PURPOSE INTERFACE BUS 3.6.1 GPIB Structure 3.6.2 GPIB Lines 3.6.3 Handshake Sequence 3.6.4 GPIB Commands 3.6.4.1 Listen Addresses 3.6.4.2 Talk Addresses 3.6.4.3 Secondary Addresses 3.6.4.4 Universal Commands 3.6.4.5 Addressed Commands 3.6.5 Using the GPIB | 3-32<br>3-32<br>3-32<br>3-43<br>3-43<br>3-45<br>3-45<br>3-45<br>3-46<br>3-46 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

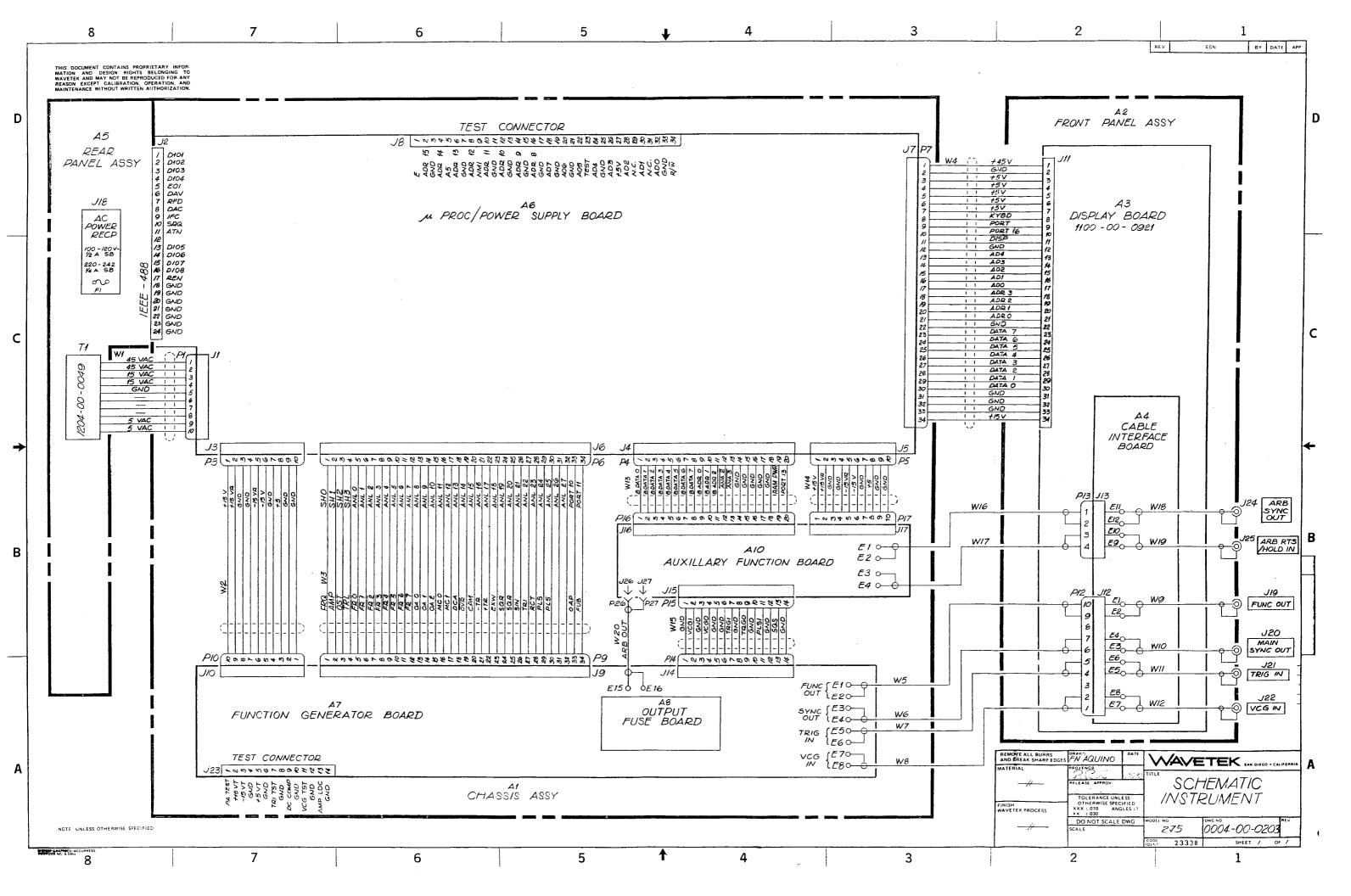

| SECTION 4 | CIRCUIT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |

|           | 4.1 GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                              | 4-1                                                                          |

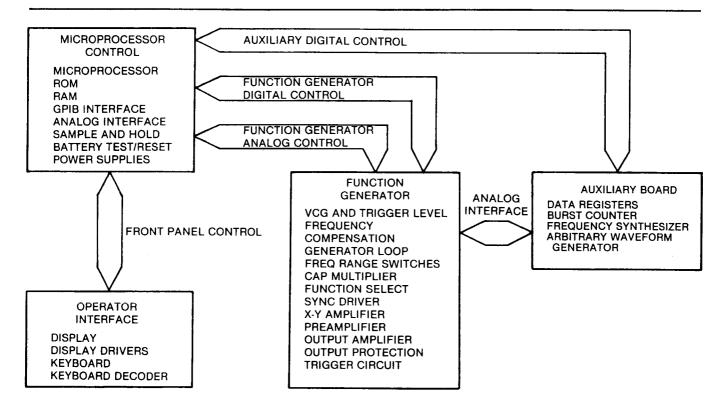

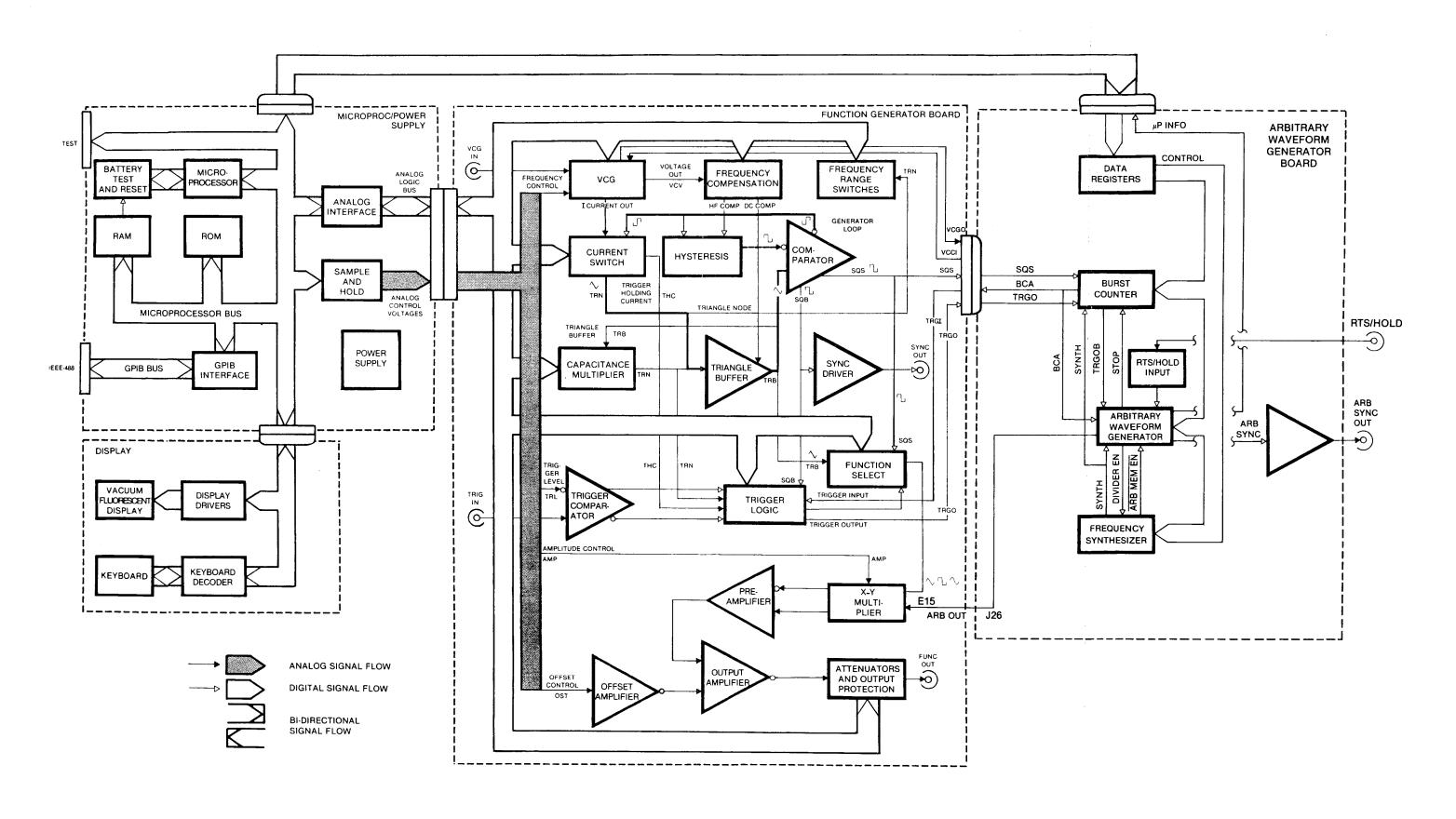

|           | 4.1.1 Microprocessor Control                                                                                                                                                                                                                                                                                                                                                                                         | 4-1                                                                          |

|           | 4.1.2 Operator Interface                                                                                                                                                                                                                                                                                                                                                                                             | 4-1                                                                          |

|           | 4.1.3 Function Generator                                                                                                                                                                                                                                                                                                                                                                                             | 4-2                                                                          |

|           | 4.1.4 Auxiliary Board                                                                                                                                                                                                                                                                                                                                                                                                | 4-2                                                                          |

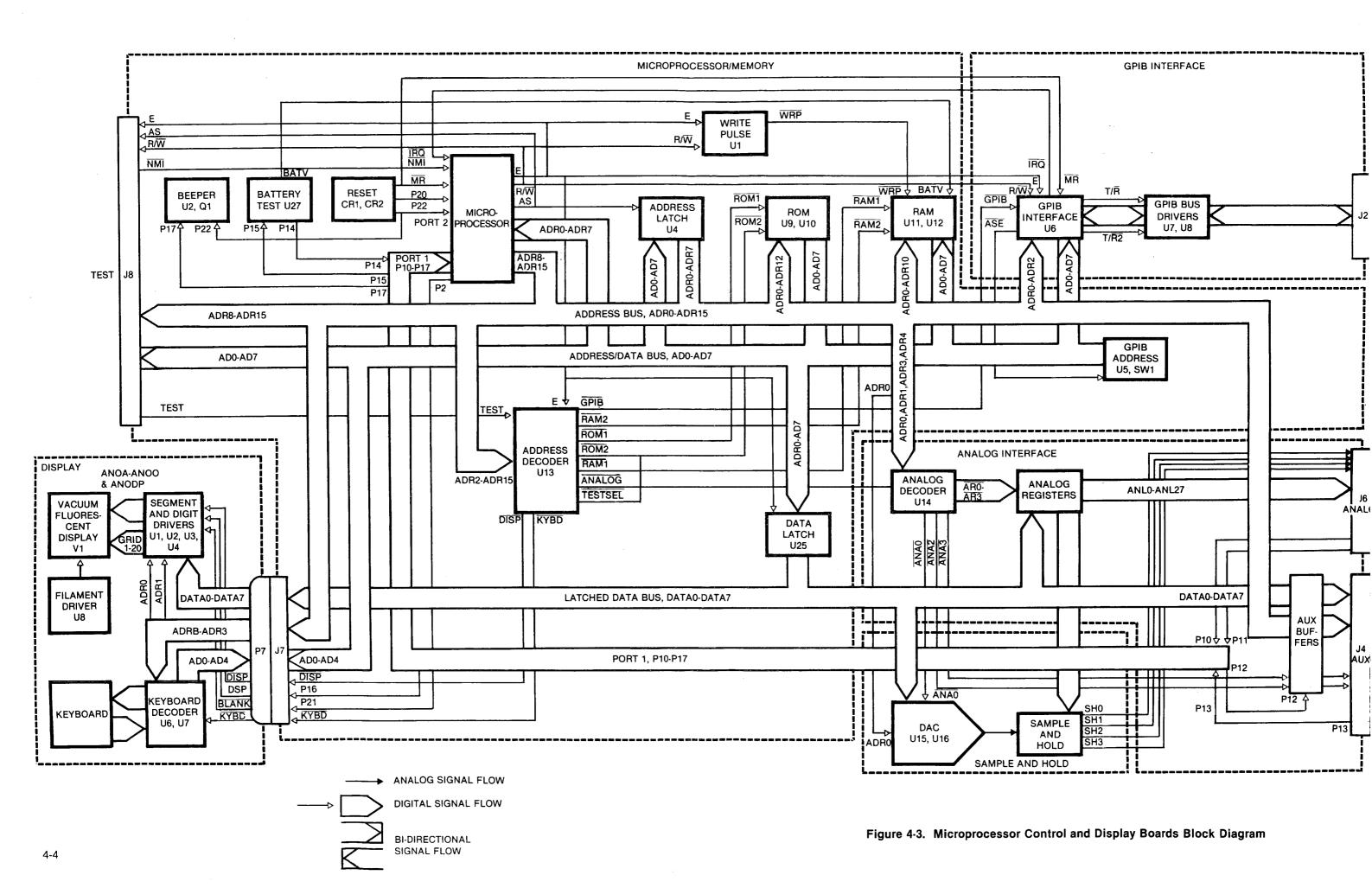

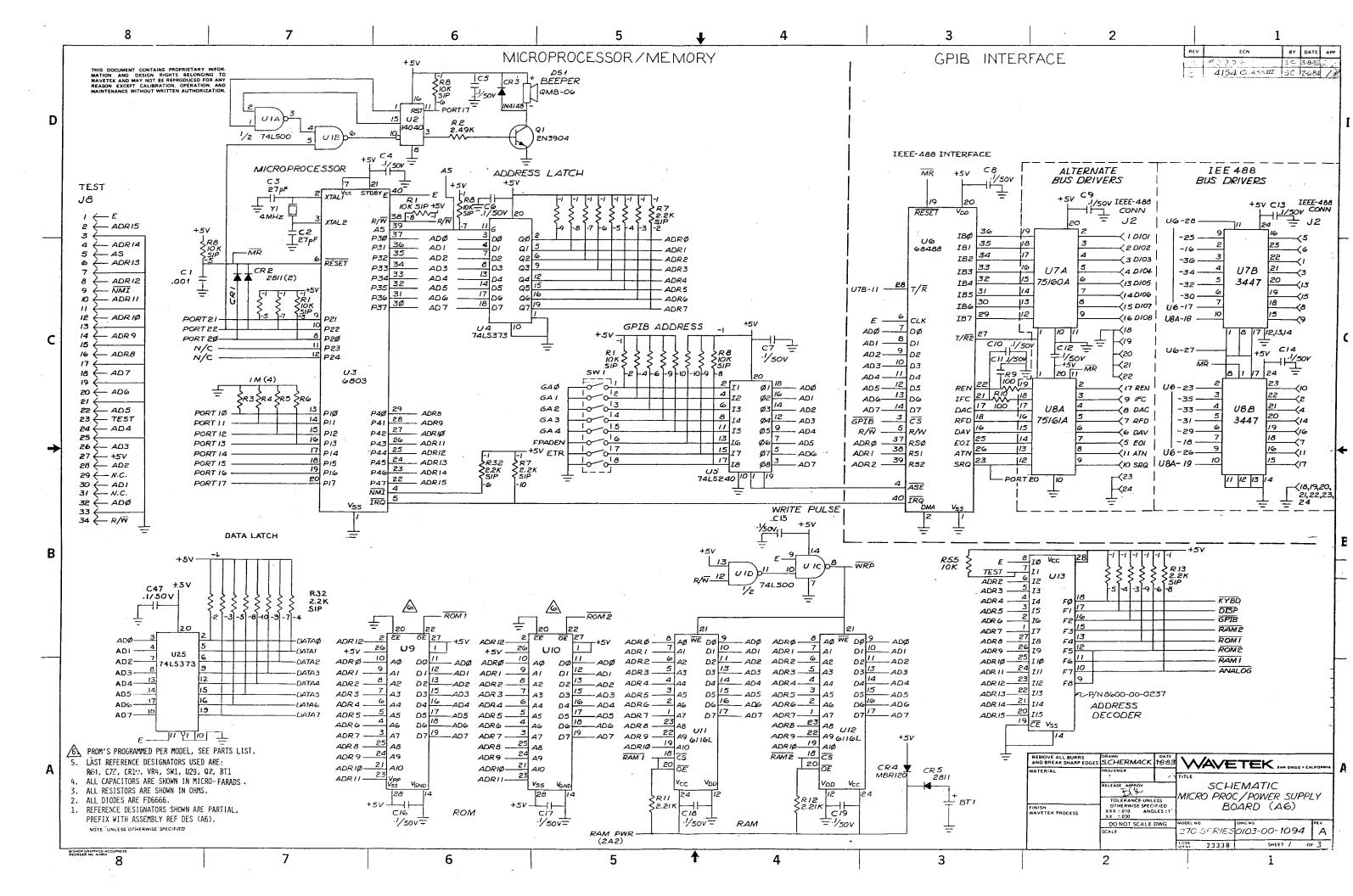

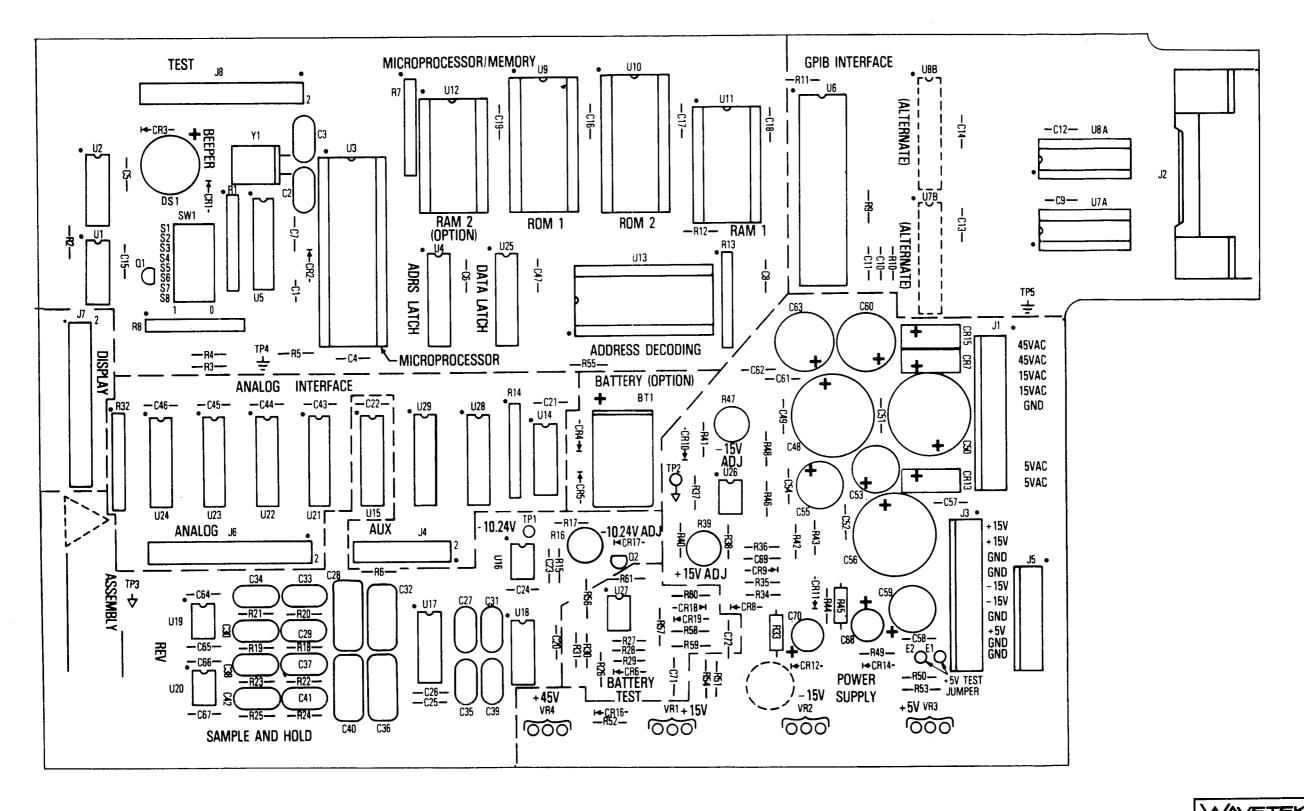

|           | 4.2 MICROPROCESSOR CONTROL CIRCUIT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                       | 4-2                                                                          |

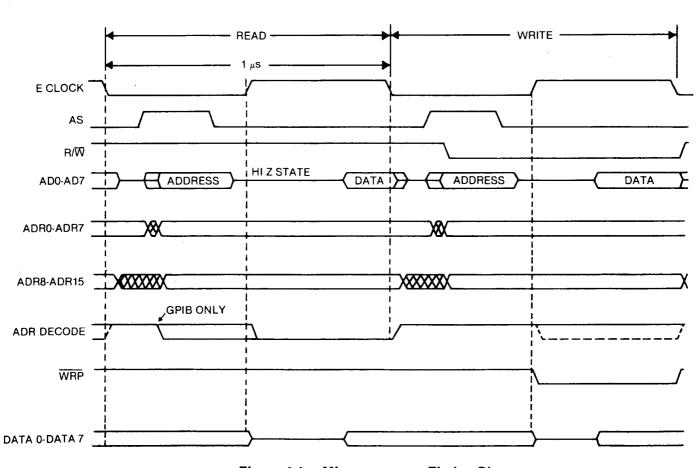

|           | 4.2.1 Microprocessor/Memory                                                                                                                                                                                                                                                                                                                                                                                          | 4-2                                                                          |

|           | 4.2.1.1 Microprocessor                                                                                                                                                                                                                                                                                                                                                                                               | 4-5                                                                          |

|           | 4.2.1.2 Address Latch                                                                                                                                                                                                                                                                                                                                                                                                | 4-5                                                                          |

|           | 4.2.1.3 Data Latch                                                                                                                                                                                                                                                                                                                                                                                                   | 4-5                                                                          |

|           | 4.2.1.4 Address Decoder                                                                                                                                                                                                                                                                                                                                                                                              | 4-6                                                                          |

|           | 4.2.1.5 ROM                                                                                                                                                                                                                                                                                                                                                                                                          | 4-6                                                                          |

|           | 4.2.1.6 RAM                                                                                                                                                                                                                                                                                                                                                                                                          | 4-6                                                                          |

|           | 4.2.1.7 Beeper                                                                                                                                                                                                                                                                                                                                                                                                       | 4-6                                                                          |

|           | 4.2.1.8 GPIB Address                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                              |

|           | 4.2.2 GPIB Interface                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                              |

|           | 4.2.3 Battery Test and Reset                                                                                                                                                                                                                                                                                                                                                                                         |                                                                              |

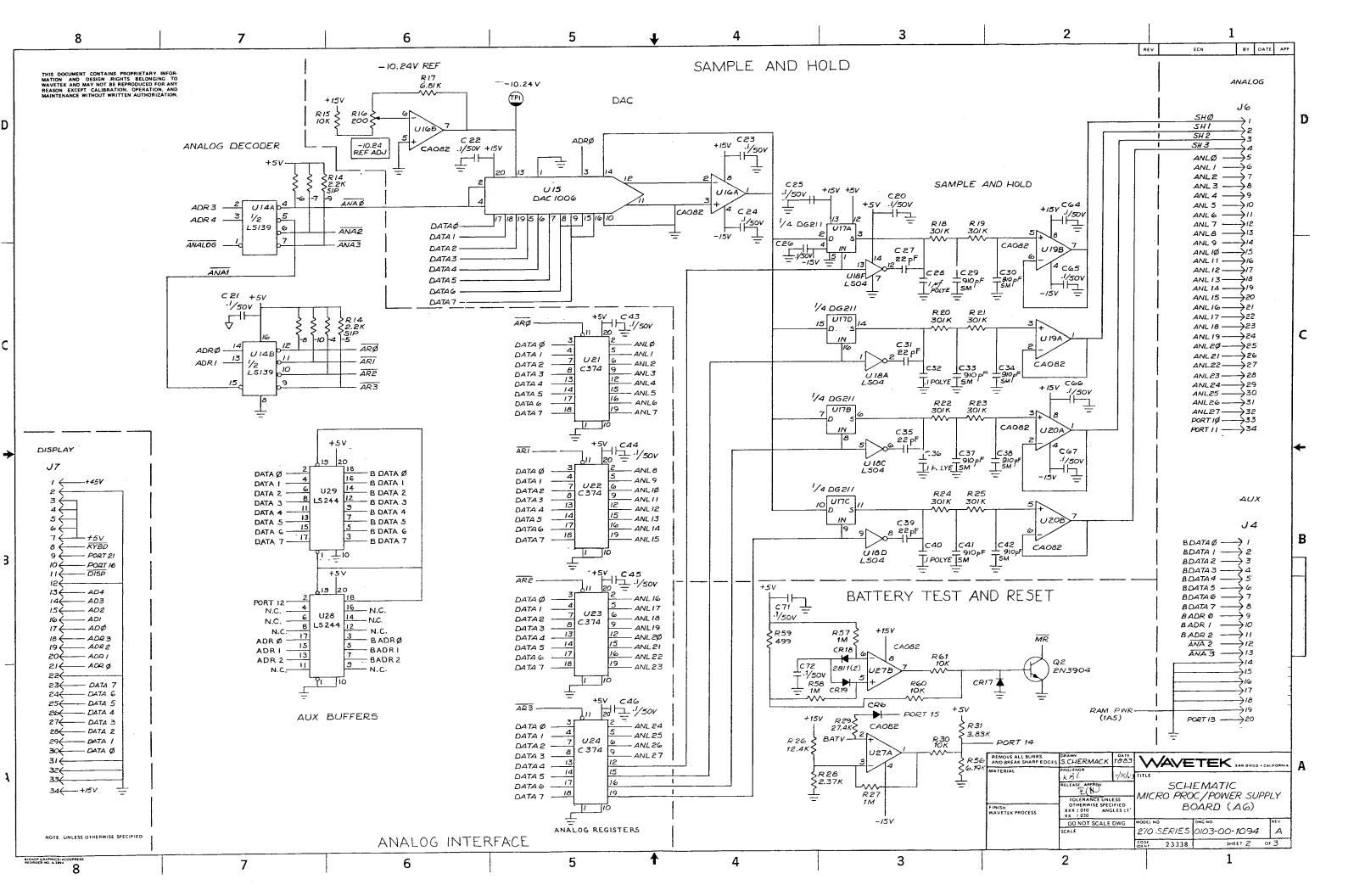

|           | 4.2.4 Analog Interface                                                                                                                                                                                                                                                                                                                                                                                               | 4-8<br>4-8                                                                   |

|           | 4.2.4.2 Analog Registers                                                                                                                                                                                                                                                                                                                                                                                             | 4-8                                                                          |

|           | 4.2.5 Sample and Hold                                                                                                                                                                                                                                                                                                                                                                                                | 4-8                                                                          |

|           | 4.2.5.1 DAC                                                                                                                                                                                                                                                                                                                                                                                                          | 4-8                                                                          |

|           | 4.2.5.2 -10,24V Reference                                                                                                                                                                                                                                                                                                                                                                                            | 4-8                                                                          |

|           | 4.2.5.3 Sample and Hold.                                                                                                                                                                                                                                                                                                                                                                                             | 4-8                                                                          |

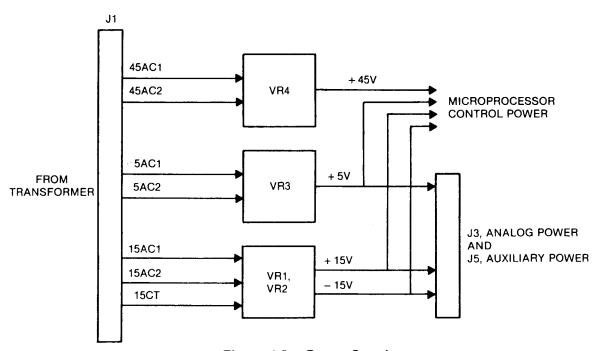

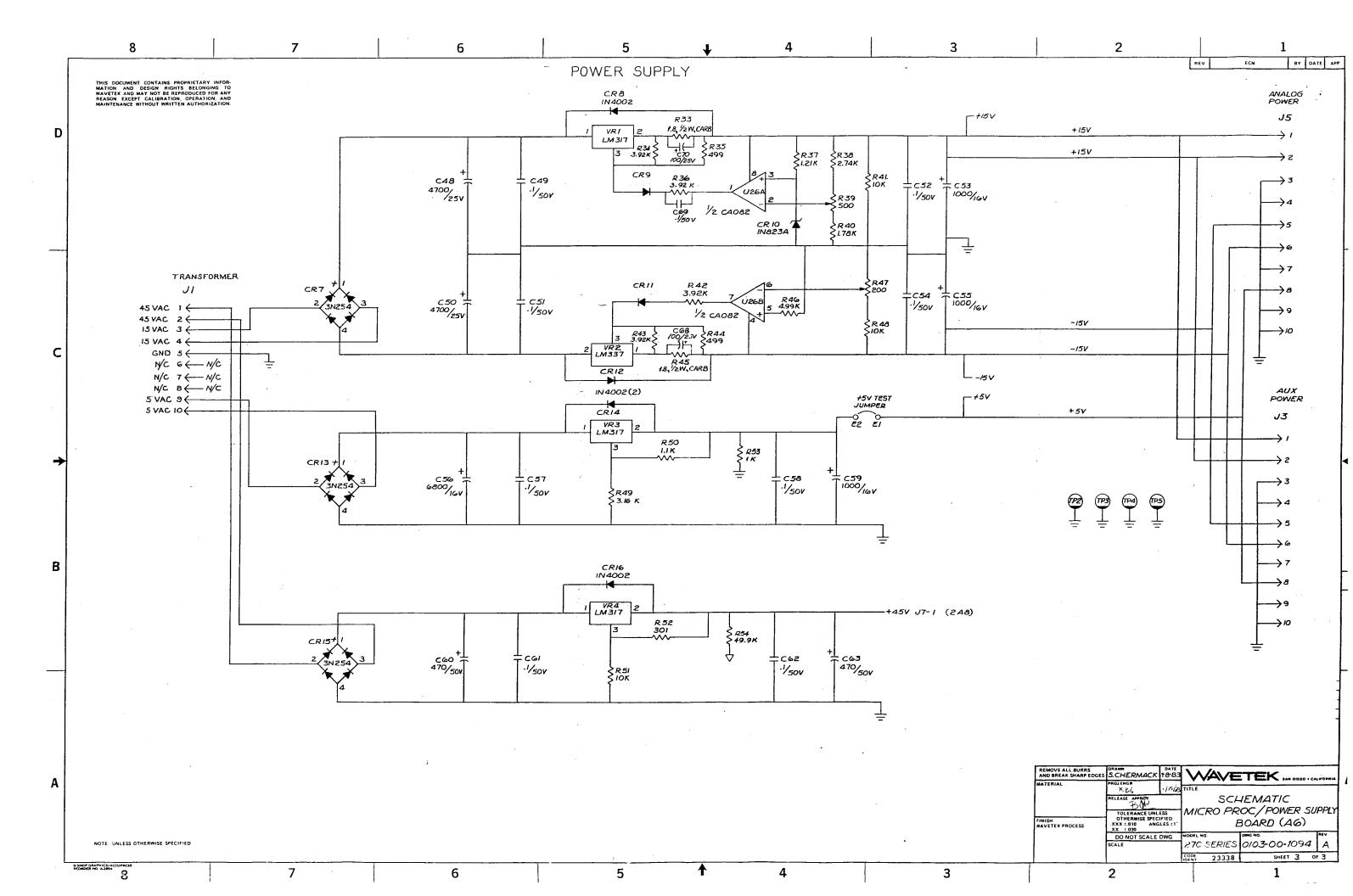

|           | 4.2.6 Power Supply                                                                                                                                                                                                                                                                                                                                                                                                   | 4-9                                                                          |

|           | 4.2.6.1 + 5V Supply                                                                                                                                                                                                                                                                                                                                                                                                  | 4-9                                                                          |

|           | 4.2.6.2 + 45V Supply                                                                                                                                                                                                                                                                                                                                                                                                 | 4-9                                                                          |

|           | 4.2.6.3 ±15V Supplies                                                                                                                                                                                                                                                                                                                                                                                                | 4-9                                                                          |

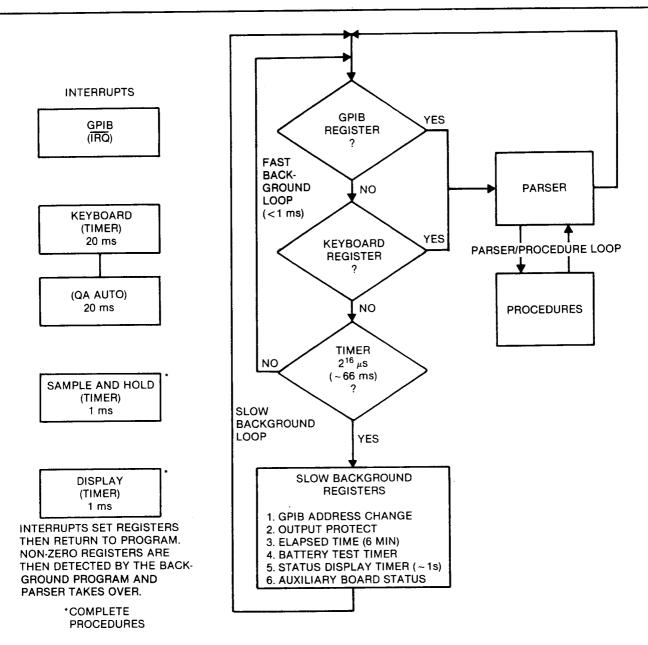

|           | 4.2.7 Microprocessor Software                                                                                                                                                                                                                                                                                                                                                                                        | 4-10                                                                         |

|           | 4.2.7.1 Fast Background                                                                                                                                                                                                                                                                                                                                                                                              |                                                                              |

|           | 4.2.7.2 Slow Background                                                                                                                                                                                                                                                                                                                                                                                              |                                                                              |

|           | 4.2.7.3 Parser/Procedure                                                                                                                                                                                                                                                                                                                                                                                             | 4-11                                                                         |

|           | 4.2.7.4 Interrupts                                  | 4-1  |

|-----------|-----------------------------------------------------|------|

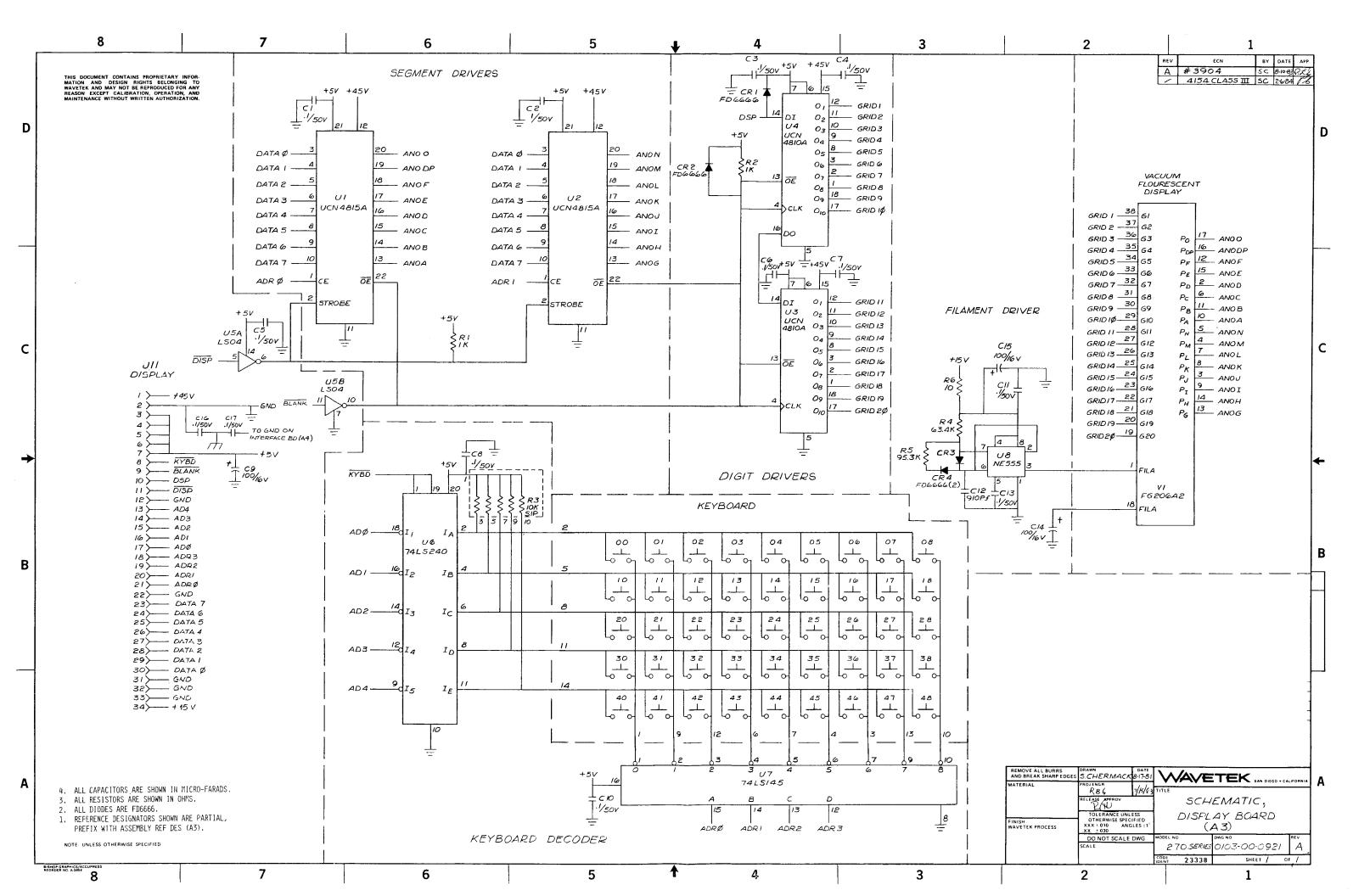

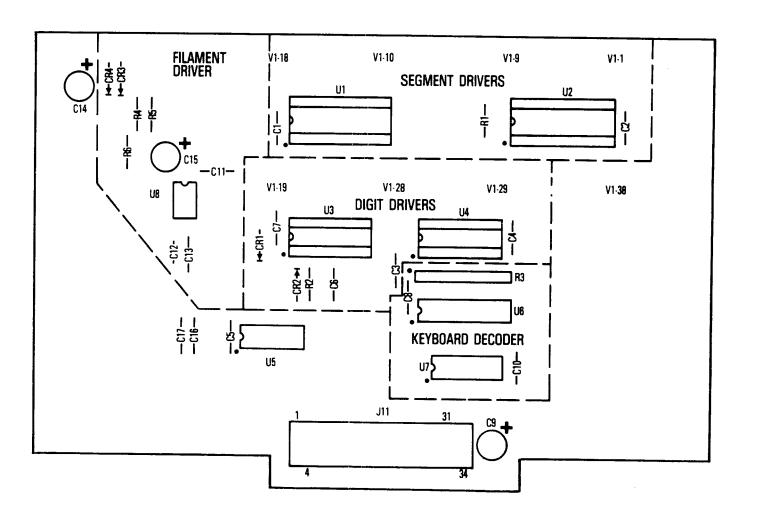

|           | 4.3 OPERATOR INTERFACE CIRCUIT DESCRIPTION          | 4-12 |

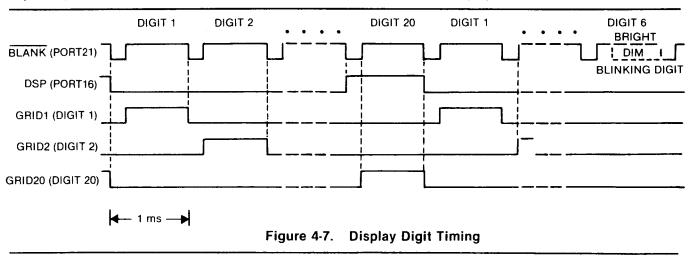

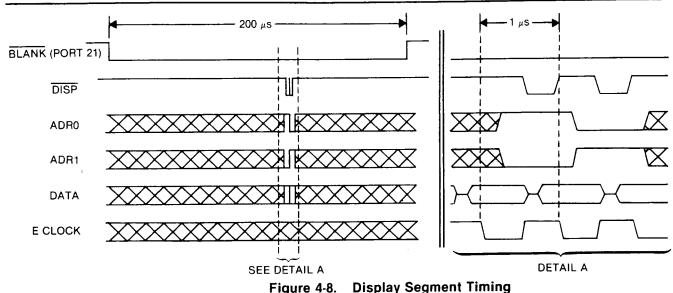

|           | 4.3.1 Display                                       | 4-12 |

|           | 4.3.2 Keyboard                                      |      |

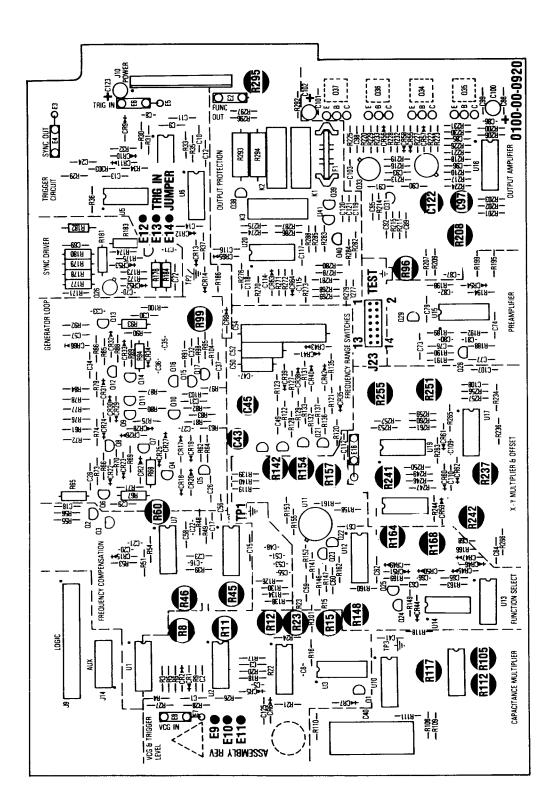

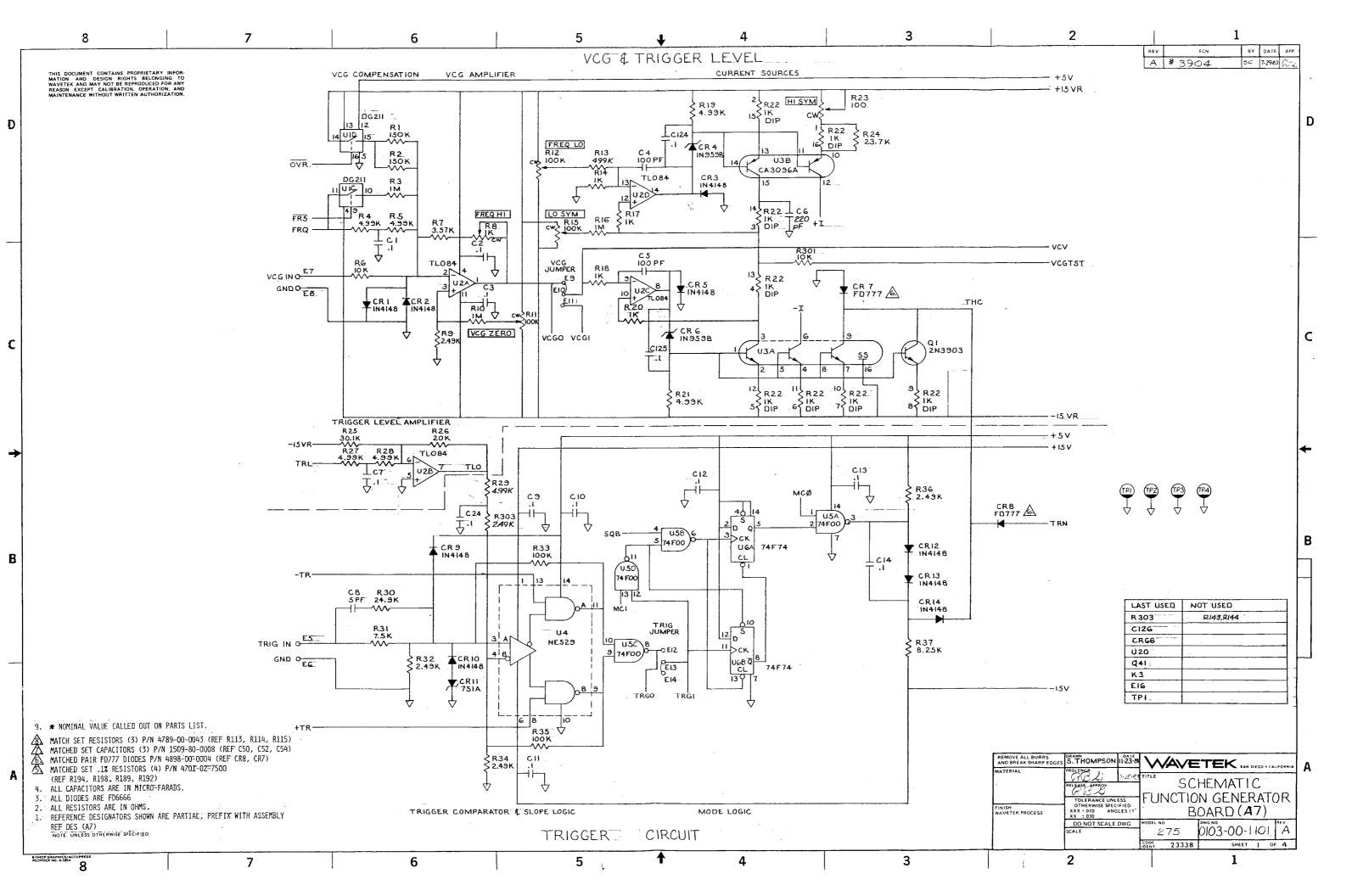

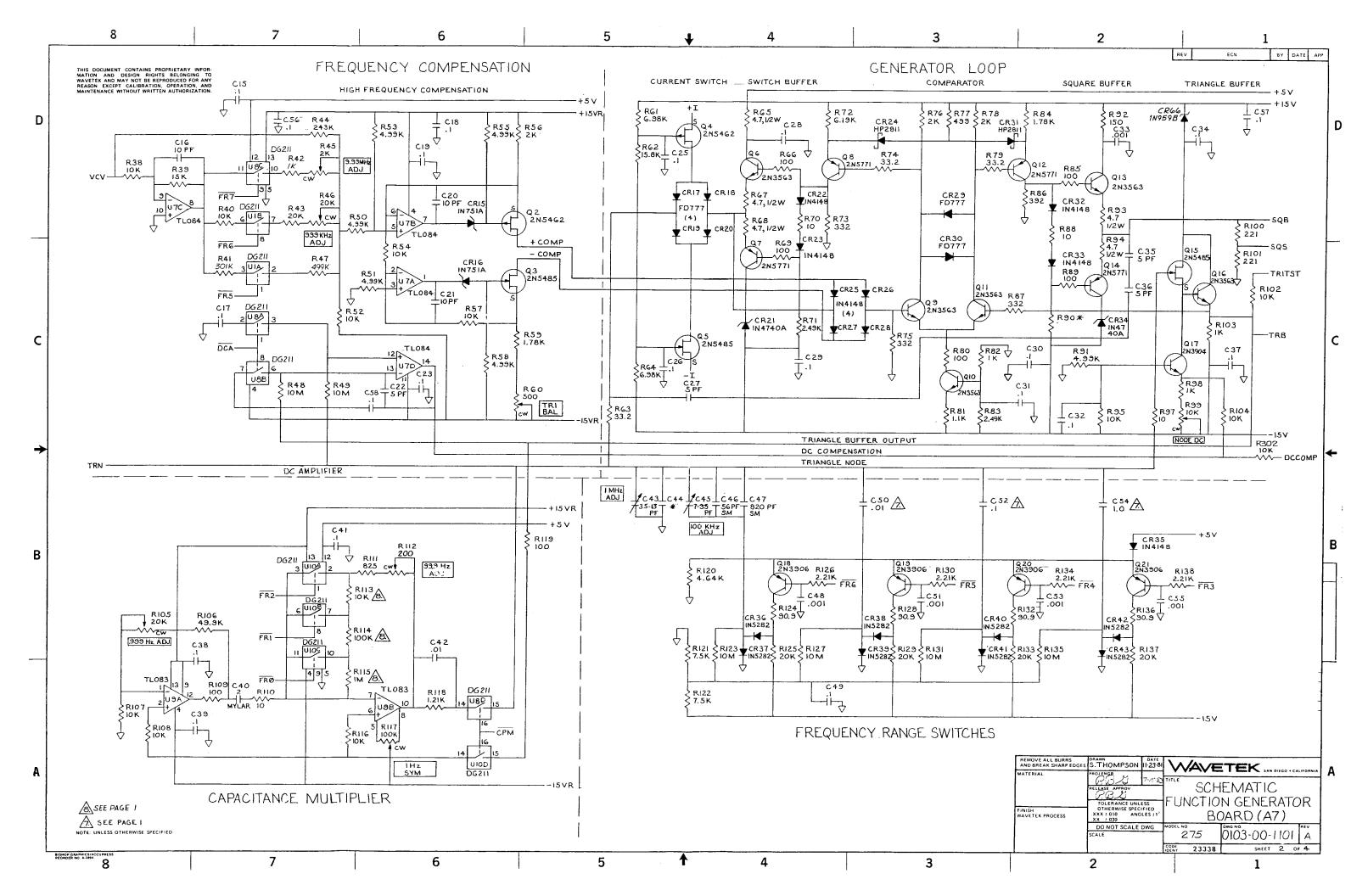

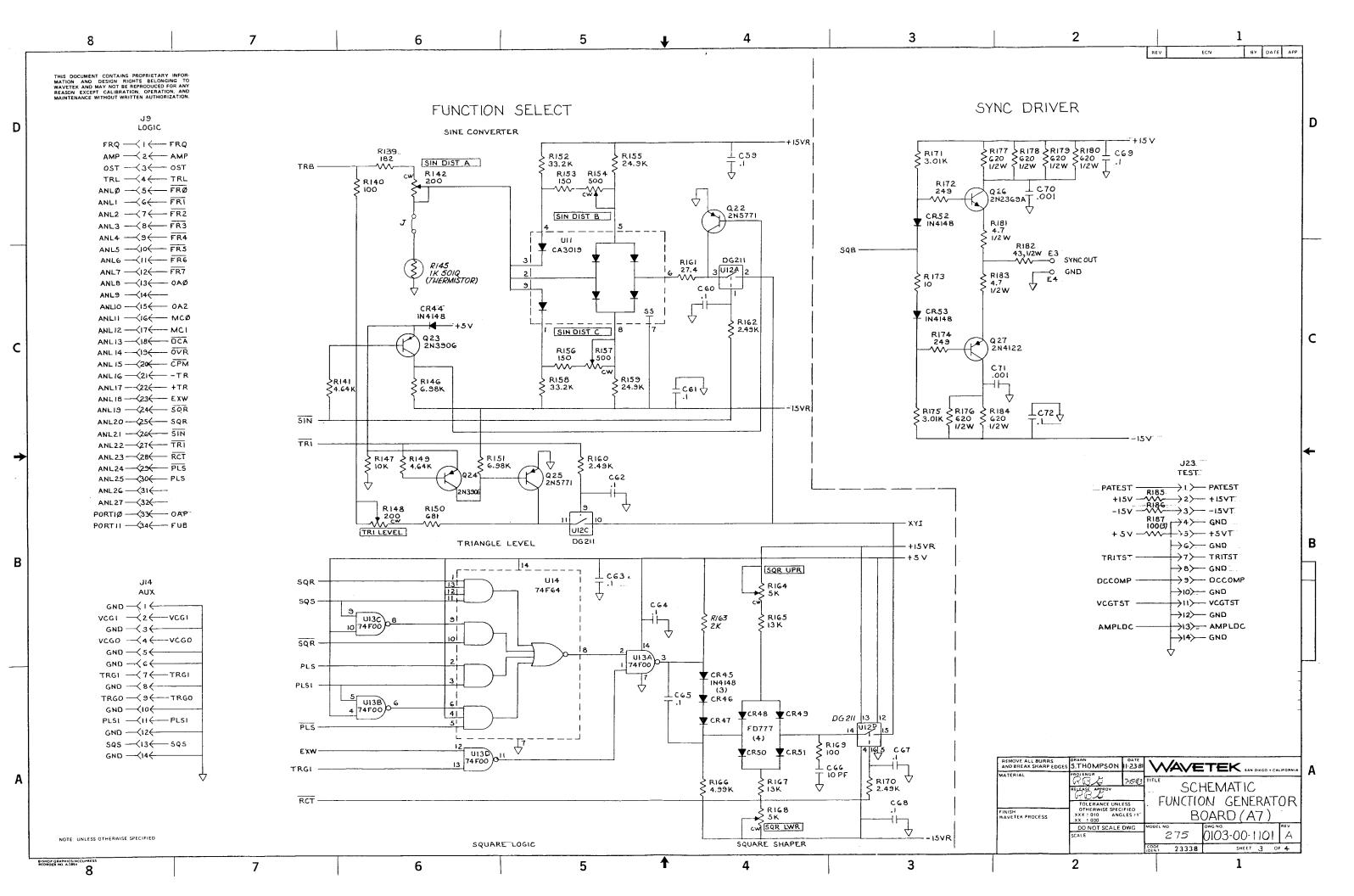

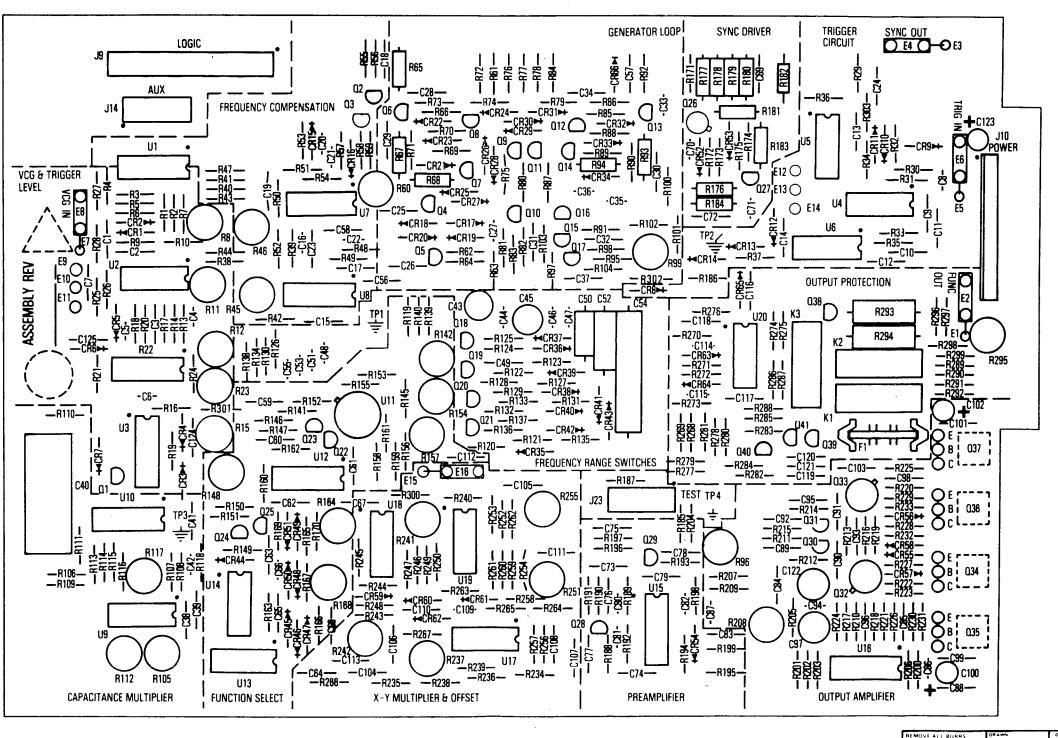

|           | 4.4 FUNCTION GENERATOR CIRCUIT DESCRIPTION          | 4-13 |

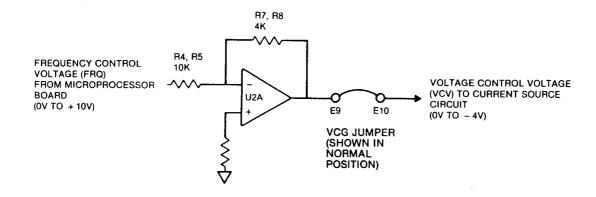

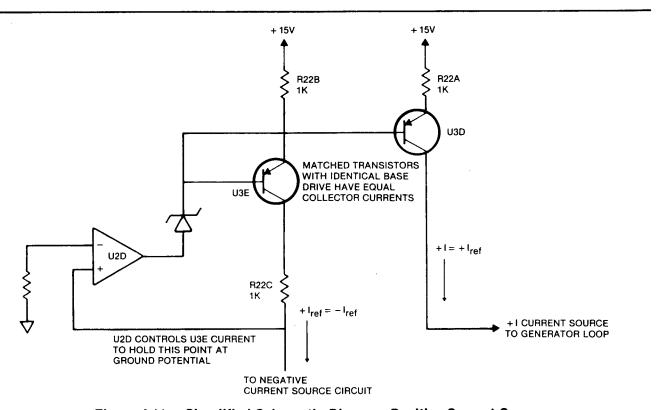

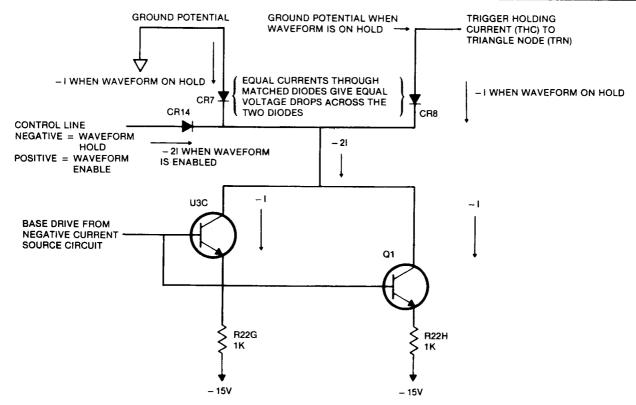

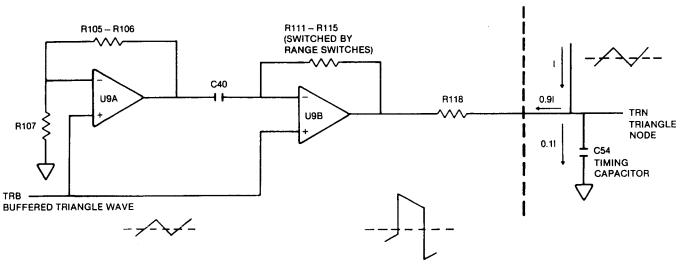

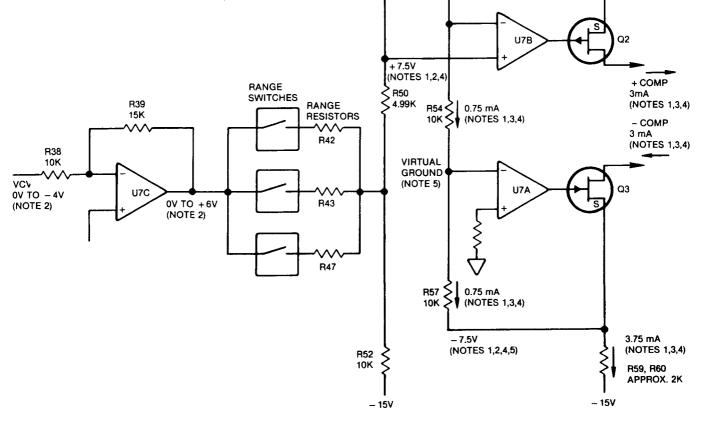

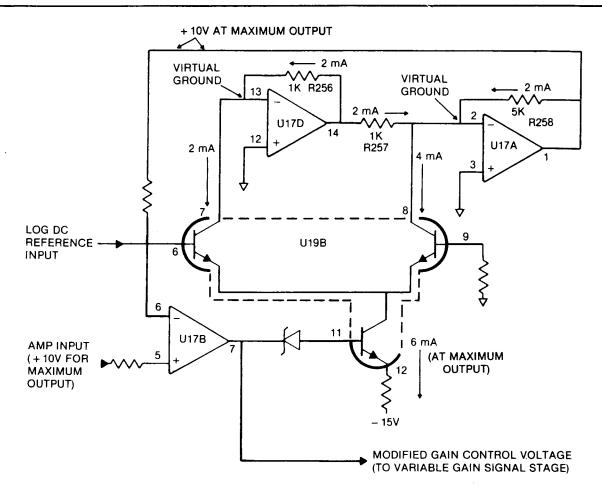

|           | 4.4.1 VCG and Trigger Level                         | 4-13 |

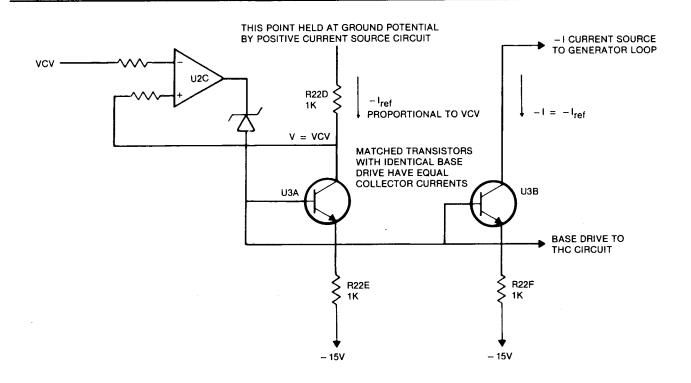

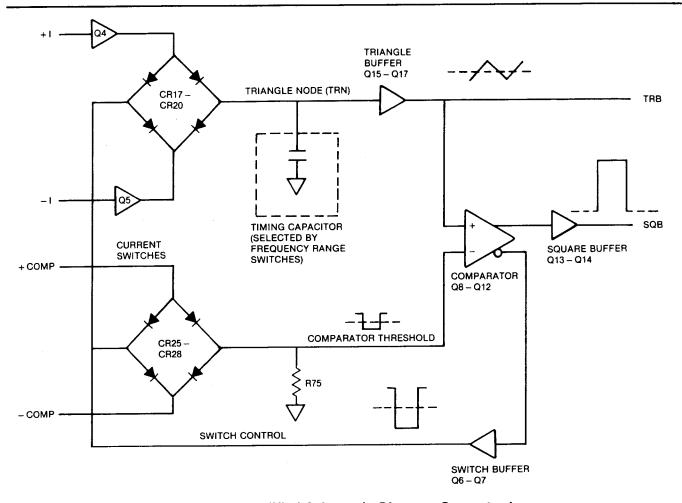

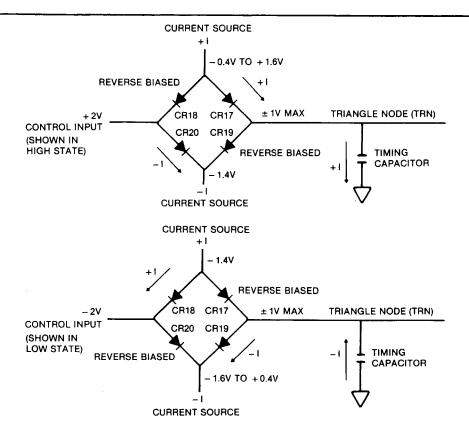

|           | 4.4.2 Generator Loop                                | 4-16 |

|           | 4.4.3 Frequency Range Switches                      | 4-19 |

|           | 4.4.5 Capacitance Multiplier                        |      |

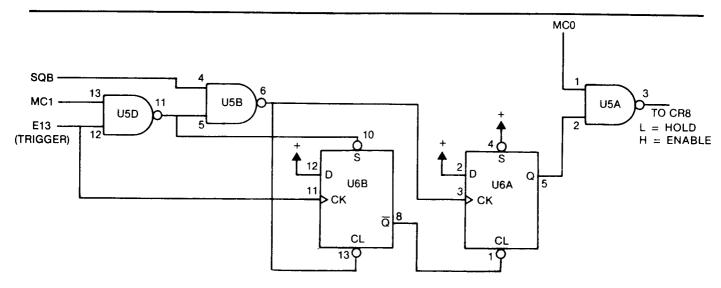

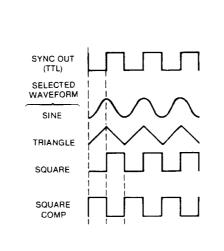

|           | 4.4.6 Sync Driver                                   |      |

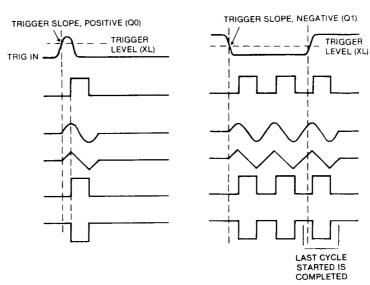

|           | 4.4.7 Trigger Circuit                               |      |

|           | 4.4.8 Function Select                               |      |

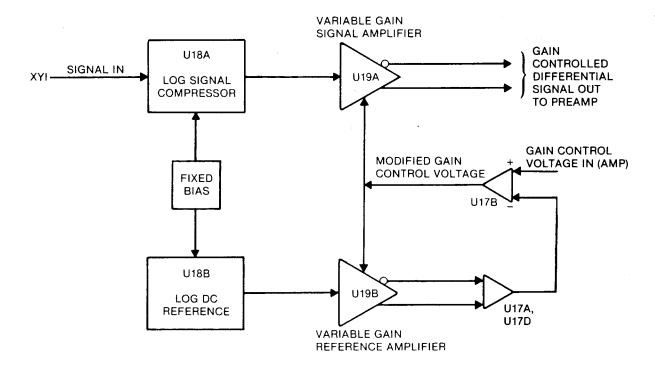

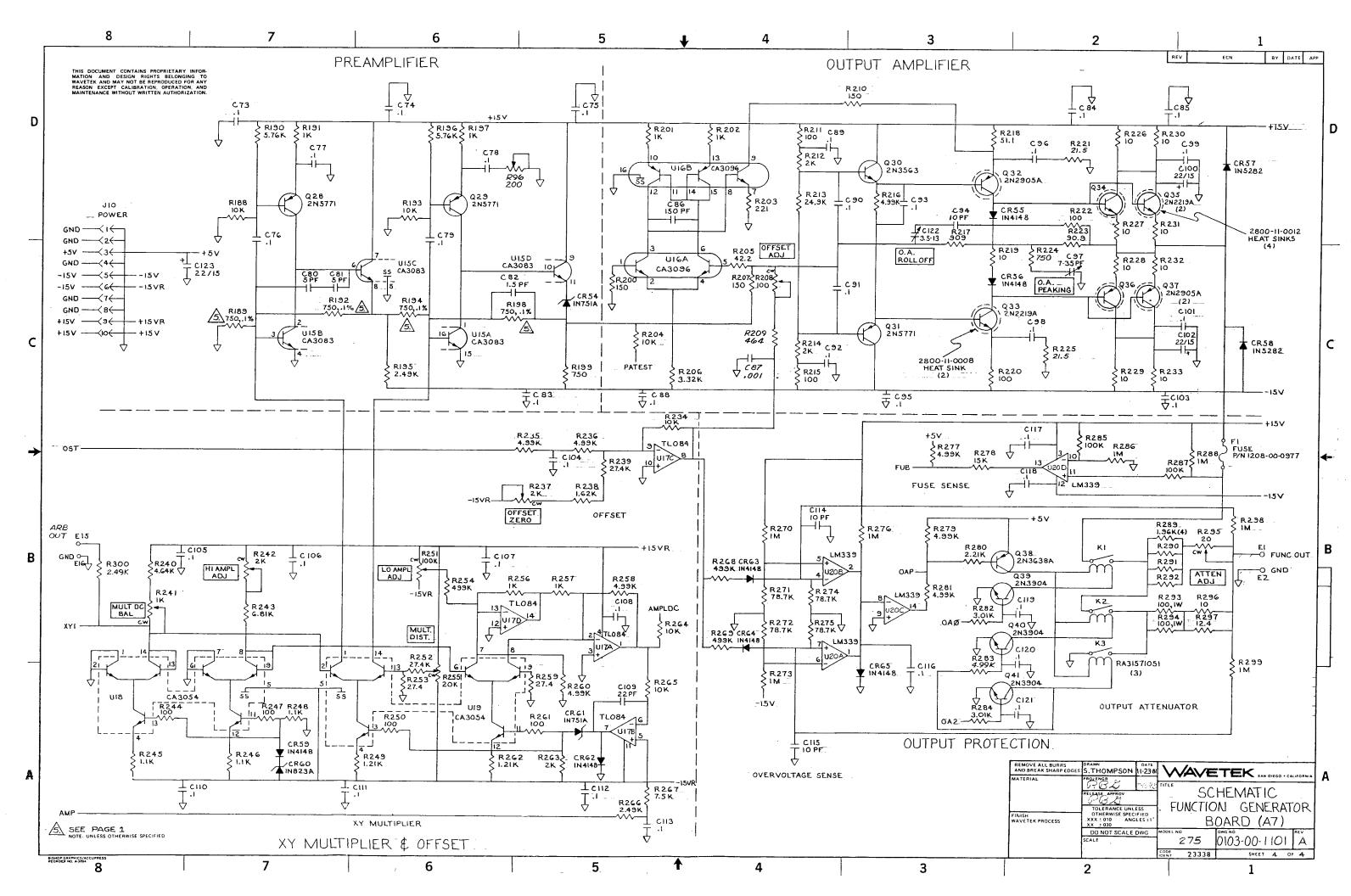

|           | 4.4.9 X-Y Multiplier and Offset                     |      |

|           | 4.4.9.1 X-Y Multiplier                              |      |

|           | 4.4.9.2 Offset Circuit                              |      |

|           | 4.4.10 Preamplifier                                 |      |

|           | 4.4.11 Output Amplifier                             |      |

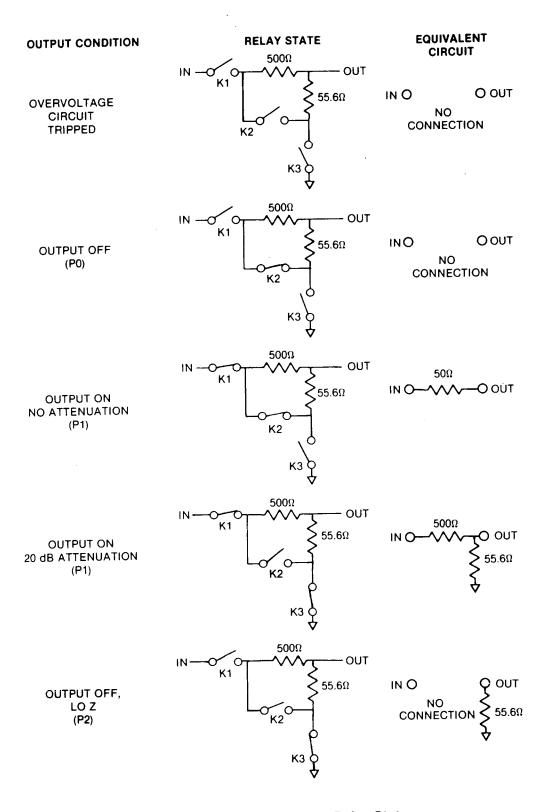

|           | 4.4.12 Output Protection and Attenuator.            |      |

|           | 4.4.12.1 Overvoltage Sense Circuit                  |      |

|           | 4.4.12.2 Fuse Protection                            |      |

|           | 4.4.12.3 Output Attenuator                          |      |

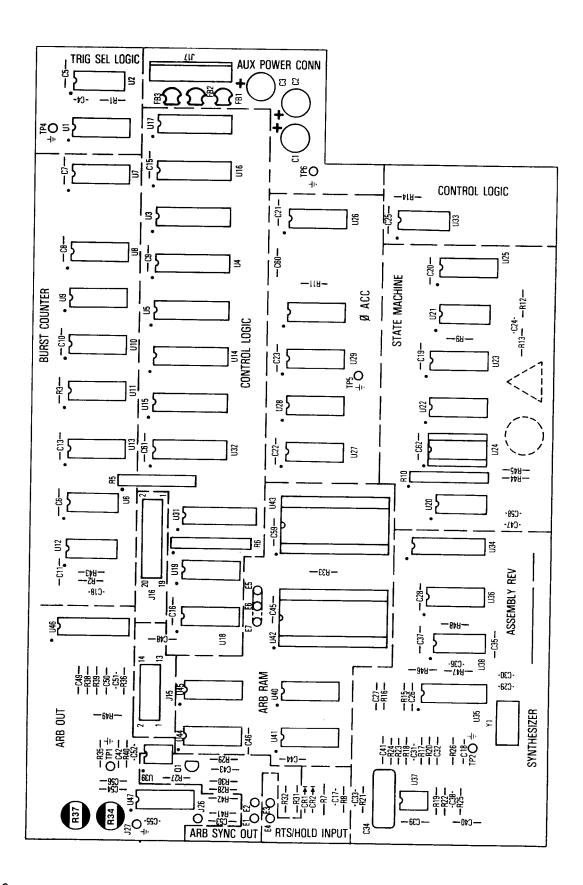

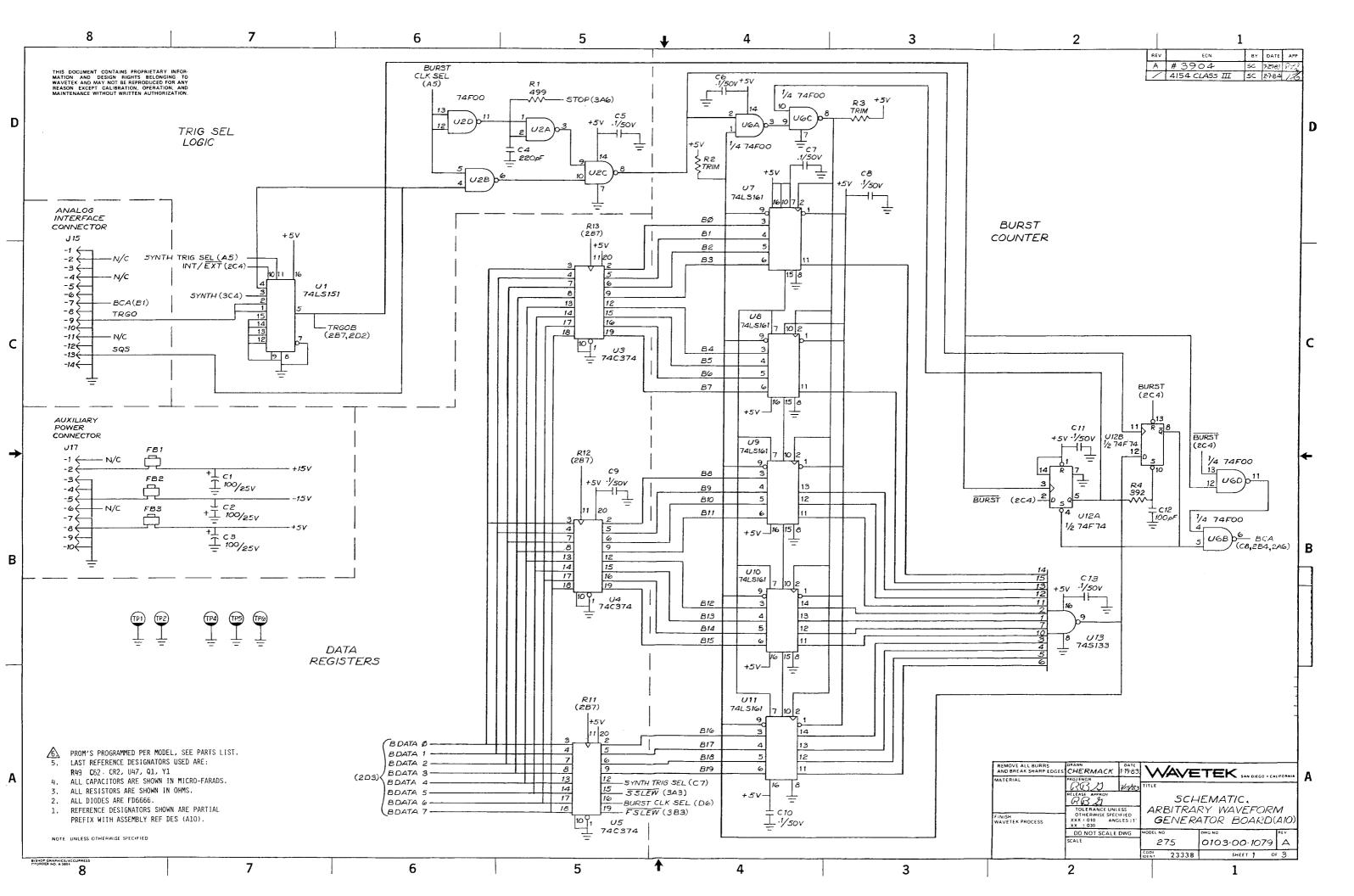

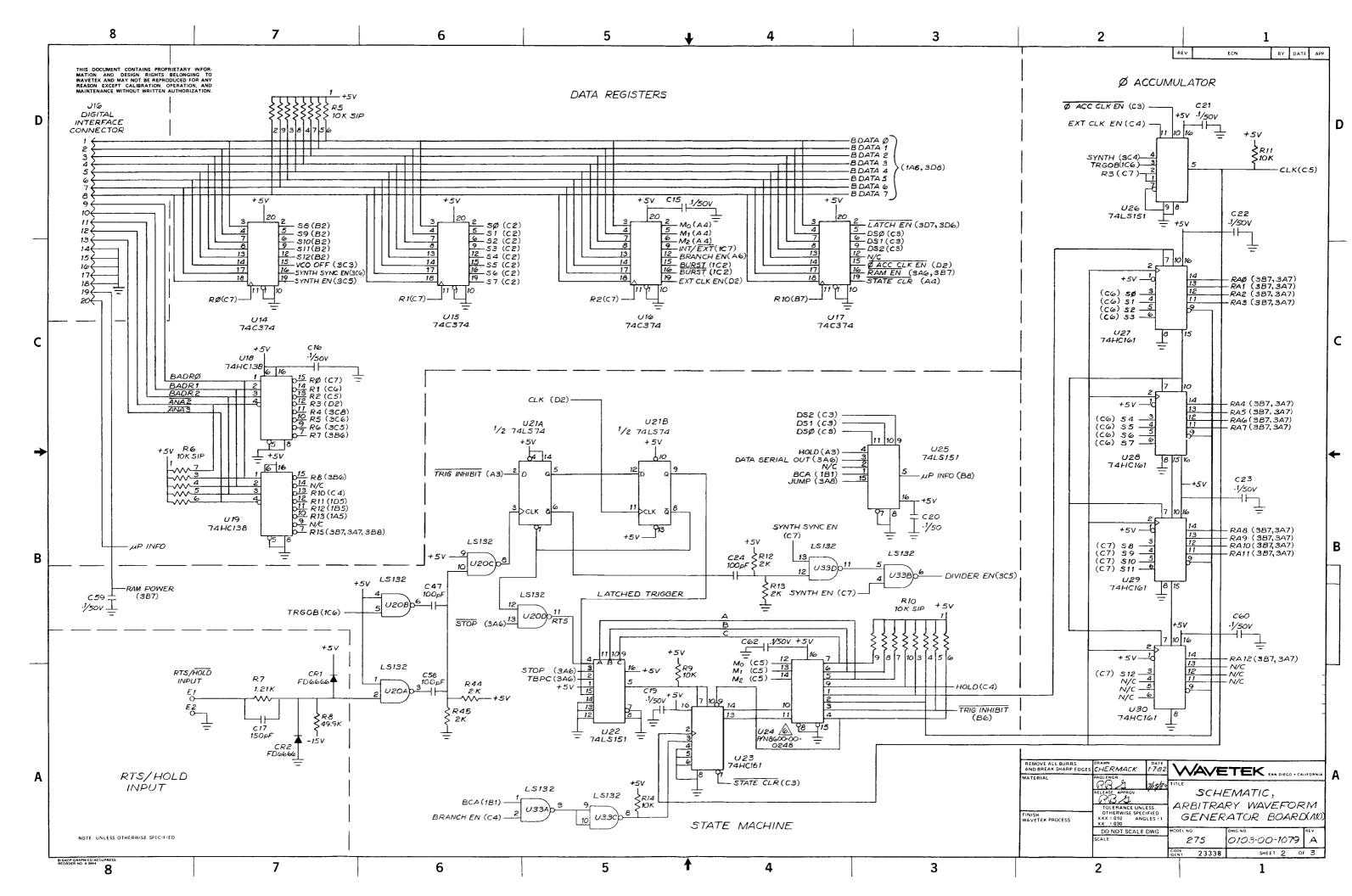

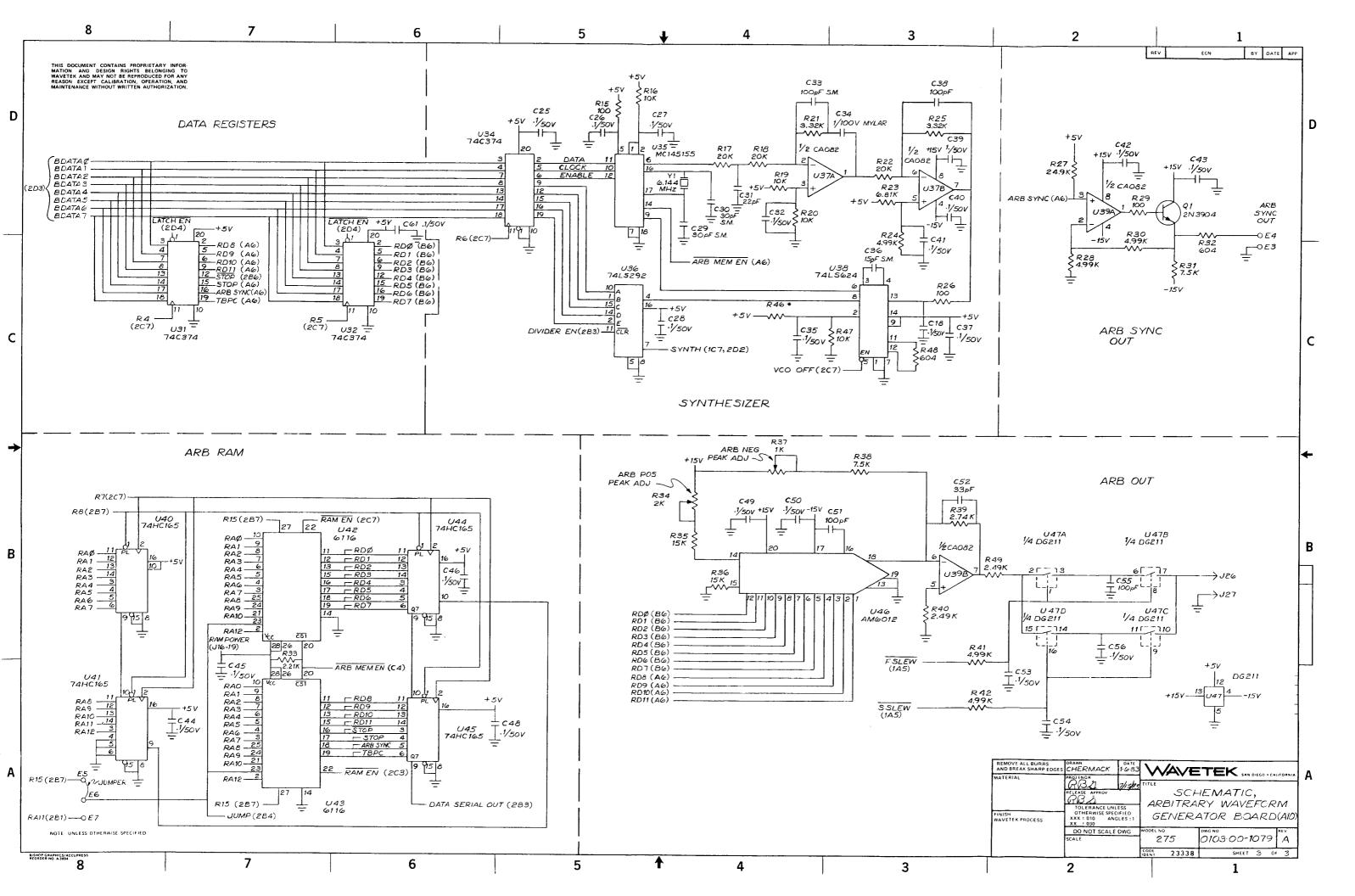

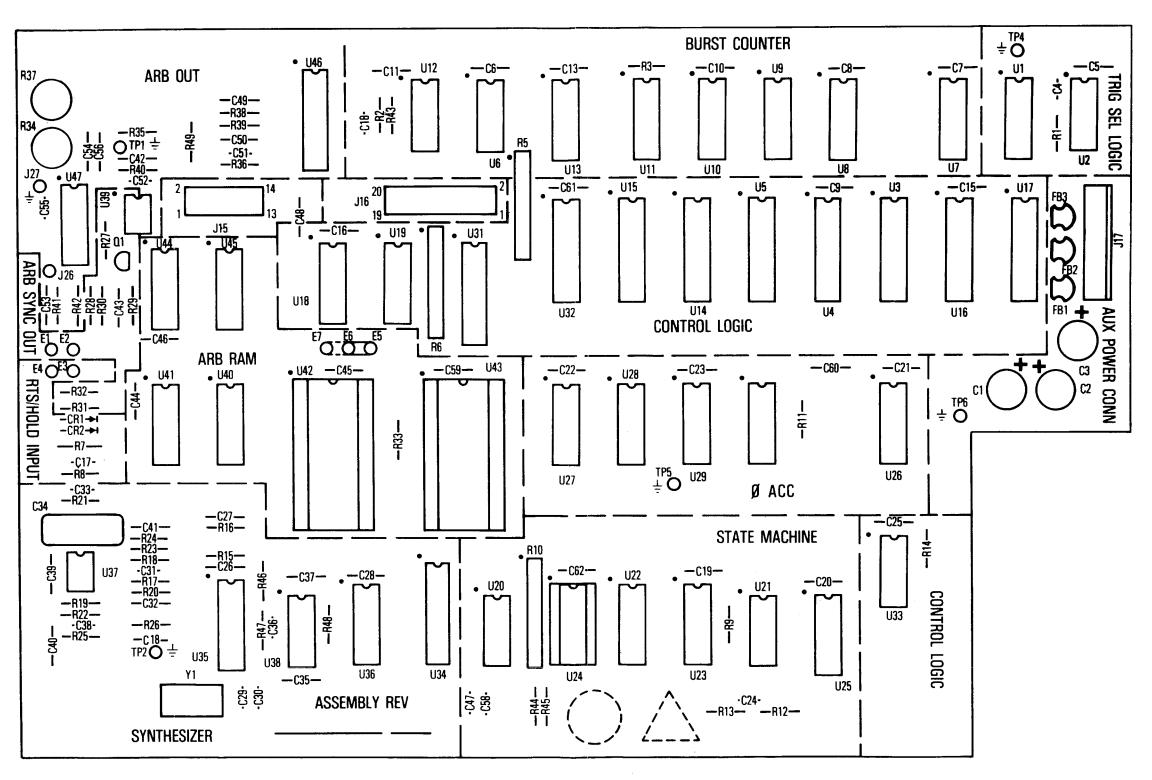

|           | 4.5 AUXILIARY BOARD CIRCUIT DESCRIPTION             |      |

|           | 4.5.1 Data Registers                                |      |

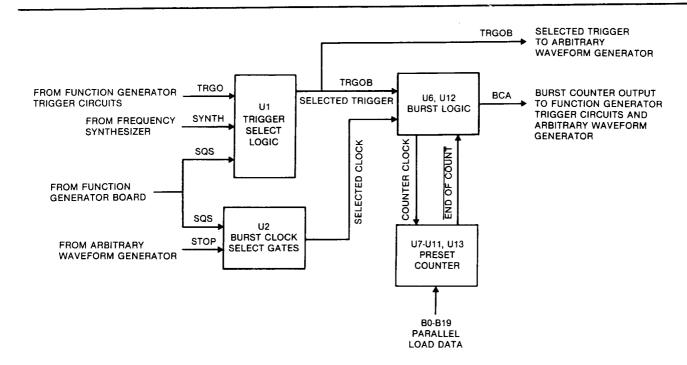

|           | 4.5.2 Burst Counter                                 |      |

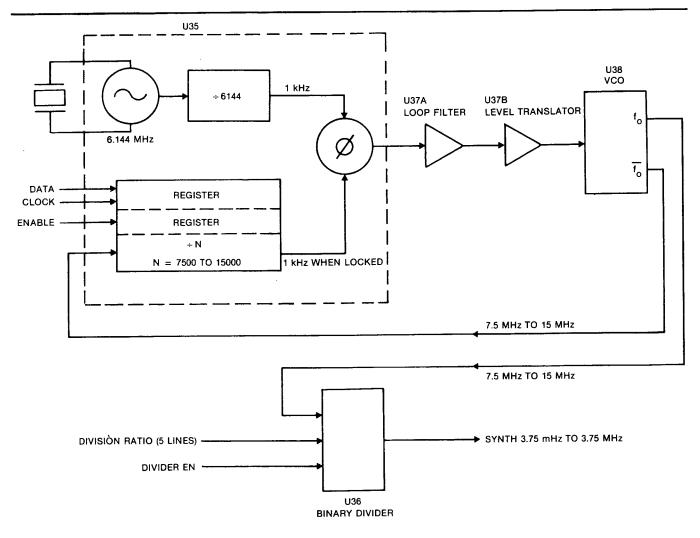

|           | 4.5.3 Frequency Synthesizer                         |      |

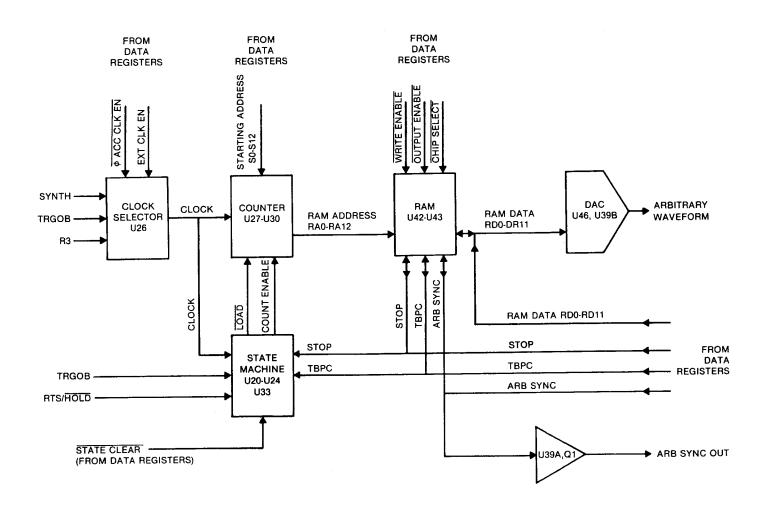

|           | 4.5.4 Arbitrary Waveform Generator                  |      |

|           | 4.5.4.1 Phase Accumulator                           |      |

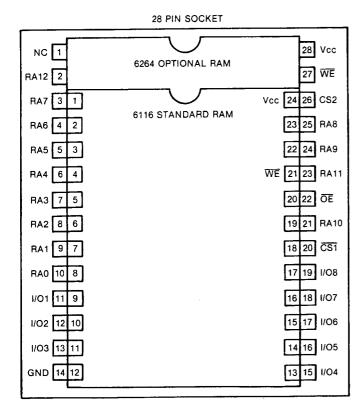

|           | 4.5.4.2 ARB RAM Circuit                             |      |

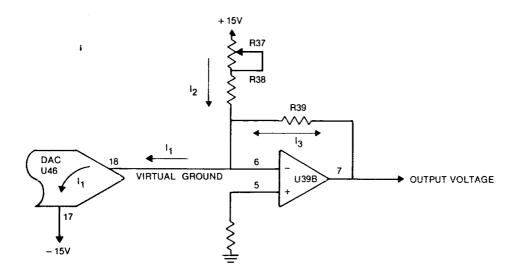

|           | 4.5.4.3 ARB OUT Circuit                             |      |

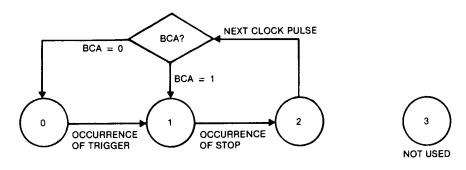

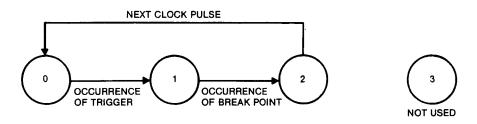

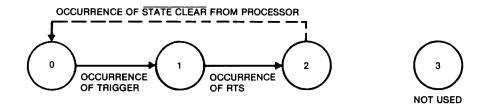

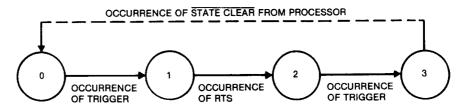

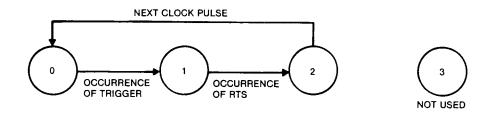

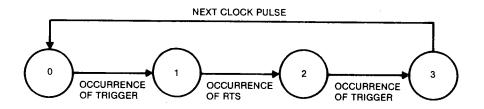

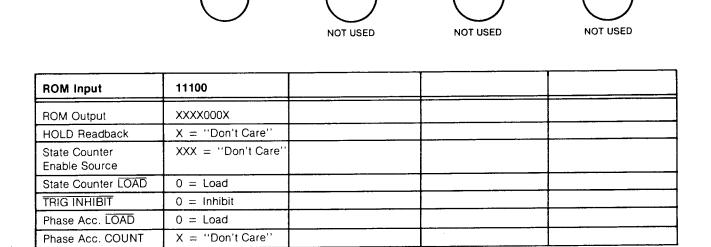

|           | 4.5.4.4 State Machine Circuit                       |      |

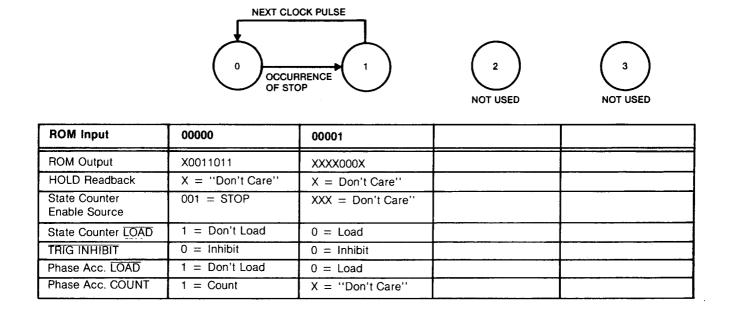

|           | 4.5.4.4.1 State Machine Circuit                     |      |

|           | 4.5.4.4.2 State Machine Sequence Control Circuit    |      |

|           | 4.5.4.5 Other Arbitrary Waveform Generator Circuits |      |

|           |                                                     |      |

|           |                                                     |      |

|           | 4.5.4.5.2 ARB SYNC OUT Circuit                      | 4-45 |

| SECTION 5 | CALIBRATION                                         |      |

|           | 5.1 FACTORY REPAIR                                  | 5-1  |

|           | 5.2 CALIBRATION                                     | 5-1  |

|           |                                                     |      |

| SECTION 6 | TROUBLESHOOTING                                     |      |

|           | 6.1 FACTORY REPAIR                                  | 6-1  |

|           | 6.2 BEFORE YOU START                                | 6-1  |

|           | 6.3 TROUBLESHOOTING                                 | 6-1  |

|           | 6.4 TROUBLESHOOTING INDIVIDUAL COMPONENTS           | 6-2  |

|           | 6.4.1 Transistor                                    | 6-2  |

|           | 6.4.2 Diode                                         | 6-2  |

|           | 6.4.3 Operational Amplifier                         | 6-2  |

|           | 6.4.4 FET Transistor                                | 6-2  |

|           |                                                     |      |

|           | 6.4.5 Capacitor                                                                                                                                                                                                                                                    |                   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

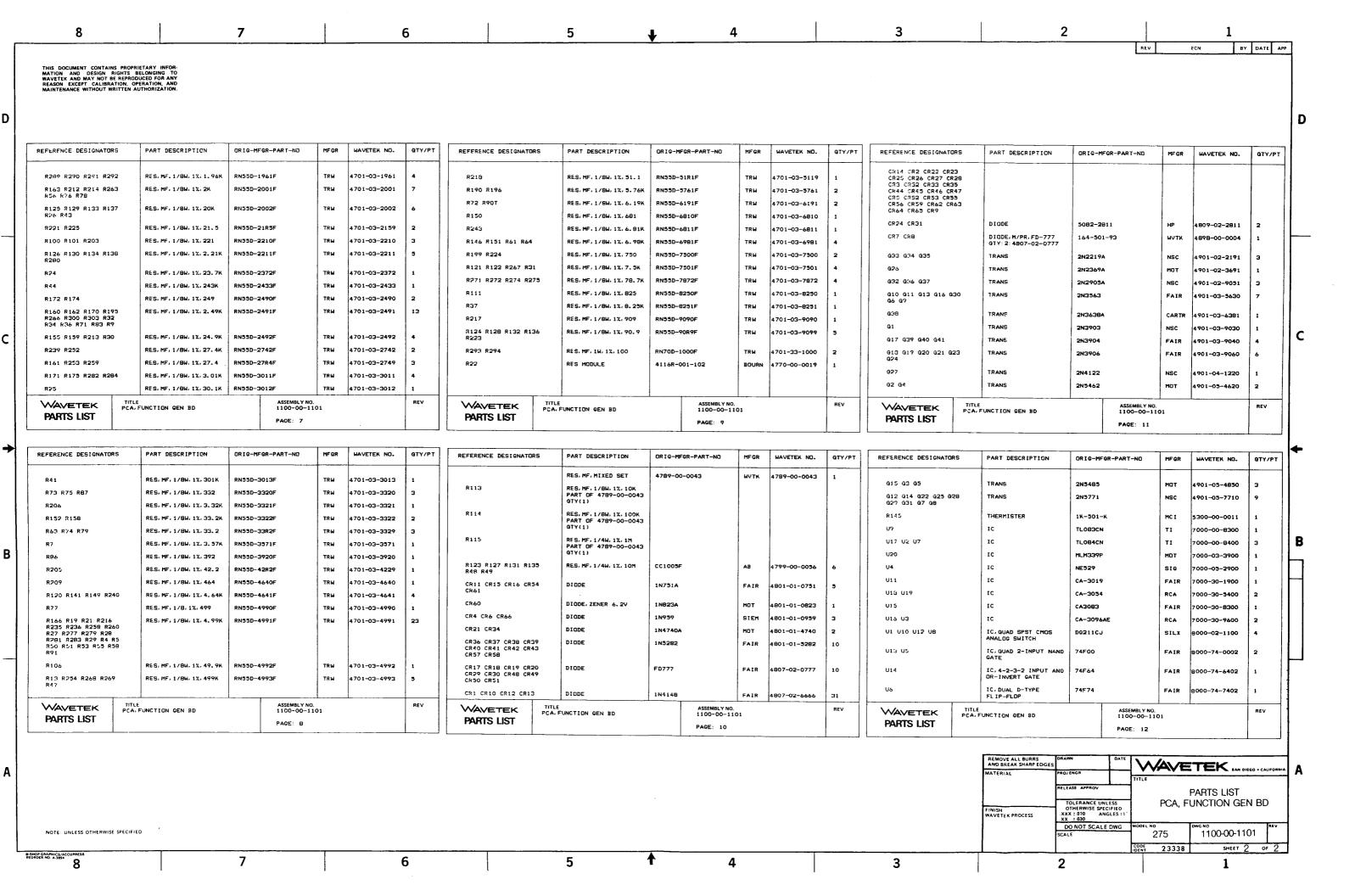

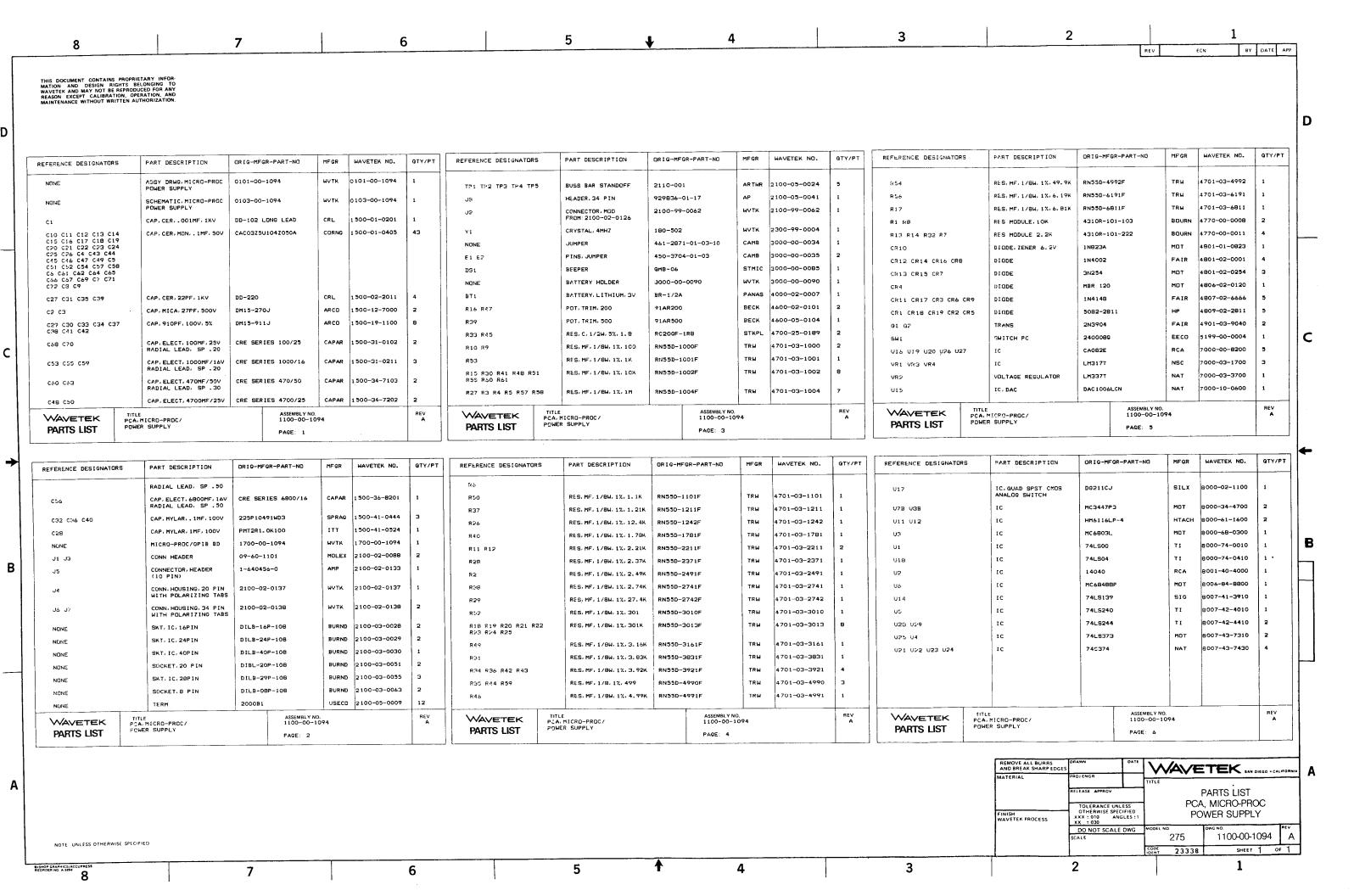

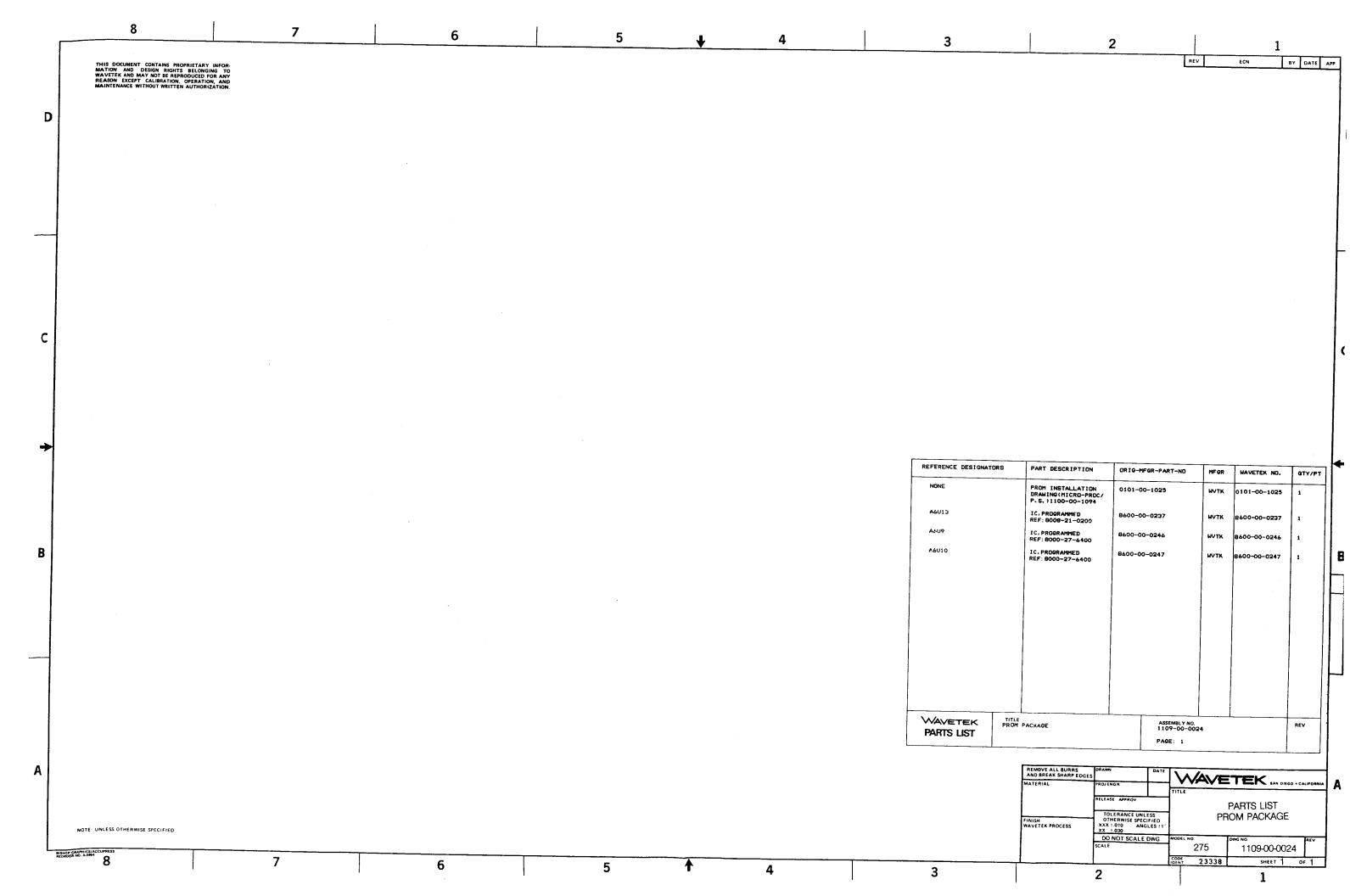

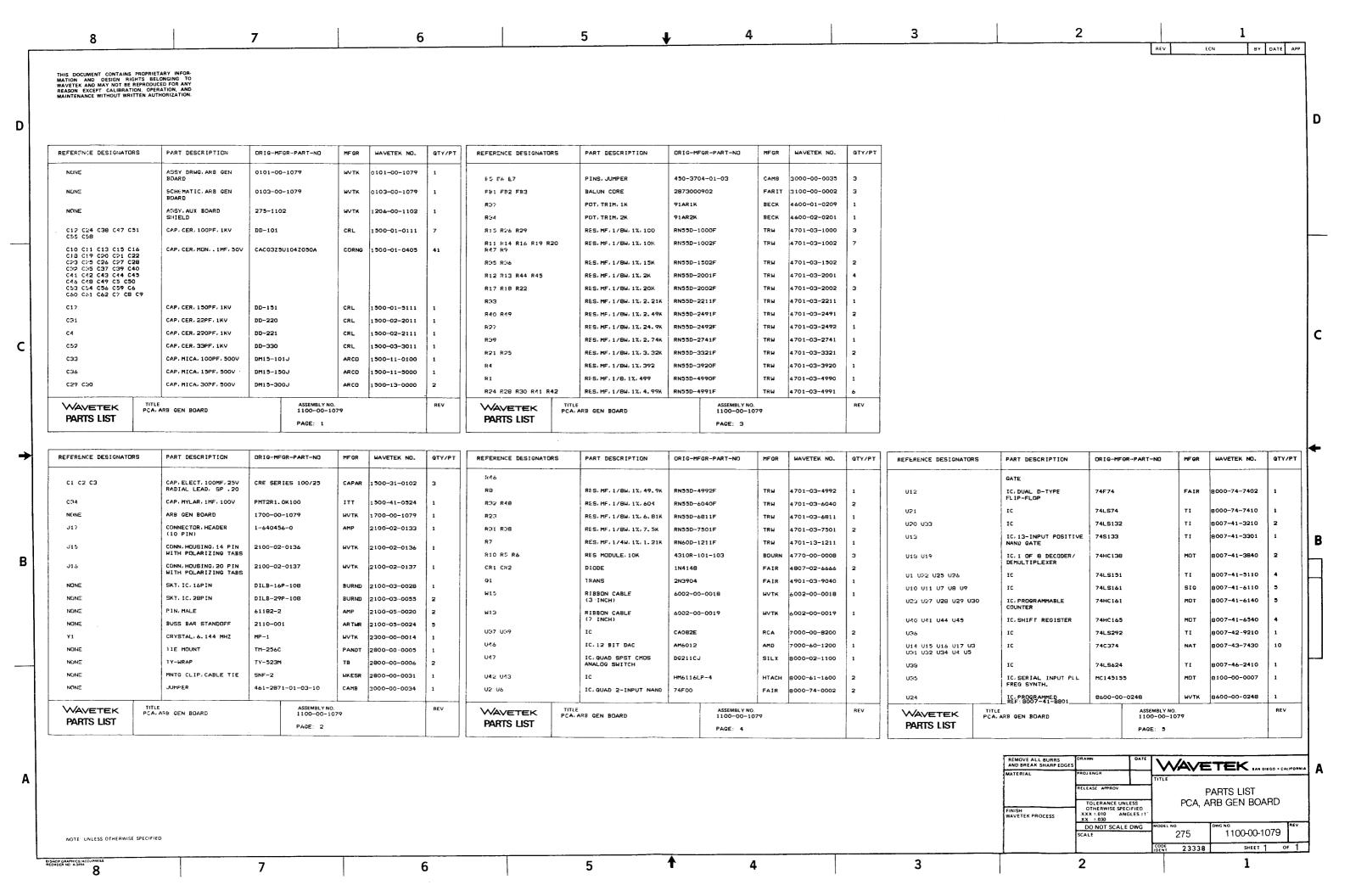

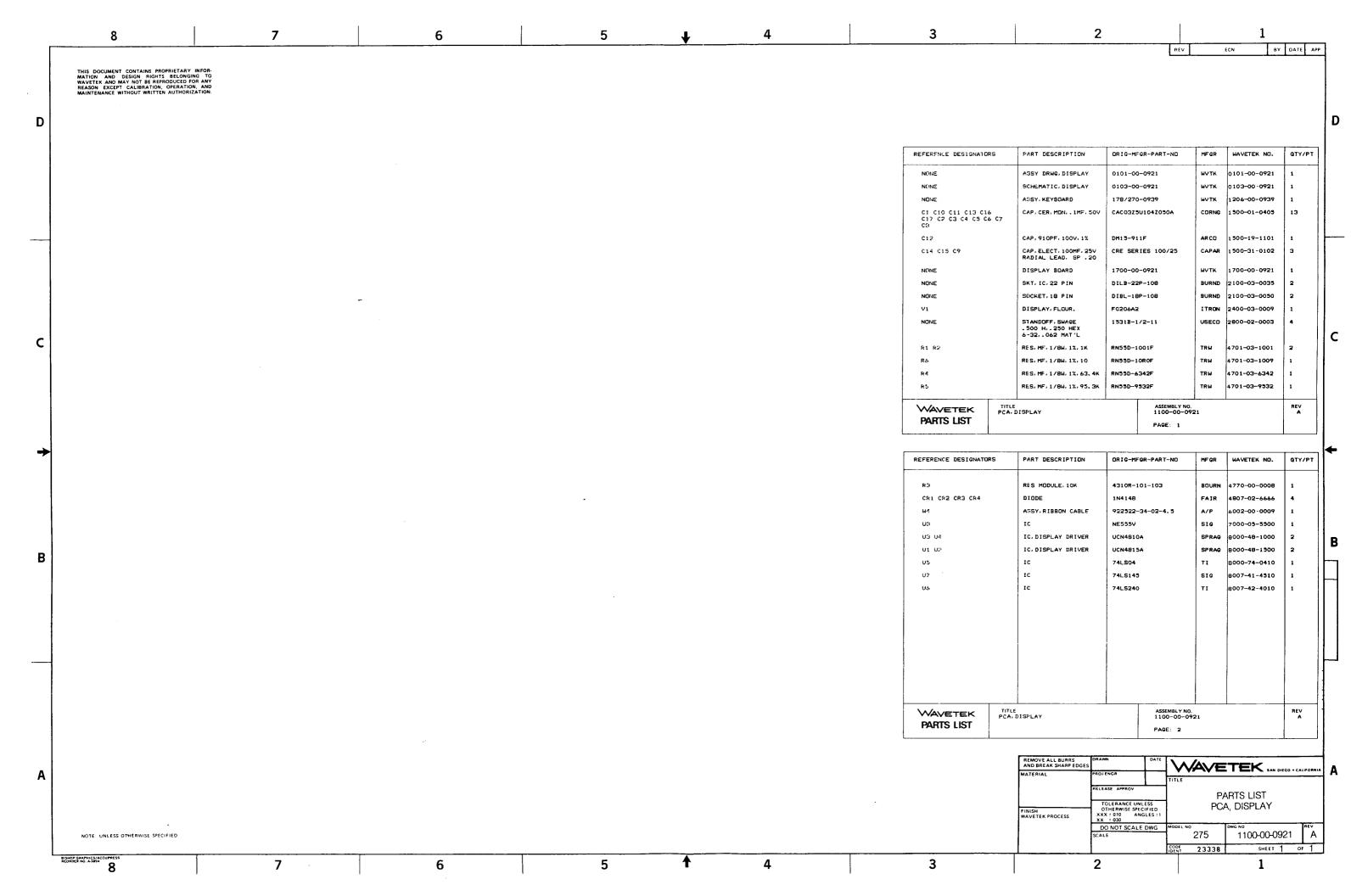

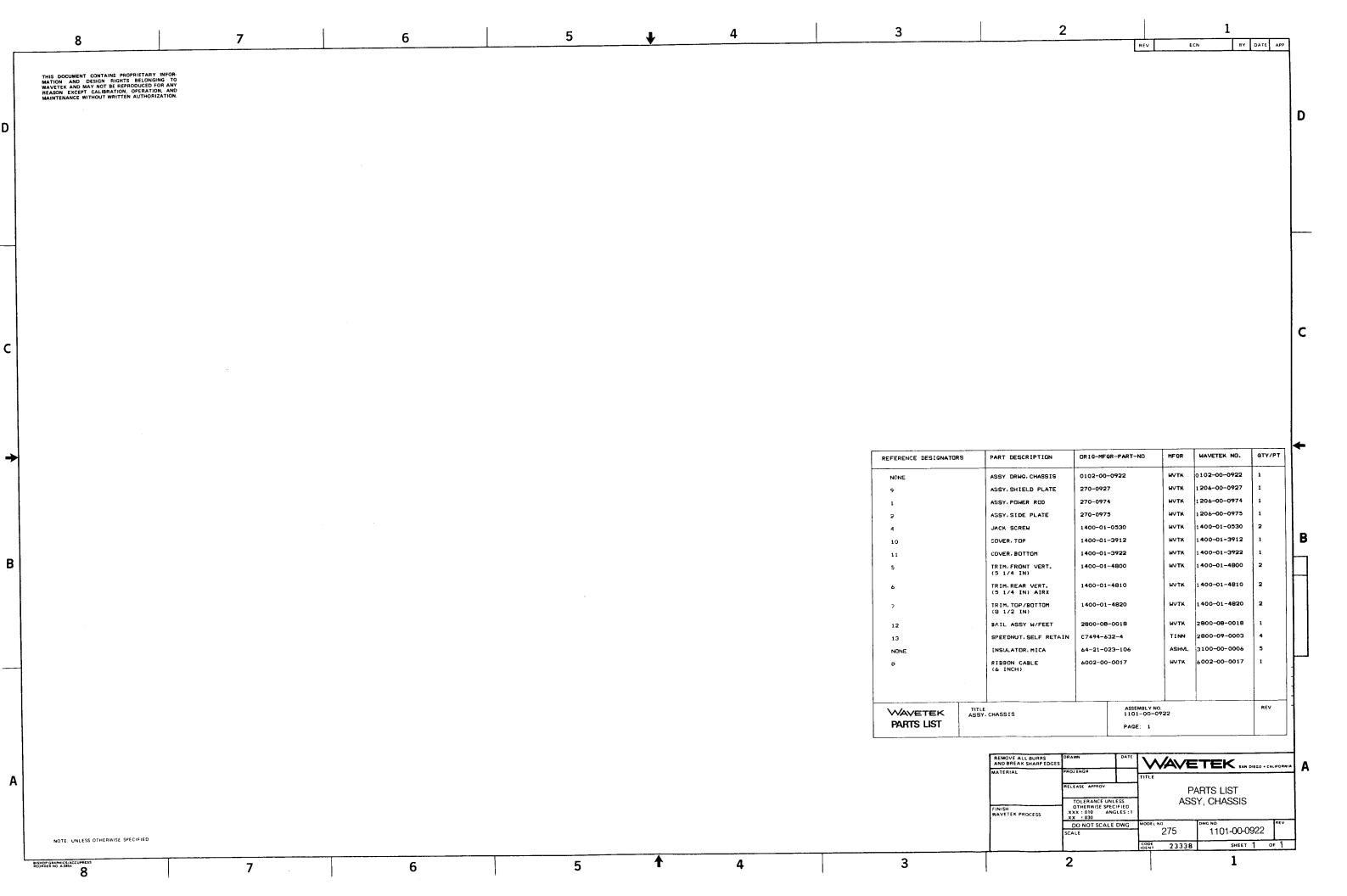

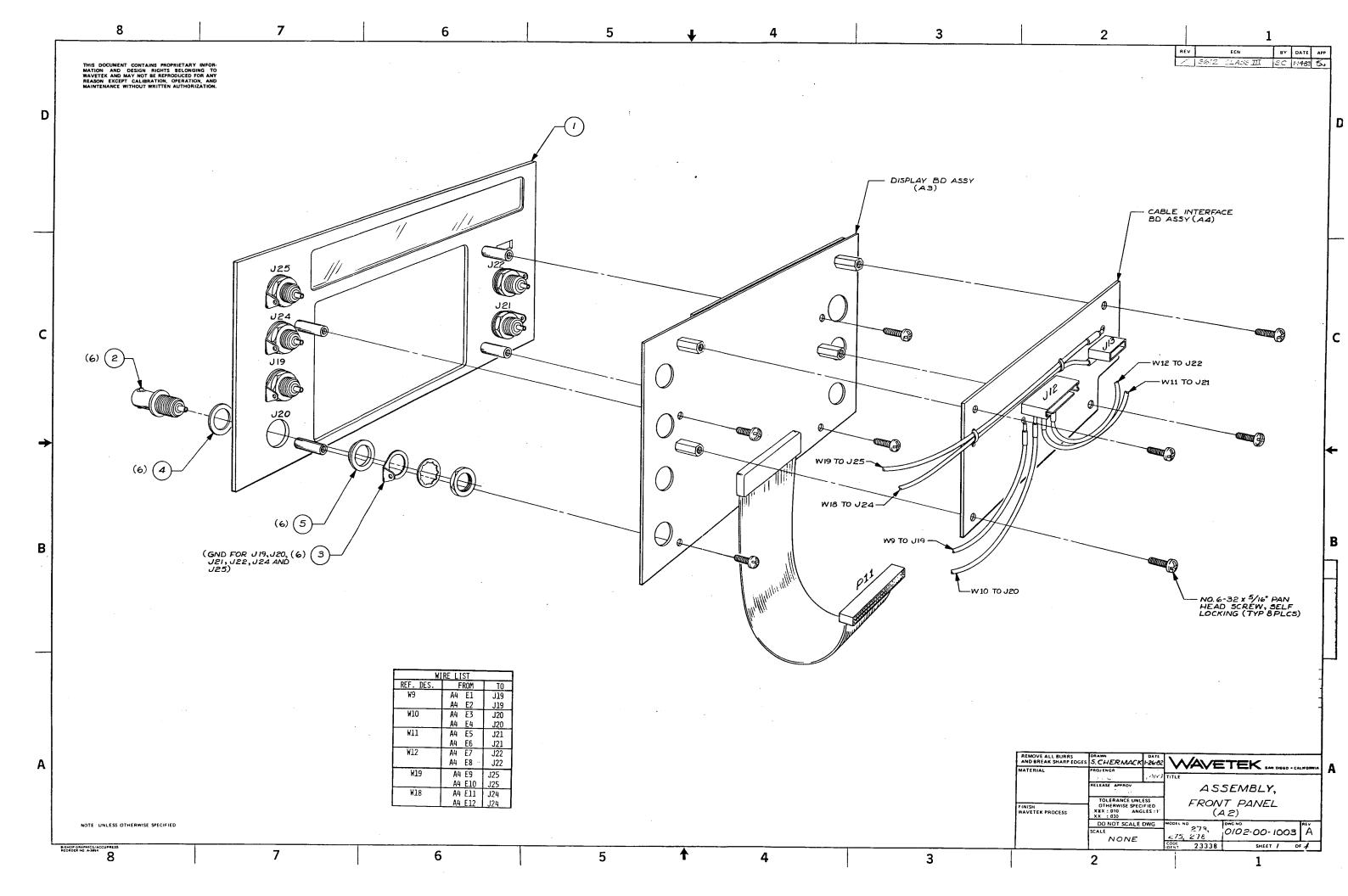

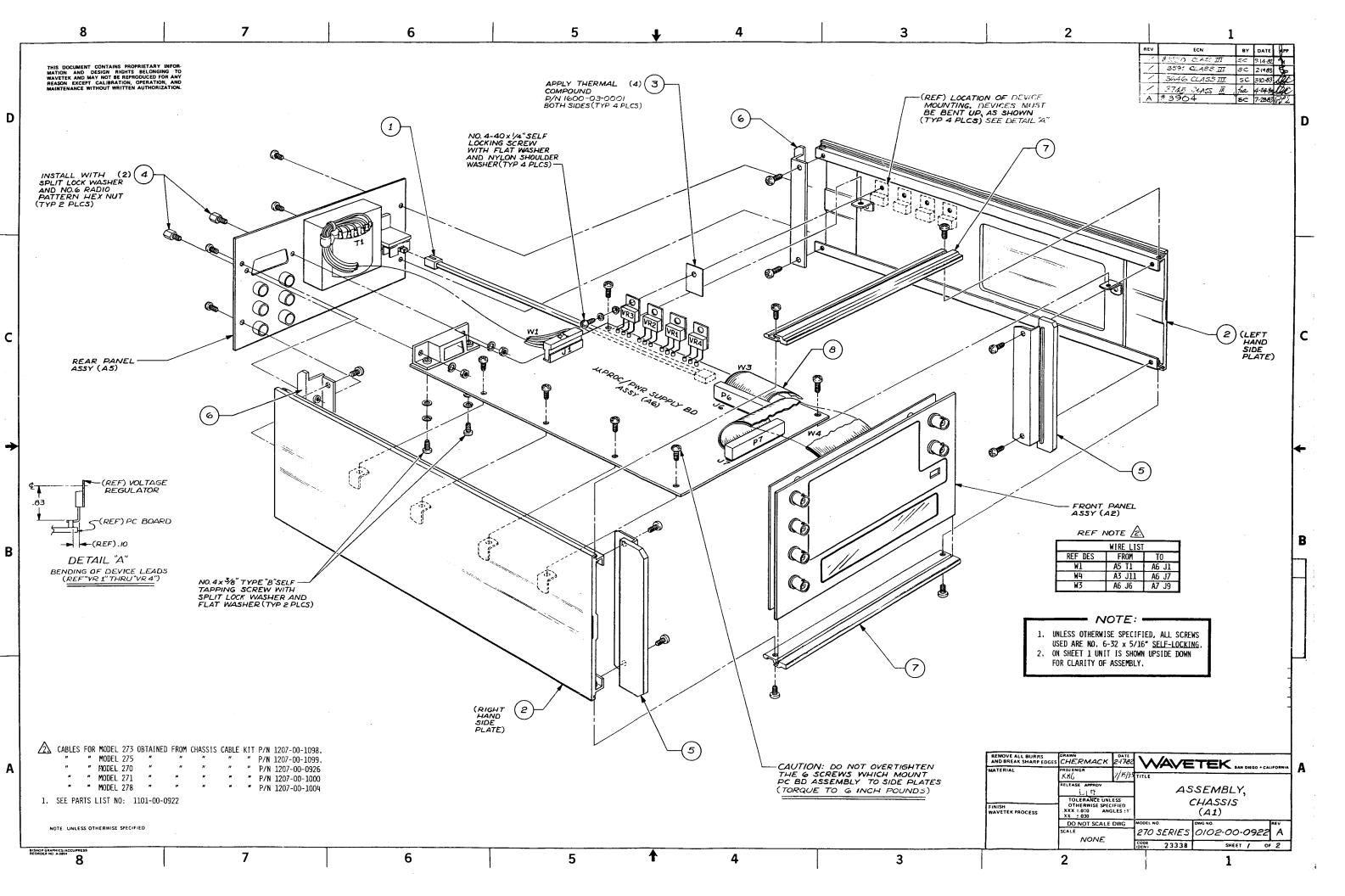

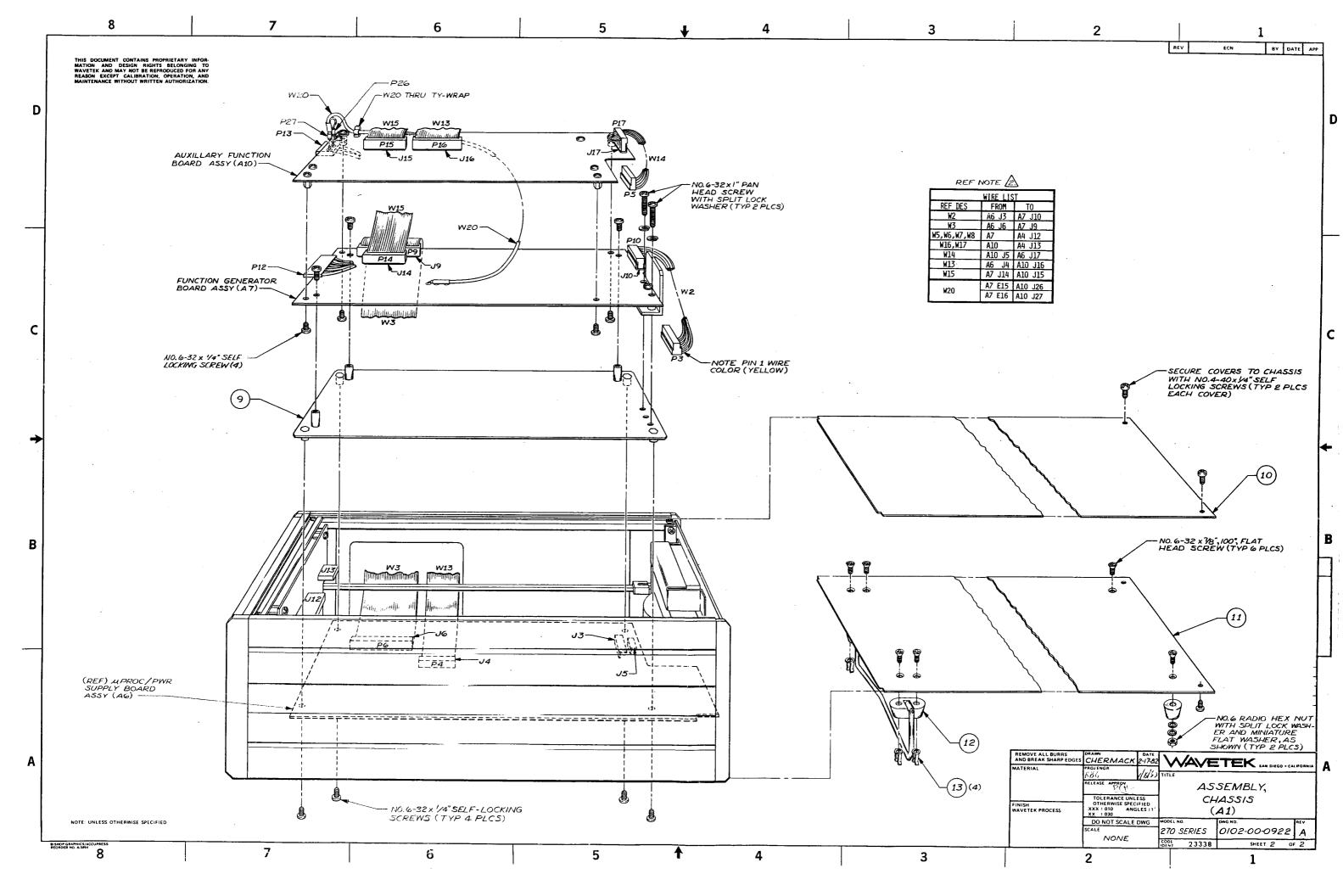

| SECTION 7 | PARTS AND SCHEMATICS                                                                                                                                                                                                                                               |                   |

|           | 7.1 DRAWINGS<br>7.2 ADDENDA<br>7.3 ORDERING PARTS                                                                                                                                                                                                                  | 7-1               |

| APPENDIX  |                                                                                                                                                                                                                                                                    |                   |

|           | APPENDIX A American Standard Code For Information Interchange (ASCII).  APPENDIX B Programming Command Summary.  APPENDIX C Displays.  APPENDIX D Output and Timing for Modes and Functions.  APPENDIX E Glossary of Mneumonics.  APPENDIX F Waveform Measurements | B-1<br>C-1<br>D-1 |

## **SAFETY**

This instrument is wired for earth grounding via the facility power wiring. Do not bypass earth grounding with two wire extension cords, plug adapters, etc.

While the very low power of the rf energy generated in this instrument makes it ordinarily nonhazardous, extremely close and prolonged proximity of an eye and an rf output connector could cause injury.

BEFORE PLUGGING IN the instrument, comply with installation instructions.

MAINTENANCE may require power on with the instrument covers removed. This should be done only by qualified personnel aware of the electrical hazards.

The instrument power receptacle is connected to the instrument safety earth terminal with a green/yellow wire. Do not alter this connection. (Reference:

or stamped inside the rear panel near the safety earth terminal.)

WARNING notes call attention to possible injury or death hazards in subsequent operations.

CAUTION notes call attention to possible equipment damage in subsequent operations.

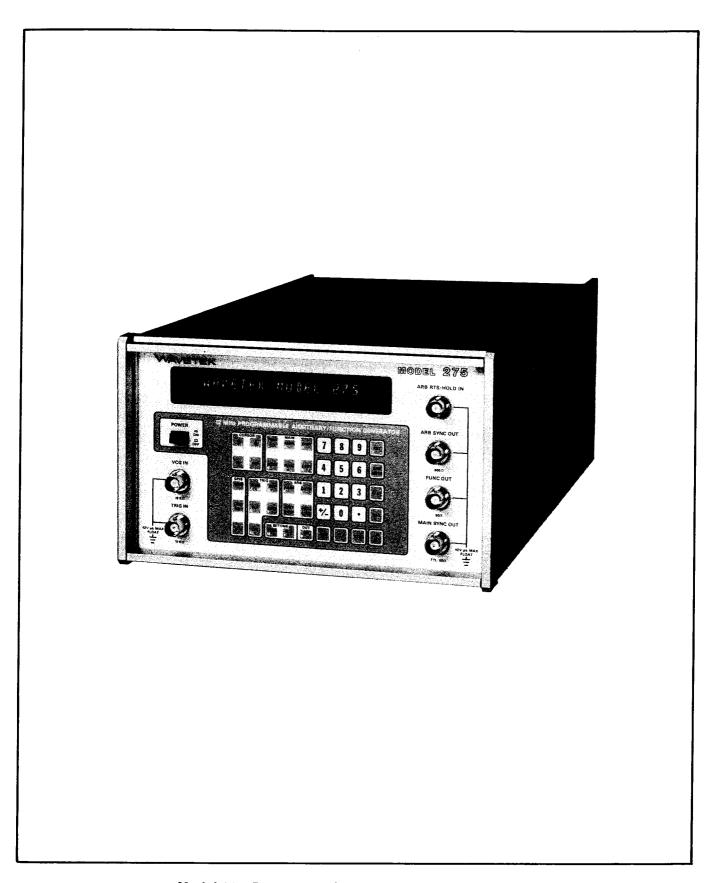

Model 275, Programmable Arbitrary/Function Generator

## SECTION SECTION

## 1.1 MODEL 275

The Wavetek 275 Programmable Arbitrary/Function Generator produces sine, triangle and square waveforms as well as user-defined arbitrary waveshapes. Any of the waveforms can be generated in the continuous, triggered, gated or burst modes. External width and dc functions are also provided.

Data entry is from the front panel or GPIB (IEEE 488-1978). Numeric input is entered in free format: fixed, floating, or exponential notation. Parameters may be entered in any order. Internally, all entries are interactively checked for errors and displayed on the front panel, or they may be accessed through the GPIB.

Arbitrary waveform amplitude resolution is 12 bits. Horizontal resolution is 2048 points (standard), expandable to 8192 points (optional). Arbitrary waveform clock period is programmable within the range of 267 ns to 267 s per point with 0.2% accuracy. Non-arbitrary waveform frequency range is 0.01 Hz to 12 MHz.

Output level is specified from 10 mV to 10 Vp-p into a  $50\Omega$  termination and 20 mV to 20 Vp-p into an open circuit with 3 digits of resolution. Offset can be programmed to vary the waveform base line up to  $\pm$  10V, or in the dc function, to vary the dc output.

All inputs and outputs are protected against short circuits and excessive voltages between  $\pm\,15$ V. The function output is further protected against voltage inputs up to 140 Vac or  $\pm\,200$  Vdc. Activation of the protection circuits will cause a front panel error message and may cause a GPIB service request.

Up to 75 sets of complete front panel settings can be stored in memory. The memory has a non-rechargeable lithium battery back up for a minimum of 6 months (typically 1 to 2 years). A "low battery" warning will be indicated on the display when the battery voltage drops to 80% of its normal voltage.

## WARNING

This equipment uses a BR-1/2A, 3V lithium battery, that contains less than 0.3 grams of lithium. To prevent the release of a potentially harmful substance, DO NOT RECHARGE, SHORT CIRCUIT, DISASSEMBLE, OR APPLY HEAT TO THE BATTERY. In addition, observe correct polarity when replacing.

## 1.2 ACCESSORIES

Rack mounts for a single instrument, rack mounts for two series 270 instruments side-by-side and instrument slides are available accessories. Refer to paragraph 1.3.13 for details.

## 1.3 SPECIFICATIONS

## 1.3.1 Main Generator Waveforms (Functions)

Programmable sine  $\checkmark$ , triangle  $\checkmark$ , square  $\Box$ , square complement, dc, external width, arbitrary and filtered arbitrary.

## Sine Distortion (THD at 5 Vp-p):

<0.5% 10 mHz to 99.9 kHz.

No harmonics above

- 40 dBc 100 kHz to 999 kHz

- 30 dBc 1 MHz to 12 MHz.

## **Time Symmetry:**

$\pm 1\% \pm 8 \, \text{ns}.$

## **Square Transition Time:**

<15 ns.

## **Square Overshoot:**

<4% at full amplitude.

Triangle Linearity: 99% to 100 kHz.

## 1.3.2 Operational Modes (For All Functions Including ARB)

## Continuous:

Output continuous at programmed frequency or clock rate.

## Triggered:

Output quiescent until triggered by external signal, internal trigger, GPIB trigger or manual trigger, then generates one cycle at programmed frequency or clock rate.

## Gated:

Similar to triggered mode, except that output is continuous for the duration of the gate signal. The last cycle started is completed.

## **Burst:**

Similar to triggered mode, except that the number of cycles produced is programmable.

Count Range: 1 to 1,048,200. Burst Rate: 12 MHz maximum.

## 1.3.3 Operational Modes (ARB Only)

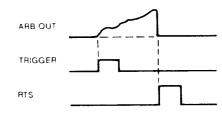

## Triggered ARB with Ramp-to-Start:

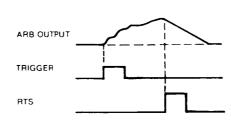

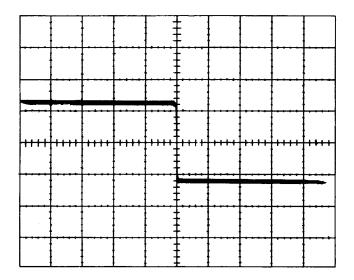

One cycle of ARB waveform is initiated on the trigger input. External RTS signal (at ARB RTS/HOLD IN) causes ARB output to slowly ramp to data value at start address of the ARB waveform. If RTS signal is not received before stop address is reached, RTS is initiated at stop address.

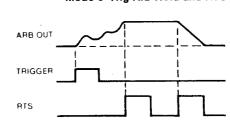

## Triggered ARB with Reset:

Same as Triggered ARB with Ramp-to-Start except the Reset signal (or stop address) causes immediate reset to start address.

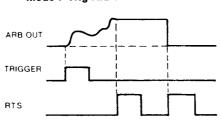

## Triggered ARB with Hold and Triggered Ramp-to-Start:

One cycle of the ARB waveform is initiated on trigger input. Leading edge of Hold signal causes ARB to hold. Second leading edge (Reset signal) causes immediate reset to start. If stop address is reached before Hold signal then stop address causes hold.

## Triggered ARB with Hold and Triggered Reset:

One cycle of ARB waveform is initiated on trigger input. Leading edge of Hold signal causes ARB to hold. Second leading edge (Reset signal) causes immediate reset to start. If stop address is reached before Hold signal, then stop address causes hold.

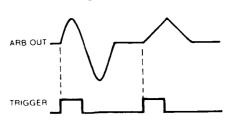

## Single Step:

Same as Continuous mode except when Arbitrary function is selected ARB clock rate is replaced by trigger input so that ARB clock can be supplied externally or with function generator.

## Examine:

When Arbitrary function is selected the output will be voltage (data value) present at address specified on address program. This allows ARB waveform to be examined one point at a time by specifying address of desired point.

## Triggered ARB with Hold on Breakpoint:

ARB waveform is initiated upon trigger input and held at programmed breakpoints. Start and stop addresses are ignored in this mode.

## 1.3.4 Frequency

## Range:

10 mHz to 12 MHz for sine, triangle, square, square complement, >15 MHz for external width. ARB frequency range dependent upon clock rate and block size. Clock rate 267 ns to 267 s.

## **Block Size:**

2 points to 2048 points (option to 8192 points).

## Resolution:

3 digits.

## Accuracy:

$\pm$  2% for non-ARB modes,  $\pm$  0.2% for ARB modes.

## Repeatability (24 hr):

$\pm$  1% for non-ARB modes, 0.01% for ARB modes.

### Jitter:

$\leq 0.1\%$  of period  $\pm 100$  ps

## Control:

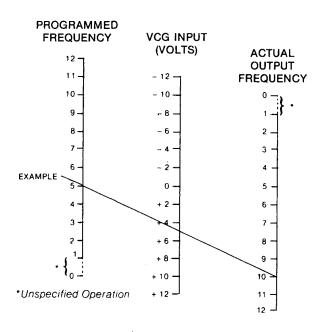

Frequency may be controlled by programmed value or external VCG input.

### Value:

Frequency value is keyboard or GPIB programmable with automatic range selection.

## VCG (Voltage Controlled Generator):

AC or dc input controls frequency. 0.01 to 12V into  $10k\Omega$  for up to 1200:1 frequency change in each of 9 frequency ranges (range must be programmed). Slew rate is limited to  $1Vl\mu$ s.

## 1.3.5 Amplitude

## Range:

0.01 to 10 Vp-p into  $50\Omega$  (0.02 to 20 Vp-p into open circuit) from main output. Absolute peak amplitude plus offset may not exceed 5V into  $50\Omega$  (10V into open circuit).

## Resolution:

3 digits or 10 mV when absolute peak amplitude plus offset > 0.5V; 3 digits or 1 mV when absolute peak amplitude plus offset  $\le 0.5V$ .

## Accuracy:

- $\pm$  2% of programmed value and:

- $\pm 5$  mV for 0.1 to 1V (peak amplitude + offset < 0.5V)

- $\pm$  20 mV for 1.01 to 10V,

- ±50 mV for all other.

## Repeatability (24 hr):

$\pm 1\% \pm 10 \text{ mV}.$

## Flatness (at 5 Vp-p):

0.1 dB to 100 kHz, 1.5 dB to 12 MHz.

## 1.3.6 Offset

## Range:

DC or offset programmable from -5V to +5V into  $50\Omega$  (-10V to +10V into open circuit). Absolute peak amplitude plus offset may not exceed 5V into  $50\Omega$  (10V into open circuit).

## Resolution:

3 digits or 10 mV when absolute peak amplitude plus offset >0.5V, 3 digits or 1 mV when absolute peak amplitude plus offset  $\leq 0.5V$ .

## Accuracy:

±40 mV in dc function.

## Repeatability (24 hr):

$\pm 20 \text{ mV}.$

## 1.3.7 Outputs

**Function Output:** Source of primary waveforms. Programs control provides:

Output on,  $50\Omega$  source impedance;

Output off, high  $Z (> 500k\Omega)$ ;

Output off, low Z (terminated in approximately  $50\Omega$ ).

## Protection:

Output protected to 140 Vac or 200 Vdc without internal damage.

## Main Sync Output:

Sync signal is at programmed frequency and TTL level.

Level:

$\leq 0.4 \text{V to } \geq 2.4 \text{V into } 50\Omega$ ,

$\leq$  0.8V to  $\geq$  4.8V into open circuit.

## Source Impedance:

$50\Omega$ .

## Timing:

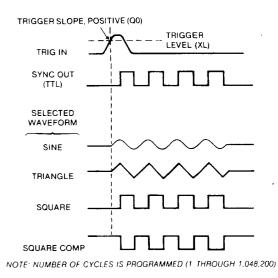

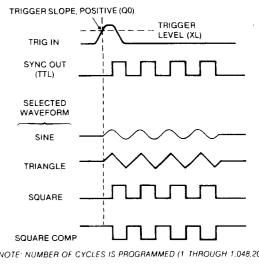

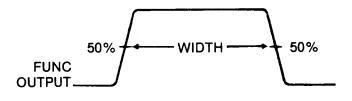

Concurrent with function output in square; lags sine and triangle by 90°.

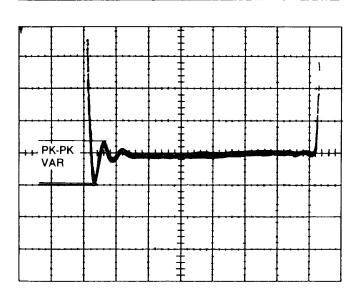

## Over/Undershoot:

<10% into  $50\Omega$ .

## Protection:

Output protected from short circuit to any voltage between  $\pm 15$  Vdc.

## **Arb Sync Output:**

5 Vp-p into  $600\Omega$ , programmable phase control. RCL 4000 initiates positive ARB sync; RCL 4001 initiates negative ARB sync.

## Source Impedance:

$600\Omega$ .

## Protection:

Output protected from short circuit to any voltage between ± 15V.

## 1.3.8 Inputs

## **External Trigger:**

Trigger of input circuit is programmable for a + or - signal slope and required threshold level.

Level: -10 to +10V. Resolution: 20 mV. Accuracy:  $\pm 500$  mV. Input Impedance:  $10 \text{ k}\Omega$ .

Maximum Trigger Rate: 12 MHz (15 MHz for External

Width function).

Minimum Trigger Width: 20 ns.

Minimum Amplitude: 500 mVp-p to 1 MHz, 1 Vp-p to

15 MHz.

Protection: Input protected to  $\pm 50V$ .

## VCG in:

Voltage control of generator frequency. See Frequency.

Range: 0.01 to 12V. Impedance:  $10k\Omega$ .

Protection: Input protected to  $\pm 50V$ .

## ARB RTS/HOLD Input:

Trig input and RTS/Hold Input are logically internally common. Having two inputs provides processing for independently generated trigger and RTS/hold signal. (NOTE: Inputs are buffered prior to being logically "OR" ed together.)

Protection: Input protected from short circuit to any

voltage between  $\pm 15V$ .

## 1.3.9 Internal Trigger

## **Non-ARB Functions**

Range: 3.75 mHz to 3.75 MHz.

Resolution: 4 digits. Accuracy: 0.2%.

## **ARB Functions**

Range: 10 mHz to 3.75 MHz.

Resolution: 3 digits. Accuracy: 2%.

## 1.3.10 ARB Characteristics

## **Horizontal Resolution:**

2048 points standard; 8192 points optional.

## **Vertical Resolution:**

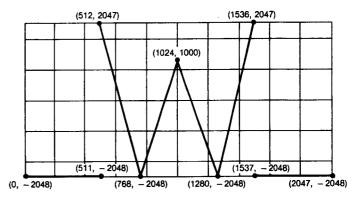

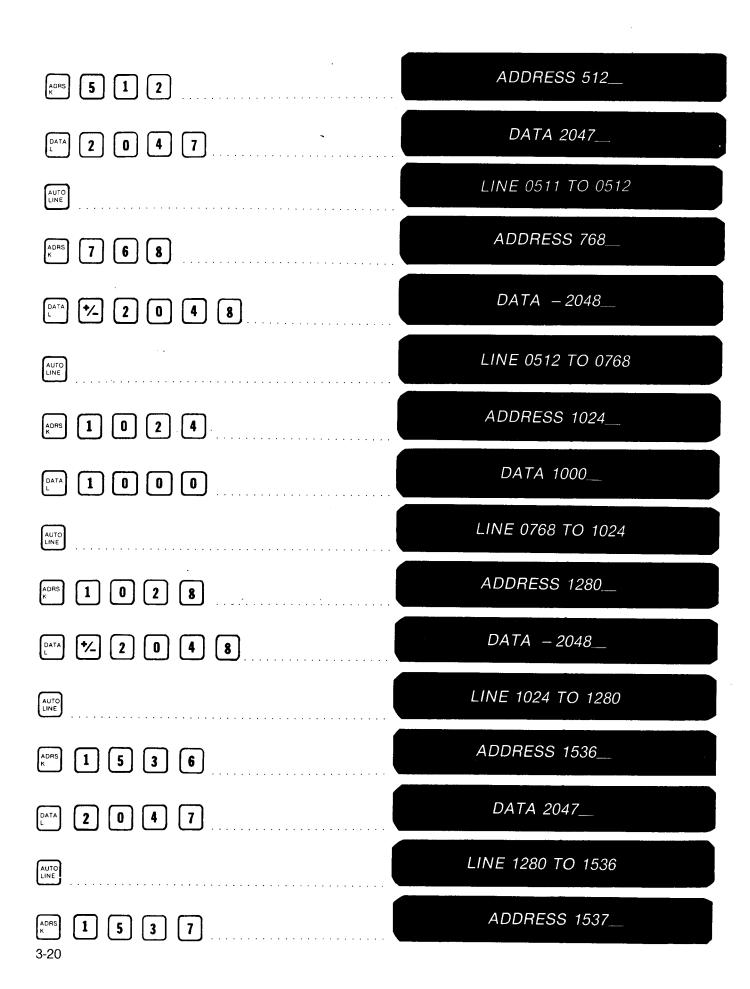

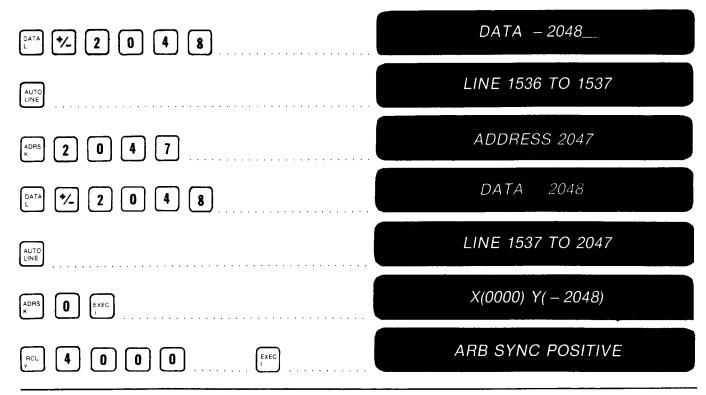

12 bits (-2048 to +2047).

## Auto-Line:

Allows a straight line to be drawn between the last two data points specified.

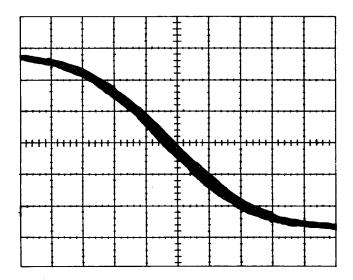

## Programmable Filter on ARB Waveform:

Non-Filtered Arb waveform: Settling time 1.5  $\mu$ s. Filtered Arb waveform: Settling time 1 ms.

## Programmable Ramp-to-Start Rate:

Fast: approximately 5 ms/bit; Slow: approximately 20 ms/bit.

## Programmable 3 digit ARB Clock:

Period ranges from 267 s to 267 ns with 0.2% accuracy.

## 1.3.11 GPIB Programming

IEEE 488-1978 compatible. Nonisolated. Double buffered.

Address: 0-30, keyboard or internal switch selectable. Internal switch can lock out keyboard selection. Power-up address is internal setting.

Subsets: SH1, AH1, T6, TE0, L4, SR1, RL1, PP0, DC1, C0, E2.

## Interface Timing:

| Frequency   | 16 ms          |

|-------------|----------------|

| Amplitude   | 13 ms          |

| Offset      | 14 ms          |

| Mode        | 6 ms           |

| Function    | 5 ms           |

| INT/EXT     | 5 ms           |

| Execute     | 20 ms to 4 sec |

| Store       | 11 ms          |

| Output      | 10 ms          |

| Slope       | 5 ms           |

| Burst Count | 10 ms          |

| Rate        | 35 ms          |

| Recall      | 185 ms         |

| Reset       | 185 ms         |

| Start       | 20 ms          |

| Stop        | 20 ms          |

| GET Mode    | 5 ms to 4 sec  |

| ADRS        | 10 ms          |

| DATA        | 15 ms          |

| AUTO LINE   | 20 ms to 2 sec |

## 1.3.12 General

## **Stored Settings:**

Non-volatile memory for 75 stored settings.

## **Environmental:**

Temperature Range:  $25^{\circ}\text{C} \pm 10^{\circ}\text{C}$  for specified operation; operates  $0^{\circ}\text{C}$  to  $50^{\circ}\text{C}$ ;  $-50^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  for storage.

Altitude: Sea level to 10,000 ft for operation. Sea level to 40,000 ft for storage.

Relative Humidity: 95% at 20°C at sea level (non-condensing).

Warm-up Time: 20 minutes for specified operation.

## **Dimensions:**

21.7 cm (8.54 in) wide (half-rack); 13.3 cm (5.25 in) high; 39.4 cm (15.5 in) deep.

## Weight:

5.9 kg (13 lb) net, 7.2 kg (16 lb) shipping.

## Power:

90 to 105, 108 to 126, 198 to 231, or 216 to 252 volts rms; 48 to 66 Hz, 1 phase; < 40 watts.

## **1.3.13 Options**

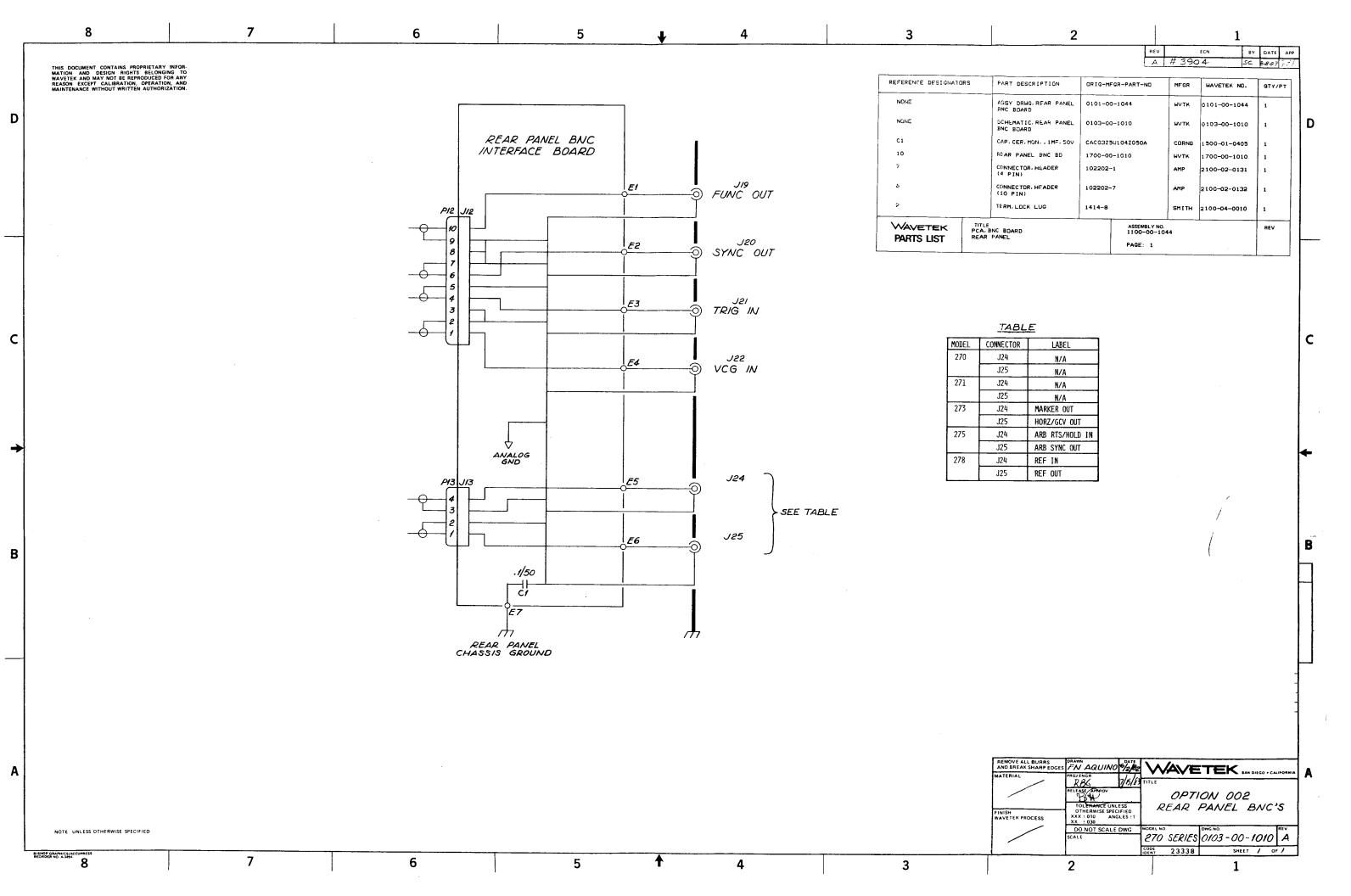

## 002: Rear Panel Connectors

Front panel BNC connectors relocated to rear panel.

## 004: Extended Block Size

Extends arbitrary waveform memory block size to 8192 points.

## 1.3.14 Accessories

## Style 12: Single Rack Adapter Kit

Allows right or left mounting in a standard 19 inch rack. 5 1/4 inches high.

## Style 13: Dual Rack Adapter Kit

Allows any 270 series instrument to be mounted sideby-side in a standard 19 inch rack. 5 1/4 inches high.

## **Rack Slides**

## SECTION AND INTERFACE

## 2.1 MECHANICAL INSTALLATION

After unpacking the instrument, visually inspect all external parts for possible damage to connectors, surface areas, etc. If damage is discovered, file a claim with the carrier who transported the unit. The shipping container and packing material should be saved in case reshipment is required.

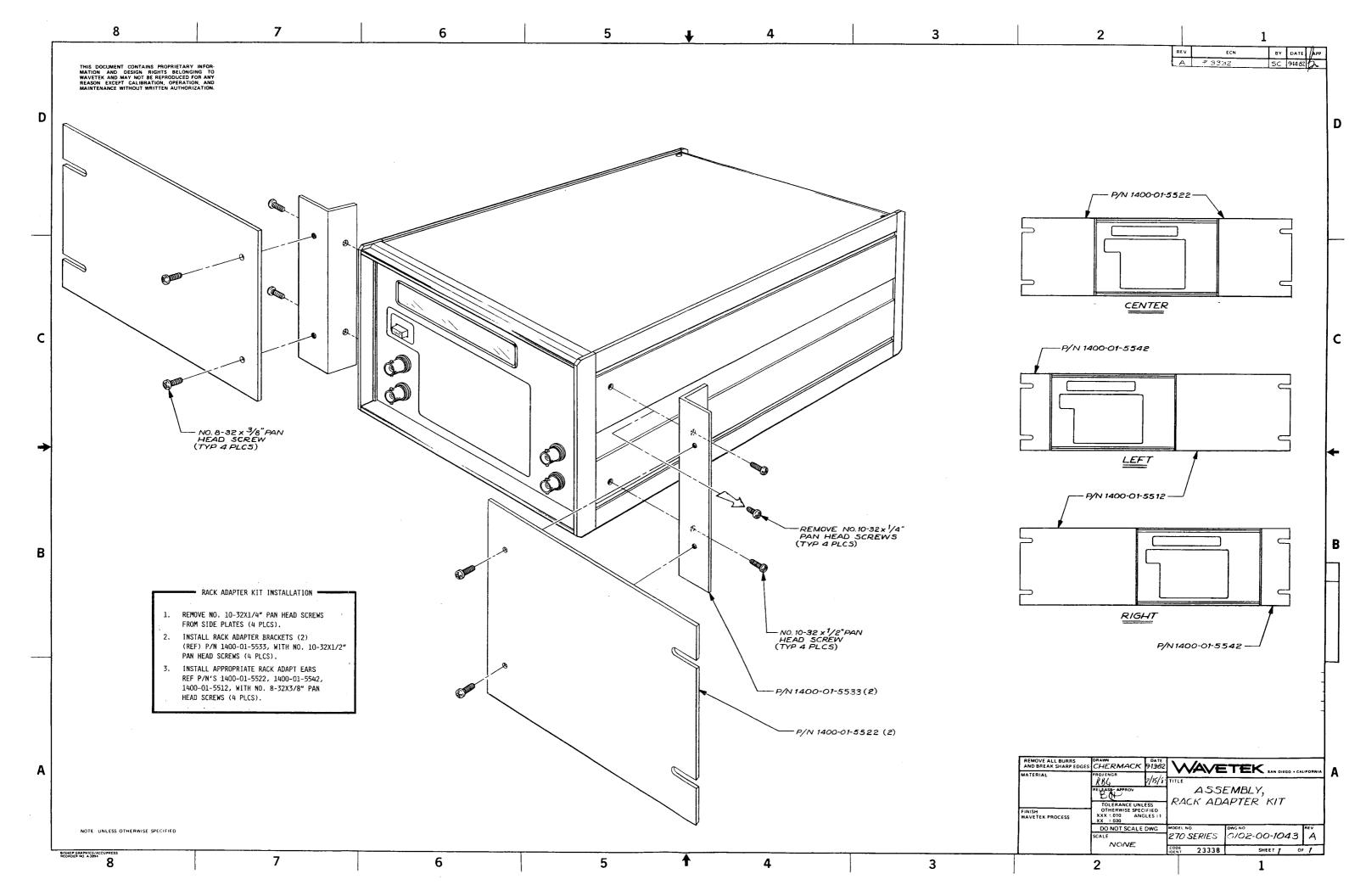

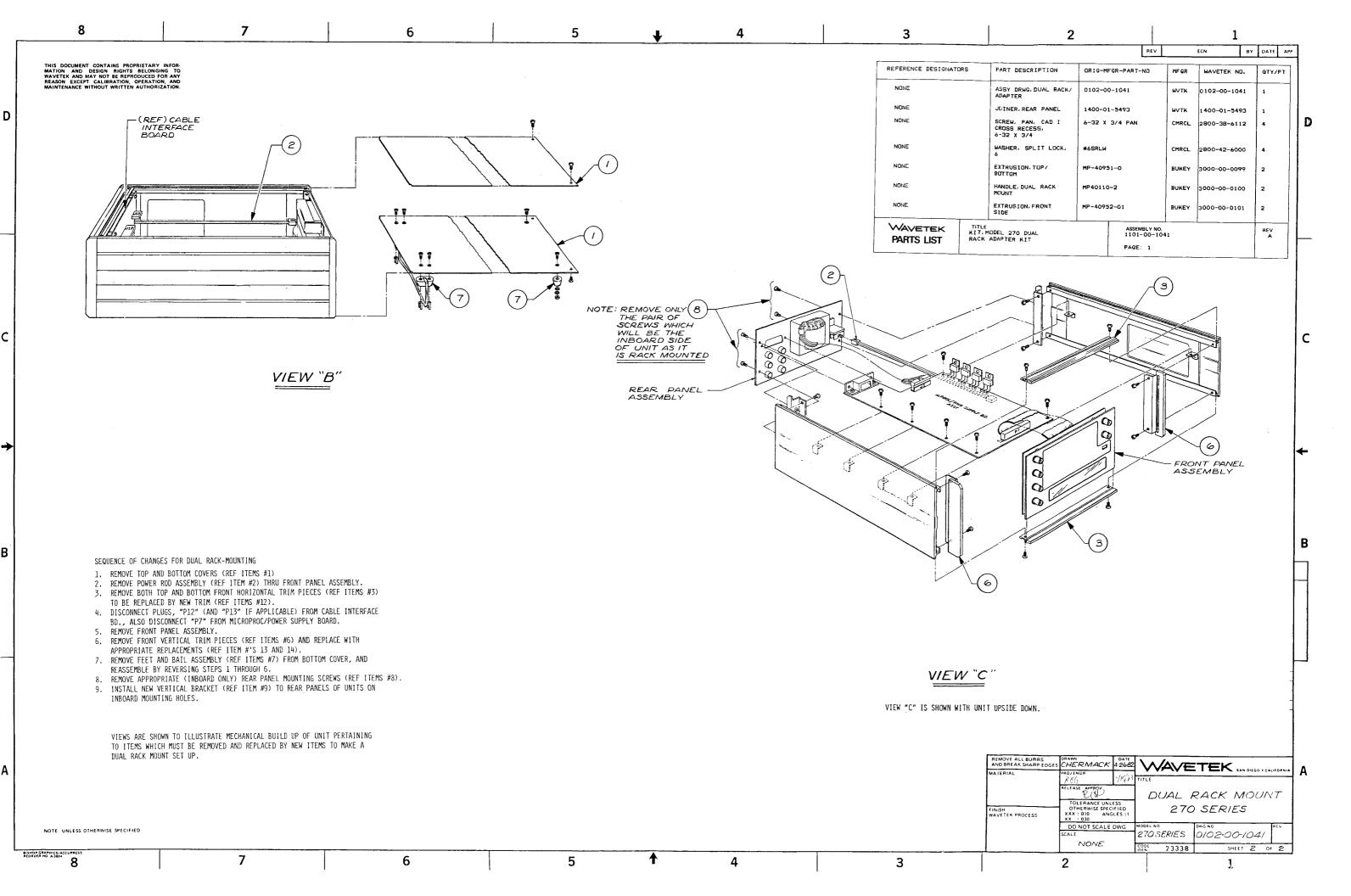

The generator can be used as a bench instrument or rack mounted. The 275 can be converted to rack mounts in the field by using the following kits.

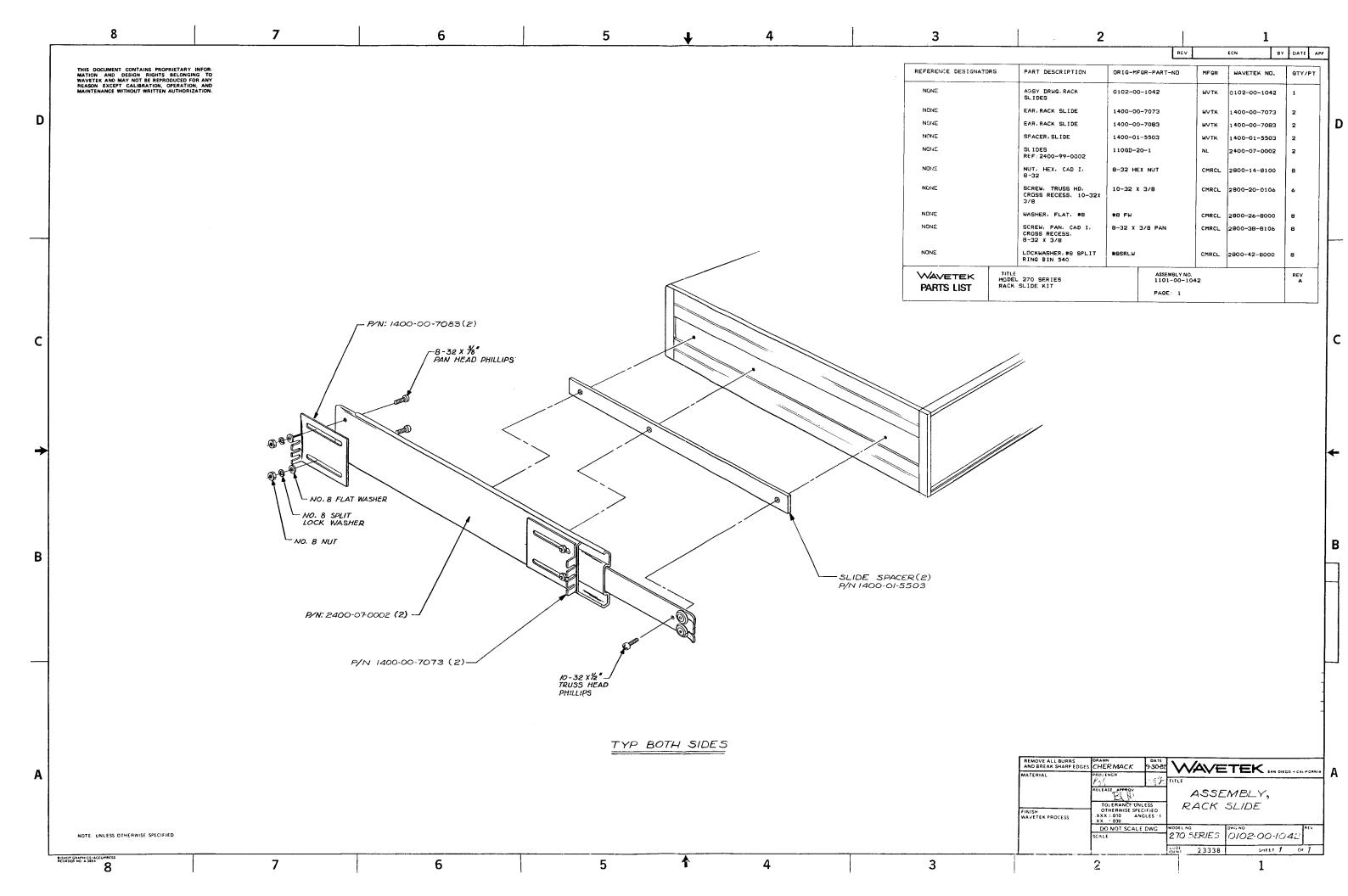

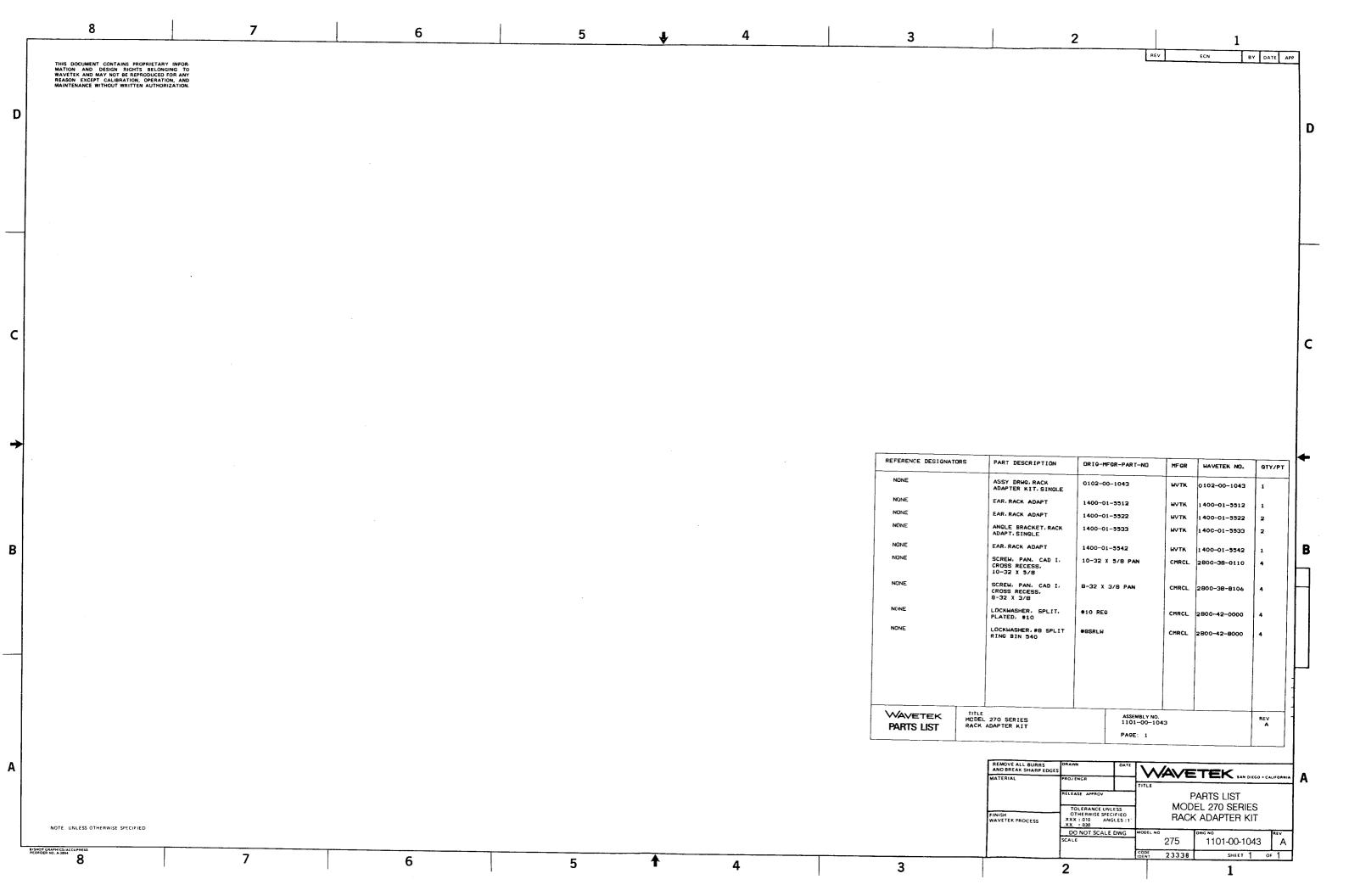

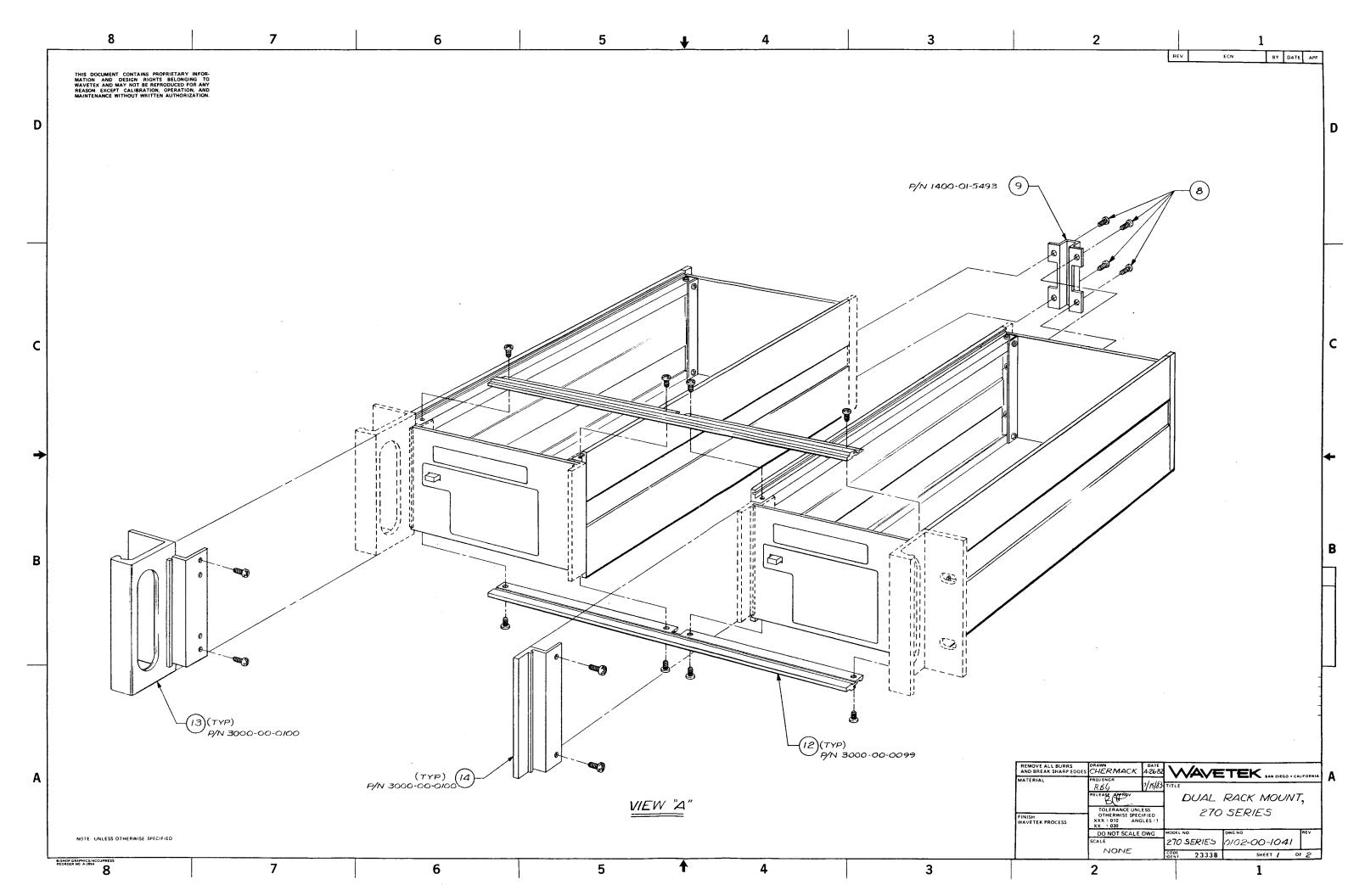

| Rack Mount<br>Kit                                   | Part<br>Number | Reference<br>Drawing |

|-----------------------------------------------------|----------------|----------------------|

| Single<br>Instrument<br>(left or right<br>mounting) | 1101-00-1043   | 0102-00-1043         |

| Dual<br>Instruments                                 | 1101-00-1041   | 0102-00-1041         |

| Rack Slides                                         | 1101-00-1042   | 0102-00-1042         |

## NOTE

The rack slides can only be used with dual rack mounted instruments.

Whether used on a bench or in a rack, ensure that there is no impedance to air flow at any surface of the instrument. Before rack mounting, it may be desirable to perform the initial checkout (paragraph 3.1) to verify operation of all functions.

## 2.2 ELECTRICAL INSTALLATION

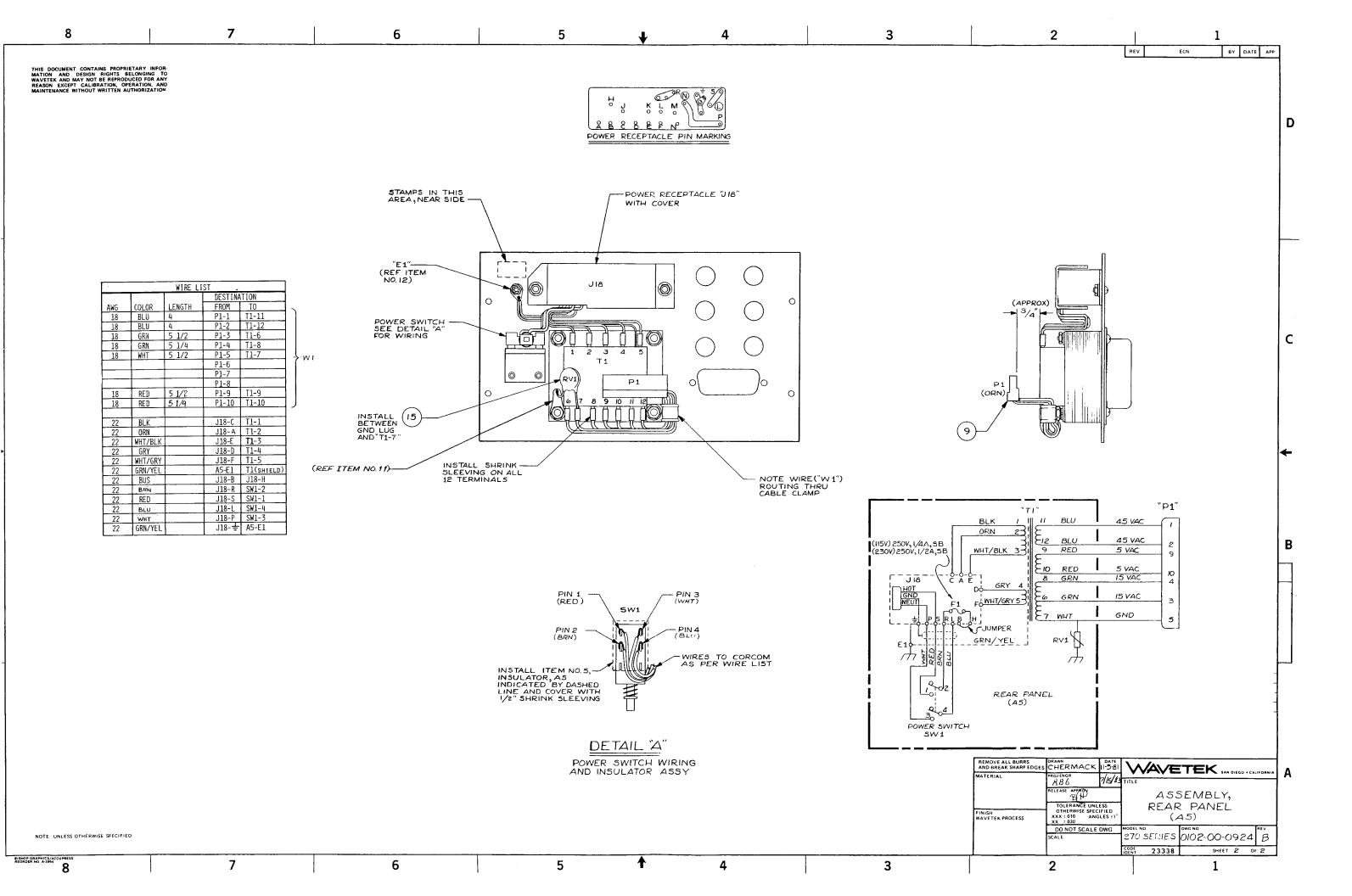

## 2.2.1 Power Connection

## NOTE

Unless otherwise specified at the time of purchase, this instrument was shipped from the factory with the power transformer connected for operation on a 120 Vac line supply and with a ½ amp fuse.

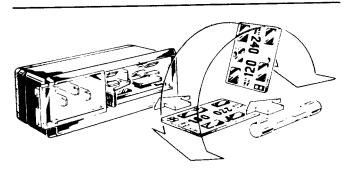

Conversion to other input voltages requires a change in rear panel fuse holder voltage card position and fuse (figure 2-1) according to the following procedure.

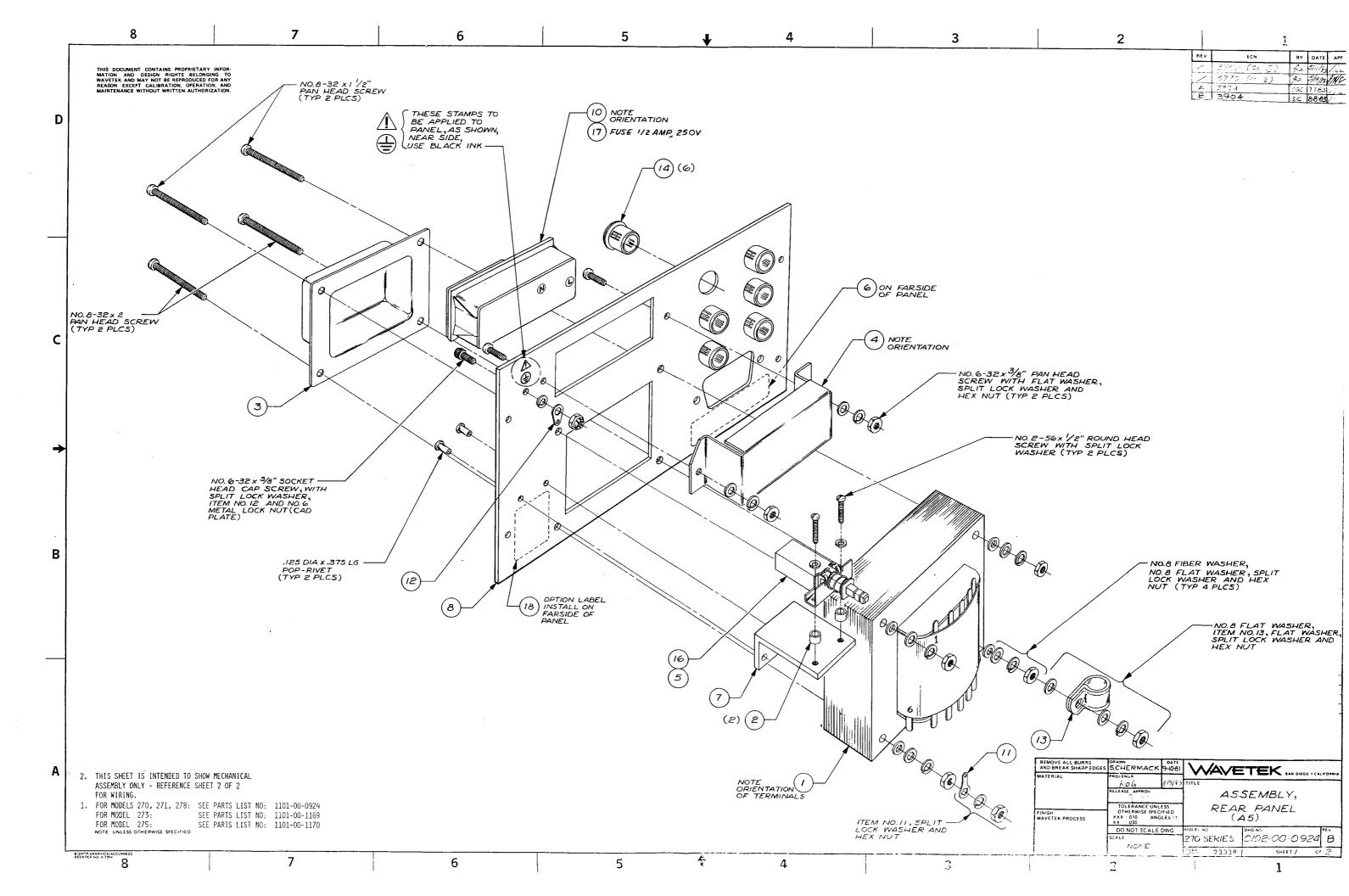

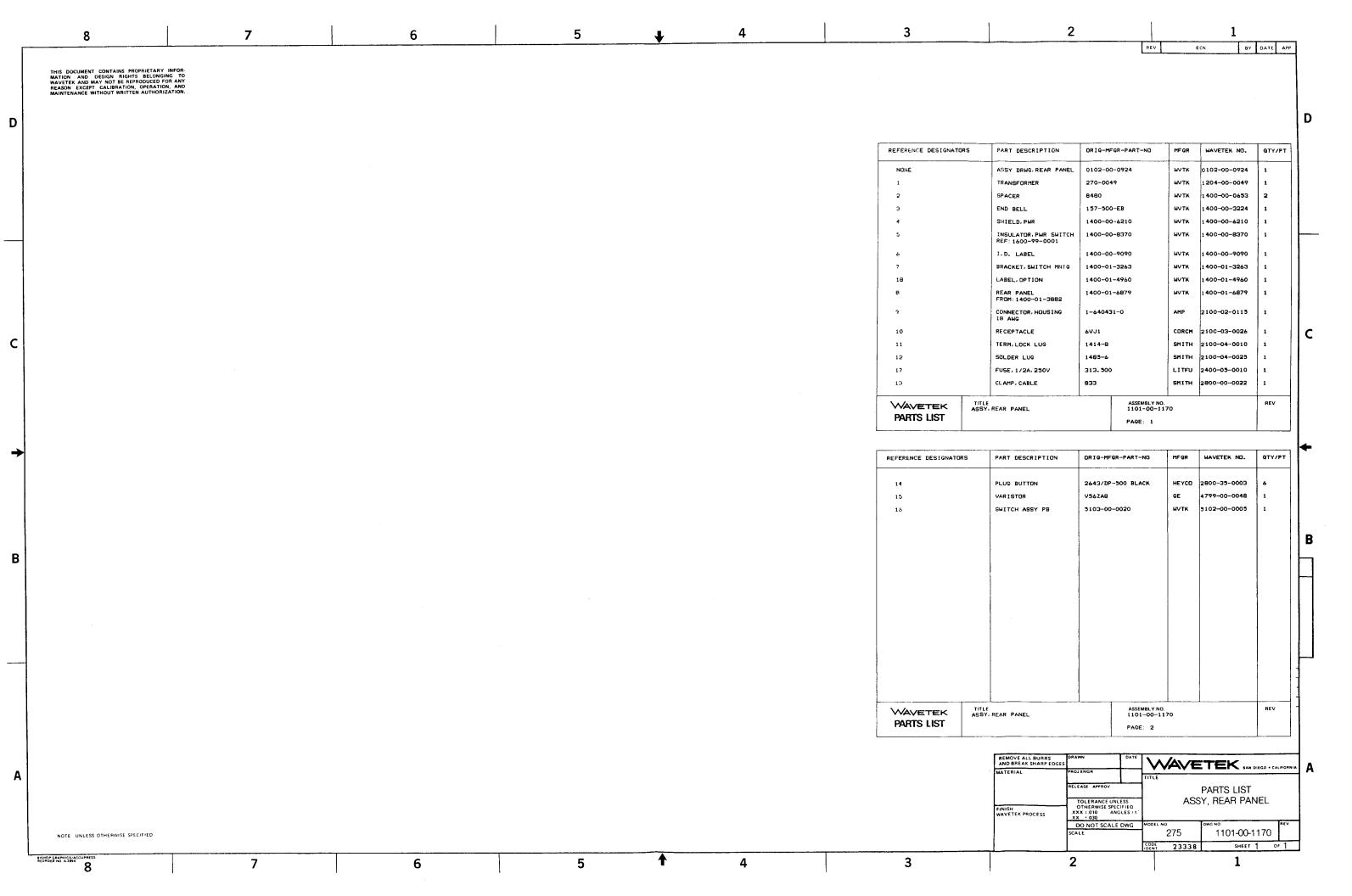

Figure 2-1. Voltage Selector and Fuse

- Disconnect the power cord at the instrument, open fuse holder cover door and rotate fuse-pull to left to remove the fuse.

- 2. Remove the small printed circuit board and select operating voltage by orienting the printed circuit board to position the desired voltage to the top left side. Push the board firmly into its module slot.

| Card Position | Input Vac  | Fuse    |

|---------------|------------|---------|

| 100           | 90 to 105  | ½ amp   |

| 120           | 108 to 126 | 1/2 amp |

| 220           | 198 to 231 | 1/4 amp |

| 240           | 216 to 252 | 1/4 amp |

- 3. Rotate the fuse-pull back into the normal position and insert the correct fuse into the fuse holder. Close the cover door.

- 4. Connect the ac line cord to the mating connector at the rear of the unit and the power source.

## 2.2.2 Signal Connections

## NOTE

Use RG58U 50 $\Omega$  or equivalent 50 $\Omega$  coaxial cables equipped with BNC connectors to distribute signals.

Instrument BNC connectors are:

**TRIG IN.** Acceptable trigger level and slope are programmable;  $-10 \text{ k}\Omega$  impedance.

**MAIN SYNC OUT.** 0V to >2.4V into50 $\Omega$  impedance; >4.8V open circuit.

**FUNC OUT.** Up to 10 Vp-p into  $50\Omega$  impedance; up to 20 Vp-p into >50 k $\Omega$  impedance.

**VCG IN.** 0.01 to 12V; 10  $k\Omega$  impedance.

**ARB SYNC OUT.** 0V to 10V pulse into  $600\Omega$  impedance.

**ARB RTS/HOLD IN.** TTL input, 1 k $\Omega$  impedance. Used in Arb function only. RTS/HOLD and TRIG IN are internally OR'd in RTS modes.

Signal ground may be floated up to  $\pm 42$  volts with respect to chassis ground. Be aware that all signal grounds are common and must all be floated together.

## 2.2.3 GPIB Connections

The GPIB I/O rear panel pin connections and signal names are given in table 2-1. The panel connector is an Amphenol 57-10240 or equivalent and connects to a GPIB bus cable connector (available from Wavetek in 1 and 2 meter lengths).

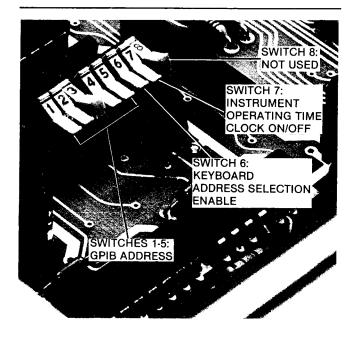

### 2.2.4 GPIB Address

For instruments on the General Purpose Interface Bus (GPIB), ensure that the instrument GPIB address is correct. The GPIB address can be changed by the internal switch (for access, remove the bottom cover, see figure 2-2) or the front panel GPIB ADRS key (e.g., ADRS 4 EXEC). The switch sections are labeled from 1 through 5 and their OFF position noted (OFF = Binary "O" in table 2-2). To verify the address, press ADR on the front panel. The device number (decimal) will be displayed. Upon power-up, the address is always that of the internal switch.

Table 2-1. GPIB Data In/Out

| Pin                        | Signal     |   |

|----------------------------|------------|---|

| 1                          | DIO1       | _ |

|                            | DIO2       |   |

| 3                          | DIO3       |   |

| 4                          | DIO4       |   |

| 2<br>3<br>4<br>5<br>6<br>7 | EOI        |   |

| 6                          | DAV        |   |

| 7                          | NRFD       |   |

| 8                          | NDAC       |   |

| 9                          | IFC        |   |

| 10                         | SRQ        |   |

| 11                         | ATN        |   |

| 12                         | Chassis    |   |

|                            | Ground     |   |

| 13                         | DIO5       |   |

| 14                         | DIO6       |   |

| 15                         | DIO7       |   |

| 16                         | DIO8       |   |

| 17                         | REN        |   |

| 18                         | )          |   |

| 19                         |            |   |

| 20                         |            |   |

| 21                         | Signal Gnd |   |

| 22                         |            |   |

| 23                         |            |   |

| 24                         |            |   |

Figure 2.2 GPIB Address Selector Switch

Table 2-2. GPIB Address Codes

|                                                                   | ASCII                              |                                 |                                                               |                                                |                                                | ch<br>ior                            | 1                                                   | Hex<br>decir                                                               |                                                                            |

|-------------------------------------------------------------------|------------------------------------|---------------------------------|---------------------------------------------------------------|------------------------------------------------|------------------------------------------------|--------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Device                                                            | Listen                             | Talk                            | 1                                                             | 2                                              | 3                                              | 4                                    | 5                                                   | Listen                                                                     | Talk                                                                       |

| 0<br>1<br>2<br>3<br>4<br>5<br>6                                   | (space)<br>!<br>.;<br>#<br>\$<br>% | @<br>A<br>B<br>C<br>D<br>E<br>F | 0<br>1<br>0<br>1<br>0<br>1                                    | 0<br>0<br>1<br>1<br>0<br>0                     | 0<br>0<br>0<br>0<br>1<br>1                     | 0 0 0 0 0                            | 0 0 0 0 0 0                                         | 20<br>21<br>22<br>23<br>24<br>25<br>26                                     | 40<br>41<br>42<br>43<br>44<br>45<br>46                                     |

| 7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | , ( ) * + , — • / 0 1 2 3          | G H - J K L M Z O P G R S       | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | 100110011                                      | 10000011110000                                 | 0 1 1 1 1 1 1 1 0 0 0 0              | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 27<br>28<br>29<br>2A<br>2B<br>2C<br>2D<br>2E<br>2F<br>30<br>31<br>32<br>33 | 47<br>48<br>49<br>4A<br>4B<br>4C<br>4D<br>4E<br>4F<br>50<br>51<br>52<br>53 |

| 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30    | 4 5 6 7 8 9 : ; < = >              | T U V W X Y Z [ \ \ ] ^         | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0                     | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0 | 1<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>1 | 1 1 1 1 1 1 1 1 1 1                                 | 34<br>35<br>36<br>37<br>38<br>39<br>3A<br>3B<br>3C<br>3D<br>3E             | 54<br>55<br>56<br>57<br>58<br>59<br>5A<br>5B<br>5C<br>5D<br>5E             |

NOTE

Address 31 is not allowed.

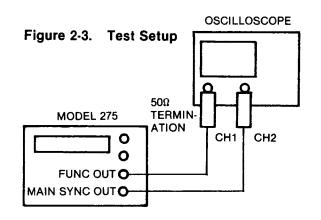

## 2.2.5 Initial Checkout and Operation Verification

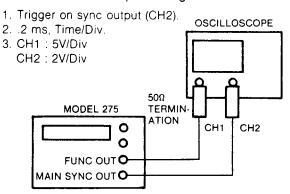

Make the equipment setup as shown in figure 2-3 and perform the steps in table 2-3 to verify Wavetek 275 operation. If further explanations are required, refer to figure 3-1 and table 3-1.

Table 2-3. Initial Checkout

| Step | Test            | Tester & Setup | Program                                                                      | Desired Results                                                                                                          |

|------|-----------------|----------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 1    | Wake-up State   |                | Power: ON                                                                    | Display: All segments, decimal points and commas light up for 1 second.                                                  |

| 2    | Wake-up Status  |                | Press STAT key.                                                              | Display (changes automatically): FREQ 1 KHz AMPLITUDE 5V OFFSET 0V MODE CONTINUOUS (0) FUNC SINE (0) BURST COUNT 2 CLK 1 |

| 3    | Status Search   |                | STAT                                                                         | Status display sequence stops.                                                                                           |

| 4    |                 |                | 1                                                                            | Status progresses forward.                                                                                               |

| 5    |                 |                |                                                                              | Status progresses backward.                                                                                              |

| 6    |                 |                | STAT                                                                         | Status display automatic sequence continues.                                                                             |

| 7    | Beeper Test.    |                | Press FREQ key a few times.                                                  | Beeper sounds every time key is pressed.                                                                                 |

| 8    |                 |                | Press I, then FREQ key a few times.                                          | Beeper is silent.                                                                                                        |

| 9    |                 |                | <b>√</b>                                                                     | Beeper enabled                                                                                                           |

| 10   | Command Recall. |                | Press each of the 6 keys in the MAIN generator section 4 times then CMD RCL. | Strings of characters shown on display. Characters are the ones shown on lower left of each key                          |

| 11   |                 |                | Press → then ←.                                                              | Moves characters right then left 4 at a time.                                                                            |

Table 2-3. Initial Checkout

| Step | Test                                                                    | Tester & Setup                                                                                                                                               | Program                   | Desired Results                                                                                                                                                                                               |

|------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12   | GPIB Address and<br>Status.                                             |                                                                                                                                                              | ADRS 1 EXEC then 30 EXEC. | Display: GPIB ADRS 1 then<br>GPIB ADRS 30.                                                                                                                                                                    |

| 13   | Quality Assurance<br>Procedure.                                         | Connect Wavetek 275<br>and oscilloscope as<br>shown in figure 2-3.<br>Scope setting: CH1<br>2V/div; horizontal<br>0.2 ms/div; CH2 2V/div;<br>trigger on CH2. | Press: RCL 2000 EXEC.     | Display: (0) BEGIN QA PROC.<br>Scope: CH1, 5 Vp-p 1 kHz sine<br>wave. CH2, 2.5 Vp-p 1 kHz<br>square wave                                                                                                      |

| 14   | Frequency: Exercises Each Frequency Bit and the Sine Wave Function.     |                                                                                                                                                              | Press: CURSOR 1 once.     | Display: (1) FREQUENCY. Scope: CH1, 5 Vp-p sine wave continuously sweeping from 1 kHz to 10 kHz. CH2, 2.5 Vp-p square wave synchronous with CH1.                                                              |

| 15   | Amplitude: Exercises Each Amplitude Bit and the Triangle Wave Function. |                                                                                                                                                              | Press: CURSOR † once.     | Display: (2) AMPLITUDE. Scope: CH1, 1 kHz triangle wave, amplitude continuously increases from 1V to 10 Vp-p. CH2, 2.5 Vp-p square wave synchronous with CH1.                                                 |

| 16   | Offset: Exercises Each<br>DC Offset Bit and<br>Square Function.         |                                                                                                                                                              | Press: CURSOR 1 once.     | Display: (3) OFFSET. Scope:<br>CH1, 1 Vp-p square wave. DC<br>offset continuously increases<br>from -4V to +4V. CH2,<br>2.5 Vp-p square wave syn-<br>chronous with CH1.                                       |

| 17   | Trigger Circuit.                                                        | Trigger Scope on CH1.                                                                                                                                        | Press: CURSOR † once.     | Display: (4) TRIGGER. Scope:<br>CH1, 500 Hz 5 Vp-p square<br>wave. CH2, 2.5 Vp-p 100 μs<br>pulse, delayed 50 μs relative to<br>positive edge of CH1 waveform.                                                 |

| 18   | Gate Circuit.                                                           |                                                                                                                                                              | Press: CURSOR 1 once.     | Display: (5) GATE. Scope: CH1, 500 Hz 5 Vp-p square wave. CH2, 2.5 Vp-p pulse burst, six 100 µs pulses.                                                                                                       |

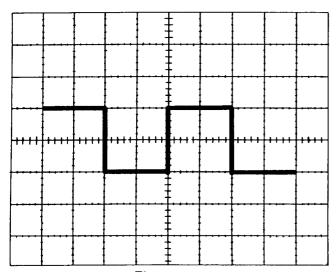

| 19   | Burst Circuit.                                                          |                                                                                                                                                              | Press: CURSOR † once.     | Display: (6) BURST. Scope: CH1, 5 Vp-p pulse, fixed repetition rate of 2 ms, variable width 1.6 ms to 250 μs. CH2, pulse train of 100 μs wide pulses, 2.5 Vp-p. Number of pulses per train steps from 9 to 2. |

| 20   |                                                                         |                                                                                                                                                              | Press: CURSOR 1 once.     | Display: (7) END QA PROC.<br>Scope: CH1, 5 Vp-p pulse,<br>250 μs wide, repetition rate<br>2 ms. CH2, burst of two 100 μs<br>pulses, burst repetition rate<br>2 ms.                                            |

## SECTION OPERATION

## 3.1 INTRODUCTION TO OPERATION

The Wavetek 275 may be operated either locally, from the front panel keyboard, or remotely, via the GPIB (General Purpose Interface Bus). This manual presents local operation first, then additional information required for remote operation. Users who plan to control the instrument remotely should read both sections.

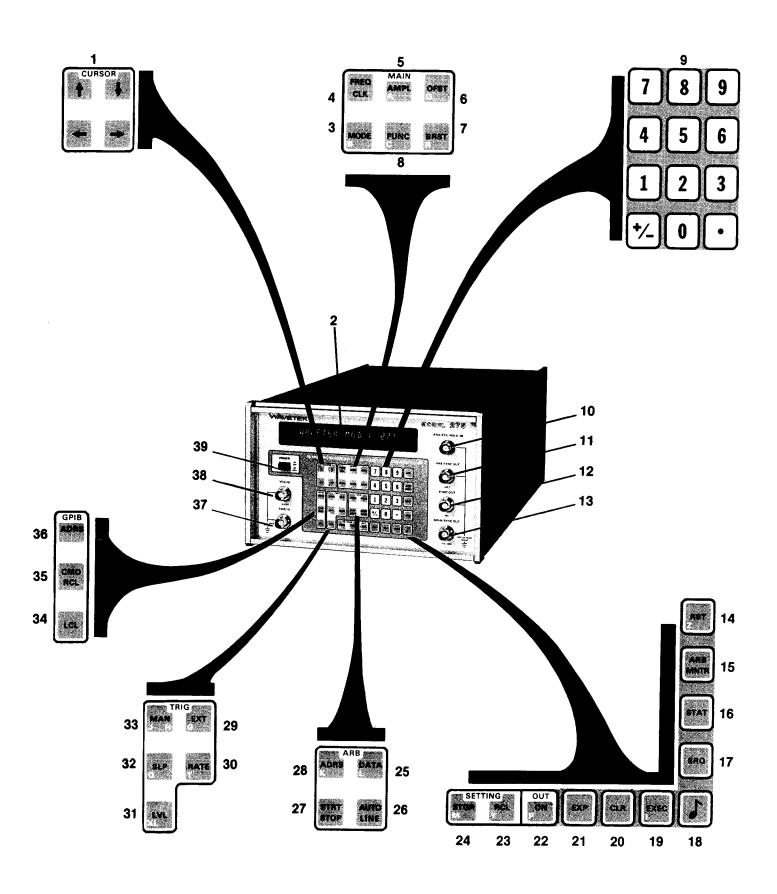

## 3.2 FRONT PANEL CONTROLS AND CONNECTORS

The front panel contains the power switch, keyboard, display and (unless option 002, rear panel connectors, has been specified) the BNC signal connection jacks. Figure 3-1 shows the location of all front panel controls and connectors. Table 3-1, which is keyed to the numeric identifiers in Figure 3-1, briefly lists the purpose of each control or connector for quick reference. Further information on the controls is contained in section 3.5, LOCAL OPERATION.

## 3.3 POWER-UP

When ac power is applied to the instrument, the microprocessor performs internal checks and initializes the internal circuitry. During the first second, the microprocessor performs a display test by lighting all display segments. The display then indicates

## BUSY, PLEASE WAIT

during the remainder of the initialization. When the initialization is complete,

## WAVETEK MODEL 275

is displayed. During power-up, all parameters are set to default values.

Table 3-1. Controls and Connectors

| Key<br>Ref<br>No. | Control or<br>Connector | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | CURSOR                  | <ul> <li>and → position the cursor to any numerical digit (indicated by the flashing digit on the display). † and ‡ increment or decrement codes, storage addresses or the flashing digit (features carry action) of a parameter value.</li> <li>and → are also used to move a displayed program string (CMD RCL) to the left or right in increments of 4 characters. Because † and ‡ employ an automatic execute, the instrument output is instantly changed with cursor action.</li> </ul> |

| 2                 | DISPLAY                 | Twenty character readout (both manually and remotely accessible). Advises operator of parameters and values, errors, warnings and GPIB activity. Also displays programming strings.                                                                                                                                                                                                                                                                                                          |

Figure 3-1. Controls and Connectors

Table 3-1. Controls and Connectors (Continued)

| Key<br>Ref<br>No. | Control or<br>Connector | Description                                                                                                                                                                                                                                                                                                                                            |                         |

|-------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 3                 | MODE (B)                | Displays main generator and Arb generator modes and enables chang There are eleven modes.                                                                                                                                                                                                                                                              |                         |

|                   |                         | MODE                                                                                                                                                                                                                                                                                                                                                   | CODE                    |

|                   |                         | Continuous                                                                                                                                                                                                                                                                                                                                             | 1 0                     |