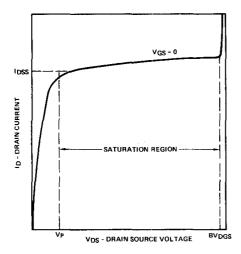

By itself, I<sub>DSS</sub> merely refers to the drain current that will flow for any applied  $V_{\mbox{DS}}$  with the gate shorted to the source. However, when a particular value for V<sub>DS</sub> is given, equal to or greater than V<sub>P</sub> (see Figure 10), I<sub>DSS</sub> indicates the drain saturation current at zero gate voltage. Some FET data sheets label I<sub>DSS</sub> for V<sub>DS</sub> greater than V<sub>P</sub> as I<sub>D(on)</sub>.

FET Characteristic at V<sub>GS</sub> = 0 Figure 10

## $V_{GS(off)}$ - Gate-Source Cutoff Voltage

The resistance of a semiconductor channel is related to its physical dimensions by  $R = \rho L/A$ , where

$\rho$  = resistivity

L = length of the channel

A = W x T = cross-sectional area of channel

In the usual FET structure, L and W are fixed by device geometry, while channel thickness T is the distance between the depletion layers. The position of the depletion layer can be varied either by the gate-source bias voltage or by the drain-source voltage. When T is reduced to zero by any combination of VGS and VDS, the depletion layers from the opposite sides come in contact, and the a-c or incremental channel resistance,  $\mathbf{r}_{DS},$  approaches infinity. As earlier noted, this condition is referred to as "pinch-off" or "cutoff" because the channel current has been reduced to a very thin sheet, and current will no longer be conducted. Further increases in V<sub>DS</sub> (up to the junction reverse-bias breakdown) will cause little change in ID. Accordingly, the pinch-off region is also referred to as the pentode or "constant-current" region.

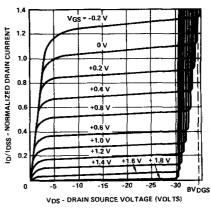

In Figure 10, pinch-off occurs with  $V_{GS} = 0$ . In Figure 11, VGS controls the magnitude of the saturated ID, with increases in V<sub>GS</sub> resulting in lower values of constant I<sub>D</sub>, and smaller values of V<sub>DS</sub> necessary to reach the "knee" of the curve. The current scale in Figure 11 has been normalized to a specific value of IDSS.

FET ID vs VD Output Characteristics Figure 11

The knee of the curve is important to the circuit designer because he must know what minimum V<sub>DS</sub> is needed to reach the pinch-off region with  $V_{GS} = 0$ . When appropriate bias voltage is applied to the gate, it will pinch off the channel so that no drain current can flow; VDS has no effect until breakdown occurs. The specific amount of V<sub>GS</sub> that produces pinch-off is known as the gate-source cutoff voltage  $V_{GS(off)}$ .

## V<sub>GS(off)</sub> Test Procedure

Although the magnitude of V<sub>GS(off)</sub> is equal to the pinchoff voltage, Vp, defined by the pinch-off knee in Figure 10, rapid curvature in the area makes it difficult to define any precise point as Vp. Taking a second derivative of VDS/ID would yield a peak corresponding to the inflection point at the knee, which approximates Vp. However, this is not a simple measurement for production quantities of devices. A better measure is to approach the cutoff point of the  $I_{\mbox{\scriptsize D}}$ versus V<sub>GS</sub> characteristic. This is easier than trying to specify the location of the knee of the ID versus VDS output characteristic.

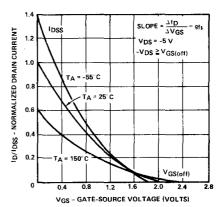

A typical transfer characteristic  $I_D$  versus  $V_{GS}$  is shown in Figure 12. The curve can be closely approximated by

$$I_{D} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_{GS(off)}} \right)^{2}$$

(4)

Typical 1<sub>D</sub> vs V<sub>GS</sub> Transfer Characteristic Figure 12

Equation 4 and Figure 12 indicate that at  $V_{GS} = V_{GS(off)}$ ,  $I_D = 0$ . In a practical device, this cannot be true because of leakage currents. If  $I_D$  is reduced to less than 1 percent of  $I_{DSS}$ ,  $V_{GS}$  will be within 10 percent of the  $V_{GS(off)}$  value indicated by Equation 4. If  $I_D$  is reduced to 0.1 percent of  $I_{DSS}$ , the indicated  $V_{GS(off)}$  error will be reduced to about 3 percent. For a true indication of  $V_{GS(off)}$ , and a realistic picture of the parameters of Figure 12, care must be taken that leakage currents do not result in an error in the  $V_{GS(off)}$  reading. Typically, at room temperature, 1 percent of  $I_{DSS}$  is still well above leakage currents but is low enough to give a fairly accurate value of  $V_{GS(off)}$ .

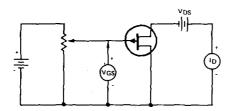

A typical circuit for measuring  $V_{GS(off)}$  is shown in Figure 13. At  $V_{GS}=0$ , the value of  $I_{DSS}$  can be measured. Then, by increasing  $V_{GS}$  until  $I_D$  is 0.01 percent of  $I_{DSS}$ , the value of  $V_{GS(off)}$  is obtained. From a production standpoint, it is more convenient to specify  $I_D$  at some fixed value (such as 1 nA), rather than as a certain percentage of  $I_{DSS}$ . Thus a pinchoff voltage specification may be given as indicated in Table I.

Circuit for Measuring VGS(OFF) Figure 13

Table I

Typical Pinch-Off Voltage Specification

| Characteristic       |                                          |   | Max | Units |

|----------------------|------------------------------------------|---|-----|-------|

| V <sub>GS(off)</sub> | Gate-source pinch-off voltage of:        |   |     |       |

| (                    | $V_{DS} = -5 \text{ V, } l_D = -1 \mu A$ | 1 | 4   | Volts |

Another method which provides an indirect indication of the maximum value of  $V_{GS(off)}$  is shown in Table II. The characteristic specified is  $I_{D(off)}$ , whereas the parameter of interest is  $V_{GS} = 8$  volts. The specification does say that the maximum  $V_{GS(off)}$  is approximately 8 volts, but no provision is made for stating a minimum  $V_{GS(off)}$ , as was done in Table 1. Therefore, another test must be made if  $V_{GS(off)}$  (min) is to be specified.

Table II Indication of Maximum Vo

| Characteristic |                            | Test Conditions                                   | Min | Max | Unit |

|----------------|----------------------------|---------------------------------------------------|-----|-----|------|

| D(off)         | Pinch-off<br>drain current | V <sub>DS</sub> = -12 V,<br>V <sub>GS</sub> = 8 V |     | -10 | μА   |

## IGSS - Gate-Source Cutoff Current

The input gate of a P-Channel FET appears as a simple PN junction; thus the input d-c input characteristic is analogous to a diode V-I curve, as is shown in Figure 14.

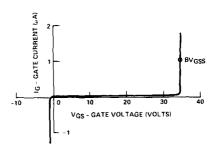

P-Channel FET Input Gate Characteristic Figure 14

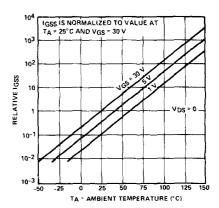

In the normal operating mode, with  $V_{GS}$  positive for a P-Channel device, the gate is reverse-biased to a voltage between zero and  $V_{GS(off)}$ . This results in a d-c gate-source resistance which is typically more than 100M  $\Omega$ . The gate current is both voltage- and temperature-sensitive. Figure 15 shows this relationship for  $I_{GSS}$  versus temperature and  $V_{GS}$ .

IGSS vs Temperature Figure 15

If the gate-source junction becomes forward-biased, (negative voltage in a P-Channel device) or if  $V_{GS}$  exceeds the reverse-bias breakdown for the junction, the input resistance will then become very low.

The FET is normally operated with a slight reverse bias applied to the gate-source; hence a good measure of the d-c input characteristic is to check the gate current at a value of gate-channel voltage that is below the junction breakdown rating. In device evaluation, there are three common measurements of gate current:  $I_{GDO}$ ,  $I_{GSO}$ , and the combined measurement  $I_{GSS}$ . These measurement circuits are shown in Figure 16.