Mit dem HiFive Unleashed stellt SiFive das erste Entwicklungskit vor, welches auf dem Freedom U540 RISC-V-Prozessor basiert. Damit ist das HiFive Unleashed das derzeit einzige linuxfähige RISC-V Entwicklungsboard.

Die offene Prozessorarchitektur RISC-V als Alternative zu patentierten Architekturen wie AMD64 oder ARM v8 hat in letzter Zeit immer mehr Unterstützer gefunden. Dabei ist RISC-V von Mikrocontrollern bis hin zu Großrechnern für eine Vielzahl von Anwendungsfällen geeignet. Wichtige Softwareprojekte wie binutils, GCC, Linux und glibc unterstützen die Architektur mittlerweile.

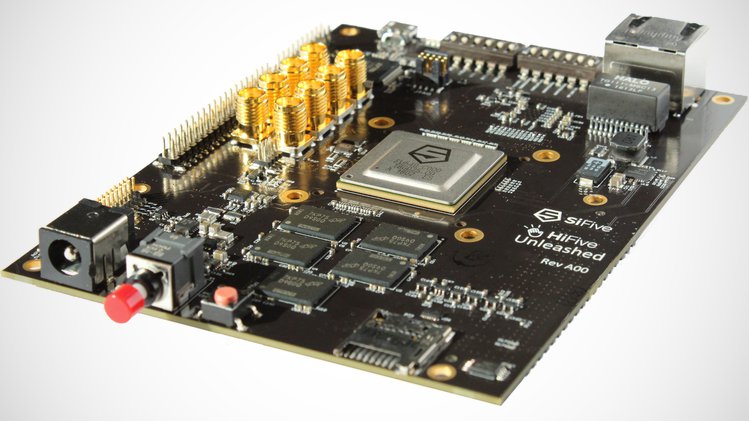

Der auf dem HiFive Unleashed verwendete Freedom U540 stellt den momentan leistungsfähigsten RISC-V Prozessor da. Mit vier Kernen, die je mit bis zu 1,5 GHz betrieben werden können, ist der in einem 28 nm Prozess hergestellte Prozessor für den Betrieb eines Linuxsystems geeignet. Das Board verfügt dabei über 8 GB DDR4 Speicher mit ECC.

Zur weiteren Ausstattung des HiFive Unleashed gehören ein Gigabit-LAN-Port, 32MB SPI-Flash, ein microSD-Slot und ein FMC-Konnektor für spätere Erweiterungen. Darüber hinaus verfügt die derzeitige Version der Platine noch über SMA-Buchsen, an denen Taktsignale zu Debugzwecken abgegriffen werden können.

Das Entwicklungsboard richtet sich hauptsächlich an Entwickler, was auch den Preis von 999 $ erklärt. Ausgeliefert werden soll die Platine Ende Juni, wobei eine limitierte Early-Access Version für 1250 $ bereits Ende März verfügbar sein soll. Beide Varianten können über die CrowdSupply-Kampagne bezogen werden.

Weitere Informationen: