Wellenwiderstand

Einleitung

Schnelle Digitalschaltkreise bzw. hochfrequente Analogschaltungen stellen erhöhte Anforderungen an die Verbindungsleitungen zwischen ICs und Baugruppen. Wo ein langsamer CMOS-Baustein der 4000 Serie mit ein paar Megahertz (wobei die Flankensteilheit entscheidet - nicht die Frequenz) noch problemlos auf dem Steckbrett mit wilder Klingeldrahtverkabelung funktioniert, dort versagt ein moderner, schneller IC seinen Dienst. Ähnliches passiert auf geätzten Leiterplatten. Nicht nur die Packungsdichte der Gehäuse, auch die immer kürzer werdenden Schaltzeiten der Signale verlangen mehr und mehr einen durchdachten, hochfrequenzgerechten Aufbau mit zwei, vier oder mehr Lagen. Die Verbindungsleitungen, welche bei niedrigen Frequenzen praktisch nicht auffallen, sind plötzlich sichtbare Bauelemente, welche die zwei wichtigen Parameter Wellenwiderstand und Laufzeit aufweisen.

Wellenwiderstand

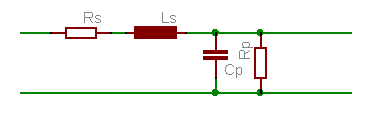

Eine elektrische Leitung muß bei hohen Frequenzen als ein Netzwerk aus folgenden Komponenten betrachtet werden:

- Serienwiderstand Rs

- Parallelwiderstand Rp

- Serieninduktivität Ls

- Parallelkapazität Cp

Praktisch kann man sich das so vorstellen: Jeder elektrische Leiter hat einen ohmschen Widerstand Rs. Vorsicht! Das ist nicht der Wellenwiderstand! Ebenso hat jede elektrische Leitung einen Widerstand zwischen den Leitern, denn der Isolator ist nie ideal. Praktisch kann man den bei niedrigen Frequenzen bis einige hundert kHz vernachlässigen, da er im Bereich von Gigaohm liegt. Allerdings wird er bei höheren Fequenzen im MHz und ganz sicher im GHz-Bereich relevant, denn dort treten deutliche, diekektrische Verluste (verlustbehaftete Umpolarisierung des Isolators). Der Widerstand ist stark frequenzabhängig.

Die unvermeidlichen und ausschlaggebenden Parameter sind jedoch Ls und Cp. Jeder elektrische Leiter, welcher von einem Strom durchflossen wird, erzeugt ein Magnetfeld. Das ist gleichbedeutend mit der Induktivität Ls. Ebenso besteht zwischen zwei isolierten Leitern immer ein elektrisches Feld, wodurch der Kondensator Cp gebildet wird. Ls und Cp sind die entscheidenden Größen zur Bestimmung des Wellenwiderstandes. Je nach geometrischer Anordnung der Leiter kann man sie in gewissen Grenzen variieren (Koaxialkabel, Twisted Pair, Flachbandkabel etc.).

Der Wellenwiderstand berechnet sich aus

- [math]\displaystyle{ Z_0= \sqrt{\frac{L_s}{C_p}} }[/math]

Er ist eine charakteristische Größe einer Leitung und somit unabhängig von deren Länge.

Läuft eine (nicht notwendigerweise sinusförmige) Welle entlang der positiven Richtung der Leitung, so ist das Verhältnis von U und I zu jedem Zeitpunkt und an jeder Stelle der Leitung gleich dem Wert des Wellenwiderstandes.

- [math]\displaystyle{ Z_0= \frac{U_{h}}{I_{h}} }[/math]

Eine Welle wird hier allgemein beschrieben als

- [math]\displaystyle{ U_h(x,t)= h(x-ct) }[/math]

Dies gilt jedoch nur, solange keine Reflexionen an den Enden auftreten, da ansonsten zur hin- auch eine rücklaufende Welle

- [math]\displaystyle{ U_r(x,t)= r(x+ct) }[/math]

hinzukommt. Für letztere gilt der Zusammenhang völlig analog,

- [math]\displaystyle{ Z_0= \frac{U_{r}}{I_{r}} }[/math]

jedoch nicht für die Summe.

Beispiele:

- Koaxialkabel RG58 und RG174, 50Ω

- Koaxialkabel RG59, 75Ω;

- Twisted Pair CAT3/5/7 für Ethernet, 100Ω

- Flachbandkabel, 150Ω typ.

- Leiterbahnen auf Platinen mit 30...150Ω

Laufzeit

Elektrische Signale haben eine sehr hohe, aber dennoch begrenzte Ausbreitungsgeschwindigkeit. In Luft bzw. im Vakuum breiten sich Funksignale mit Lichtgeschwindigkeit aus, das sind 300.000 km/s, oder 30cm/ns. Auf Leitungen breiten sich Signale langsamer aus, da das elektromagnetische Feld mit der Umgebung interagiert. Je nach Leitungstyp etwa mit 50..70% der Lichtgeschwindigkeit, sprich mit ca. 15..21 cm/ns.

Terminierung

Wenn eine elektrische Leitung als lang betrachtet werden muß, dann treten Reflexionen auf. Diese sind unerwünscht und können von sporadischen Fehlern bis zum völligen Versagen einer Schaltung alles verursachen. Deshalb müssen solche Leitungen terminiert werden. Die Terminierung absorbiert die einlaufenden Signale und verhindert damit ungewollte Reflexionen. Eine Leitung wird mit einem ohmschen Widerstand terminiert, welcher den gleichen Wert wie der Wellenwiderstand aufweist. Die Terminierungswiderstände müssen möglichst am Ende der Leitung plaziert werden.

- Eine Leitung ist dann als elektrisch lang zu betrachten, wenn die einfache Laufzeit der Leitung größer als ca. 1/6 der minimalen Anstiegszeit der Signale ist.

- Ein Beispiel

Ein AVR ist ein recht typischer, digitaler IC. Die minimale Anstiegszeit beträgt ca. 5ns. Nach obiger Formel darf die Laufzeit nur

- 1/6 · 5ns ≈ 0,83ns

betragen. Bei einer Ausbreitungsgeschwindigkeit von 21cm/ns ergibt das eine maximal zulässige Leitungslänge von

- 21cm/ns · 0,83ns ≈ 17,5cm

Das heißt, bei einer Leitungslänge von bis zu 17,5cm und halbwegs sauberer Leitungsführung treten keine nennenswerten Reflexionen auf und eine Terminierung ist nicht notwendig. Darüber muss man aufpassen: spätestens bei dem doppelten bis dreifachen Wert ist eine Terminierung meist unverzichtbar.

Serienterminierung

Serienterminierung arbeitet bewußt mit Reflexionen. Von der Quelle wird ein Signal mit einem Innenwiderstand gleich dem Wellenwiderstand eingespeist. Dadurch ergibt sich ein Spannungsteiler von 1:2, d.h. Das Signal hat kurzzeitig nur die halbe Amplitude. Damit läuft es bis zum Ende der Leitung, welches offen ist. Es wird zu 100% reflektiert. Dadurch entsteht der volle Spannungspegel. Wenn die rücklaufende Reflexion die Quelle wieder erreicht wird sie vom Innenwiderstand der Quelle, welcher gleich dem Wellenwiderstand ist, absorbiert, es entsteht keine weitere Reflexion. Idealerweise sollte der externe Serienwiderstand Rs plus der Innenwiderstand des Ausgangs Ri gleich dem Wellenwiderstand sein. CMOS-ICs haben Ausgangswiderstände zwischen 15..50Ω.

Der Terminierungswiderstand muss in der Nähe des Ausgangs des treibenden Bausteins platziert werden -> Quellenterminierung.

Datensignale können meist problemlos mit Serienterminierung betrieben werden. Taktsignale dürfen nur bei Punkt zu Punkt Verbindungen mit Serienterminierung betrieben werden (ein Sender und nur ein Empfänger). Anderenfalls kann es zu Fehlfunktionen kommen, da ein Takteingang, welcher in der Mitte der Leitung sitzt für ein paar Nanosekunden eine Spannung am Eingang anliegen hat die etwa VCC/2 entspricht. Das ist aber genau die Schaltschwelle von CMOS-ICs. Kleinste eingekoppelte Störungen können nun dafür sorgen, daß der Takteingang mehrere Flanken "sieht", wo eigentlich nur eine sein sollte.

Parallelterminierung

Parallelterminierung absorbiert die ankommende Welle am Ende einer Leitung. Damit treten zu keinem Zeitpunkt Reflexionen auf. Nachteilig ist der Stromverbrauch bei HIGH-Pegel. Diese Terminierung ist nicht für 5 oder 3.3V CMOS geeignet. Parallelterminierung wird typisch bei Ethernet sowie beim RS485-Bus verwendet, dort sogar an beiden Enden. Es gibt diverse IO-Standards wie HSTL, SSTL etc., welche für schnelle ICs entwickelt wurden (DDR-RAM, DDR2-RAM), diese arbeiten mit Parallel- sowie Serienterminierung.

Den Stromverbrauch kann man halbieren, indem man mit einem speziellen Spannungsregler eine sog. Terminierungsspannung generiert (z. B. bei SCSI). Dieser Spannungsregler muss sowohl Strom liefern können (source) als auch Strom aufnehmen können (sink). Allerdings ist auch hier der Stromverbrauch noch recht beachtlich, jedoch hat man mit etwas stärkeren Bustreibern eine Chance, auch mit 5/3.3V CMOS eine Terminierung treiben zu können.

Der Terminierungswiderstand muss in der Nähe des Eingangs des empfangenden Bausteins platziert werden -> Senkenterminierung.

Ohne Terminierungsspannung kommt man mit der sog. Thevenin-Terminierung aus. Dabei wird der Terminierungswiderstand durch zwei doppelt so große Widerstände ersetzt. Aus Sicht des Kabels sind diese beiden Widerstände parallel geschaltet! Wichtig ist der zusätzliche Kondensator an VCC und GND, er stellt einen hochfrequenten Kurzschluß dar und ist wichtig für die Funktion dieser speziellen Terminierung. Er muss wie ein Entkoppelkondensator bei einem IC betrachtet und dementsprechend nah platziert werden.

Daher auch der Name: Thevenin Equivalent ist im Englischen die Bezeichung für eine Ersatzschaltung mit anderem Aufbau aber im Endeffekt gleichen Eigenschaften. Hier spart man auch die Hälfte des Stroms ein, allerdings fliesst jetzt auch bei LOW ein Strom durch die Terminierung. Der Stromverbrauch bzw. die Treiberbelastung ist identisch zur Nutzung einer Terminierungsspannung.

AC-Terminierung

Um den Stromverbrauch allgemein zu senken kann AC-Terminierung eingesetzt werden.

Dazu wird ein Kondensator in Reihe zum Terminierungswiderstand geschaltet. Damit fliesst nur für eine kurze Zeit ein Strom, wenn der Pegel wechselt. Nachteilig ist die bisweilen kritische Dimensionierung des Kondensators. Er darf nicht zu klein sein, damit die Spannung nicht zu schnell steigt und somit der Terminierungswiderstand nicht voll wirksam ist. Andererseits darf er nicht zu groß sein, damit der Umladevorgang vor dem nächsten Flankenwechsel abgeschlossen ist (Taktfrequenz). Hier muß man ggf. experimentieren und richtig messen. Typische Werte liegen zwischen 100pF und 10nF.

Für Takte und Signale mit konstantem Mittelwert (Manchesterkodierung, 8B10B Kodierung) kann man den Kondensator sehr groß wählen (100nF Keramik + großen Elko). Dann lädt sich der Kondensator über mehrere Dutzend Takte auf den Mittelwert der Spannung auf und hält diese. Damit wirkt er wie eine Spannungsquelle für die Terminierungsspannung. Der Vorteil ist der eingesparte Spannungsregler, der Stromverbrauch ist hier identisch mit der Parallelterminierung mit Terminierungsspannng. Als grobe Orientierung sollte die Zeitkonstante aus Terminierungswiderstand mal Kondensator ca. 10 mal größer sein als die Periodendauer des Taktes bzw. die Bitdauer das Datenstroms sein:

- [math]\displaystyle{ R_T \cdot C_T \;\gtrapprox\; 10 \cdot T_\text{CLK} }[/math]

Bei Datensignalen ohne konstanten Gleichanteil (also die Mehrheit) wird es etwas schwieriger. Hier kann man mit folgender Abschätzung erste Versuche starten.

- [math]\displaystyle{ R_T \cdot C_T \;\approx\; 3 \cdot t_\text{r} }[/math]

Der Stromverbrauch der AC-Terminierung ist besondes klein bei Datensignalen, welche lange Zeit keine Pegelwechsel haben (Burst, Datenpakete etc.).

Takt- und Datensignale

Bei Datensignalen ist es meist durchaus akzeptabel, wenn ein erhöhtes Maß an Überschwingern und Reflexionen auftreten. Auf synchronen Bussystemem werden die Daten mittels eines Taktes abgetastet. Nur zu diesem Zeitpunkt müssen die Daten sauber anliegen, ein wenig davor (Setup Time) und ein wenig danach (Hold time). Ganz anders bei Takten, asynchronen Resets und Interruptsignalen. Auf diese reagiert ein digitaler IC sofort und sehr schnell. Durch Reflexionen kann es zu "Zacken" auf Taktflanken kommen, welche ein langsamer IC ignoriert aber ein schneller darauf reagiert und zwei Taktflanken "sieht", wo eigentlich nur eine ist. Hier muss man aufpassen. Diese Signale sollten

- sehr solide layoutet werden

- etwas Abstand zu allen anderen Signalen bekommen

- ggf. sauber terminiert werden

Dann gibt es auch keine Probleme mit instabilen Datenübertragungen etc.

Leitungsführung und Layout

Der Zusatz "und halbwegs saubere Leitungsführung" ist eine entscheidende Komponente bei der Verteilung schneller Signale! Irgendwelche wilde Klingeldrahtorgien oder lieblos auf die Platine geschmissene Leitungen zählen nicht dazu. Im Idealfall sind die Leitungen mit einer Impedanz von 50 oder 75Ω layoutet, bei differentiellen Signalen auch 100Ω (Ethernet, LVDS etc.). Dazu muß eine bestimmte Geometrie der Leiterbahn eingehalten werden, im wesentlichen bestimmt durch Breite und Abstand zur Referenzfläche (GND oder VCC). Die Stichworte für eine Suche im Internet lauten Microstrip und Stripline. Bei zwei- oder vierlagigen Platinen werden die Leitungen mit 50/75Ω ziemlich breit, deshalb kann man sich dort dem Ideal nur sehr grob nähern. Dennoch sollte man es vor allem für Takte versuchen und möglichst die Leitung über einer Referenzfläche führen. Das grundlegende Prinzip lautet:

Die Fläche der Leiterschleife zwischen Signal und Massefläche muß minimiert werden.

Man muß immer daran denken. Strom fließt immer im Kreis, deshalb heißt es ja auch Stromkreis. Der Stromkreis beginnt am Versorgungspin des ICs, welcher das Signal generiert, läuft über den Ausgang und die Signalleitung zum Eingang des Empfängers bzw. der dort platzierten Terminierung, dort nach Masse und über die Masse zurück zum Sender-IC. Die Rückleitung über Masse ist genauso wichtig wie die Hinleitung des Signals! Eine wild geschlungene Masseleitung macht das beste Layout zunichte. Optimal sind komplette Masseflächen, doch die sind meist nur bei Platinen mit vier oder mehr Lagen machbar. Bei hochfrequenten Analogschaltungen gönnt man sich den "Luxus" auch bei zweilagigen, weil man sonst in Teufels Küche kommt. Bei schnellen Digitalschaltungen auf zweilagigen Platinen muß man Kompromisse eingehen. Aber auch hier gilt die alte Weisheit, daß die Masse möglichst sternförmig verteilt werden sollte. Entgegen der weit verbreiteten Meinung spielen 90° Winkel keine große Rolle, auch nicht weit in den den Bereich von 1 GHz! Siehe Abschnitt Links.

Wenn Kabel als Verbindung zwischen ICs verwendet werden, sollte man auch hier Sorgfalt walten lassen.

- Idealerweise sollte man bei Flachbandkabeln jede 2. Ader auf Masse legen und auf BEIDEN Seiten der Verbindung am Stecker mit der Masse der Platine verbunden werden.

- Meist reicht es, jede 4. bis 10. Ader auf Masse zu legen, wobei man Takte direkt neben die Masse legen sollte.

- Nach Möglichkeit sollte man die beiden äußeren Adern eines Flachbandkabels auf Masse legen, damit erreicht man gute EMV

- Bei Steuerkabeln (verdrillt oder auch nicht) gilt ähnliches.

Zusammenfassung

- Entscheidend für das Entstehen von Reflexionen ist NICHT die Taktfrequenz sondern die Anstiegszeit der Signale. Eine Schaltung mit schnellen ICs wird auch bei niedrigen Taktfrequenzen sehr schnell schalten, auch wenn das nicht unbedingt notwendig wäre.

- Mit Reflexionen muß man rechnen, wenn die einfache Laufzeit der Leitung grösser als ca. 1/6 der minimalen Anstiegszeit der Signale ist.

- Serienterminierung ist für Takte nur bei Punkt-zu-Punkt-Verbindungen sicher nutzbar.

- Parallelterminierung ist für 5/3,3V CMOS ungeeignet (Stromverbrauch, Treiberleistung).

- Auch mit Terminierung ist bei schnellen Signalen eine saubere Leitungsführung notwendig.

- Man sollte nach Möglichkeit immer die langsamsten Logikbausteine verwenden, um Probleme mit Reflexionen zu minimieren (Wozu braucht man 1ns Anstiegszeit bei 5 MHz Takt?).

- Ausgänge sollten möglichst identische Ausgangswiderstände für LOW und HIGH haben (wie z. B. die HC-Familie), sonst wird eine Serienterminierung schwierig bis unmöglich (wie. z. B. die ABT-Familie); siehe "Input and Output Characteristics of Digital Integrated Circuits"

Berechnung

Zur Berechnung kann man eine der in den Links aufgeführten Seiten benutzen. Die bessere Lösung (einfacher und offline) sind allerdings die in vielen Layout-Programmen enthaltenen Berechnungswerkzeuge. In KiCad z.B. unter PCB-Rechner > TransLine.

Eine schöne und verständliche Erklärung aus einem Forumsthread

→ Forum: Was ist der Wellenwiderstand?

- Bei einer kurzen Leitung (kürzer als ein Viertel der Wellenlänge)

- Bei einer Leitung ohne Last (Re = ∞) wirkt die Leitung wegen ihrer verteilten Kapazität (Kapazitätsbelag) kapazitiv.

- Bei einer Leitung mit Kurzschluss am Ende (Re = 0) wirkt die Leitung wegen ihrer verteilten Induktivität (Induktivitätsbelag) induktiv.

- Irgendwo dazwischen gibt es einen Wert, wo Induktivität und Kapazität sich gerade kompensieren: Das ist der Wellenwiderstand. Er ermöglicht eine kapazitäts- und induktivitätsfreie Übertragung.

- Eine Leitung gibt an einen Lastwiderstand volle Leistung nur bei einem bestimmten Strom/Spannungsverhältnis ab. Wenn der Lastwiderstand ein anderes Strom/Spannungsverhältnis erzwingt, wird ein Teil des Stroms oder der Spannung in die Leitung reflektiert. Der Widerstand, bei dem z.B. Impulse reflexionsfrei übergeben werden, ist der Wellenwiderstand.

- Durch die Geometrie einer Leitung werden Kapazitätsbelag und/oder Induktivitätsbelag verändert. Aus dem Verhältnis Kapazität/Induktivität lässt sich ein Widerstand errechnen, dies ist der Wellenwiderstand.

90° Ecken in Leiterbahnen

Das Thema wird seit Jahrzehnten diskutiert, real gemessen haben die Wenigsten. Hier die kurze Zusammenfassung aus zwei guten Quellen.

Messung von Ultraboard

- sieben Leiterzüge mit 20,3cm Länge, 0,25mm Breite, Microstrip mit 50 Ohm; verschiedene Winkel

- Messung mit TDR und 17ps Anstiegszeit, ~2,8mm Pulslänge auf der Leitung, etwa 10fache Leiterbahnbreite

- Auf keiner Leitung konnten Effekte nachgewiesen werden!

- Eine Messung der Abstrahlung mittels Antenne bis 1,3 GHz zeigte auch keine sichtbaren Unterschiede jenseits der Messungenauigkeit

Interview mit Dr. Howard Johnson, HF-Guru

- Die Legende kommt aus dem Bereich der Mikrowellen, wo die Theorie und Praxis in den 1960er Jahren sehr umfangreich erarbeitet wurde

- Direkte Übertragung vom Mikrowellengebiet 1-100GHz auf schnelle Digitalsignale (100MHz-10GHz) ist direkt nicht möglich, weil die Parameter anders sind

- Typische Leiterbahnbreiten für Digitalsignale sind 0,25mm und weniger, eine 90 Grad Ecke fügt ca. 0,02pF hinzu, typische Frequenz 1GHz bei Signalamplituden von 400mV und mehr (PECL, LVDS), hoher Störabstand (Digitalsignale), der Effekt ist kaum nachweisbar

- Typische Leiterbahnbreite für Mikrowellentechnik ist 3mm, Kapazitätszuwachs liegt bei ca. 0,2pF, Frequenzen von 10 GHz und mehr, Signalamplituden im Millivoltbereich mit engen Toleranzen über eine lange, analoge Verstärkerkette (+/-0,5dB über 10 Stufen)

Fazit. Die Winkel spielen unter 1 GHz keine Rolle, darüberhinaus nur sehr wenig. VIAs spielen bei 1GHz und mehr eine Rolle. 10fach wichtiger ist jedoch immer eine solide Bezugsfläche unter der HF-Leitung!

Siehe auch

- Forumsbeitrag: Warum HF-Leitungen abrunden?

- Forumsbeitrag: Thevenin-Terminierung für einen SPI-Bus mit langen Kabeln

- Forumsbeitrag: Einfacher Treiber für Parallelterminierung.

- Forumsbeitrag: Wellenwiderstand messen

- Forumsbeitrag: Serienwiderstand bei Hochfrequenz

- Forumsbeitrag: Signale an intelligenten LEDs (WS2812B) und langen Leitungen

- Forumsbeitrag: Probleme mit SPI

Links

- Wellenwiderstand bei Wikipedia

- www.signalintegrity.com, Die Bibel der hochfrequenten Digitalsignale

- AppNote von ON Semiconductor: Termination of ECL Logic Devices (ausführlicher als der Artikel)

- "Input and Output Characteristics of Digital Integrated Circuits"

- http://www.forelec.ch/fichiers/HS-PCB-1.PDF (Sehr gutes Dokument zum Thema)

- Striplines/Microstrip schnell berechnet (PDF)

- Online Calculator

- Noch ein Offline Calculator

- Linksammlung Transmission Line Design and Analysis

- TDR Circuit, ein einfaches Time Domain Reflektometer zum selber bauen

- The Amp Hour #77 — Winsome Waveform Wizardry, Podcast mit Dr. Howard Johnson, HF-Guru (Ab 01:15:00 kommt die Stelle zum Thema 90° Leiterbahnen)

- High speed data transfer, Howard Johnson über 90 Grad Ecken in Digitalschaltungen (engl.)

- Messung von verschiedenen Winkeln von Leiterbahnen mit 17ps TDR, keinerlei Unterschiede!

- Impedanzen einfach und praktisch messen

- Impulse auf Leitungen - Elektrische Grundlagen, Vorlesungsmaterial

- PDF, diverse Kabel mit Daten zum Wellenwiderstand.

- Trace Termination (engl.)