Arms Reaktion auf RISC-V ist - so viel ist nach dem letzten Entwicklerkongress klar - die „Flucht nach oben“. Waren RISC-V-Chips bisher im Embeddedbereich gut vertreten (Stichwort GigaDevice), so greift die Architektur nun nach höherwertigen Einsatzgebieten. Hier eine Liste interessanter Ankündigungen der letzten Tage.

Worum geht es hier?

Auch wenn die ARM-NVIDIA-Übernahme mittlerweile vom Tisch ist: wer ARM-Chips einsetzt, bindet sich an die “rule based international order”. Mit RISC-V steht eine quelloffene ISA zur Verfügung, die von asiatischen und amerikanischen Halbleiterherstellern gleichermaßen umgesetzt wird. Waren die Chips bisher vor allem für MSR-Aufgaben vorgesehen, so treten nun Varianten an, die ihren Nutzern mehr Leistung, beispielsweise zur Ausführung von Android oder von AI-Payloads, ermöglichen.

Alibaba: XuanTie C908 Midrange-CPU auf Basis von RISC-V

T-Head Semiconductor - auch bekannt als Alibaba sein Halbleiterbauer - bietet seit einiger Zeit RISC-V-Chips an - auf der Webseite der RISC-V-Association findet sich die in der Abbildung gezeigte Grafik, die die Produkte samt Roadmap illustriert.

(Bildquelle: https://riscv.org/blog/2022/11/xuantie-c908-high-performance-risc-v-processor-catered-to-aiot-industry-chang-liu-alibaba-cloud/ )

Neu ist nun der C908 - ein Chip, der zwar leistungsfähiger als der C906 ist, dem hauseigenen High End-Modell C910 aber unterlegen ist. Ziel des Chips ist dabei die Unterstützung von Aufgaben der künstlichen Intelligenz - als Betriebssystem dürfte Linux zum Einsatz kommen, weil der Kernel in der Version 5.19 bereits Unterstützung für den neuen Chiptyp mitbringt. Interessant ist an diesem Chip auch, dass in ihm eine Gruppe verschiedener neuer RISC-V-Features, teilweise sogar zum ersten Mal, unterstützt wird:

1 |

XuanTie C908 supports the RV32 COMPAT mode for the first time . . . |

2 |

RISC-V Bitmanip 1.0 instruction extension including the carry-less multiplication (zbc), optional support for RISC-V Vector 1.0 instruction set extension, BF16 operations, IEEE-754 compatible half-precision, and other floating-point operations. In addition, XuanTie C908 supports the RISC-V CMO Base extension and Svinval extension. It adopts the Sv39/Sv48 virtual address system and holds up Svnapot and Svpbmt. All these features make it possible for XuanTie C908 to be one of the first RISC-V processors for the upcoming RVA22 profile. . . . |

Noch ist allerdings nicht klar, wann der C908 auf den Markt kommen wird, und vor allem, ob er auch außerhalb Chinas angeboten werden wird. Erste Benchmarks finden sich bei der Bildquelle.

Andes Technologies plant Hochleistungskernfamilie AX60.

Andes Technologies - das Unternehmen sitzt in Formosa - bietet vor allem „IP-Cores“ auf Basis der RISC-V-ISA an. Neu ist die AX60-Familie - dabei handelt es sich um RISC-V-basierte Chips, die aber die 64 Bit-Version der ISA umsetzen.

Neben der Ankündigung der Familie steht mit dem A 65 ein erster Vertreter am Start. Es handelt sich dabei um einen Chip mit einer 13-stufigen Pipeline, der verschiedene Architekturerweiterungen wie das Kryptographiemodul und die Bit-Manipulations-Instruktionen umsetzt. Explizit betont Andes im Rahmen der Ankündigung außerdem, dass die Chips auch für den Einsatz im Mehrkernprozessor vorgesehen sind:

1 |

AX65 supports multicore cluster with cache coherence to scale out performance. Each core has 64KB private instruction and data caches. The cluster contains up to 8 cores, an in-cluster coherence manager and a shared cache up to 8MB. Its IO coherence interface keeps all AX65 caches coherent with respect to the external IO transactions and allows ease of SoC integration. |

Im Bezug auf die Verfügbarkeit verspricht Andes Technologies, dass “wichtige Referenzkunden“ mit 2023 mit dem Chip interagieren können - der Normalkunde soll bis Ende desselben Jahres Zugang bekommen. Dies bedeutet allerdings nicht, dass auch tatsächlich Chips folgen - viele der Kerne dienen in verschiedenen kleineren-Special-Interest-Chips als Rechenelement.

SiFive: zwei neue Chips mit Android-Unterstützung

Waren die bisherigen Neuzugänge asiatischer Provinienz, so liefert auch das in San Mateo, Kalifornien ansässige Unternehmen SiFive neue Kandidaten - interessant ist daran, dass einige der Gründer der Firma ursprünglich an der Universität zu Berkeley gearbeitet haben, die er im Bereich der Spezifikation der ISA eine Führungsrolle einnimmt.

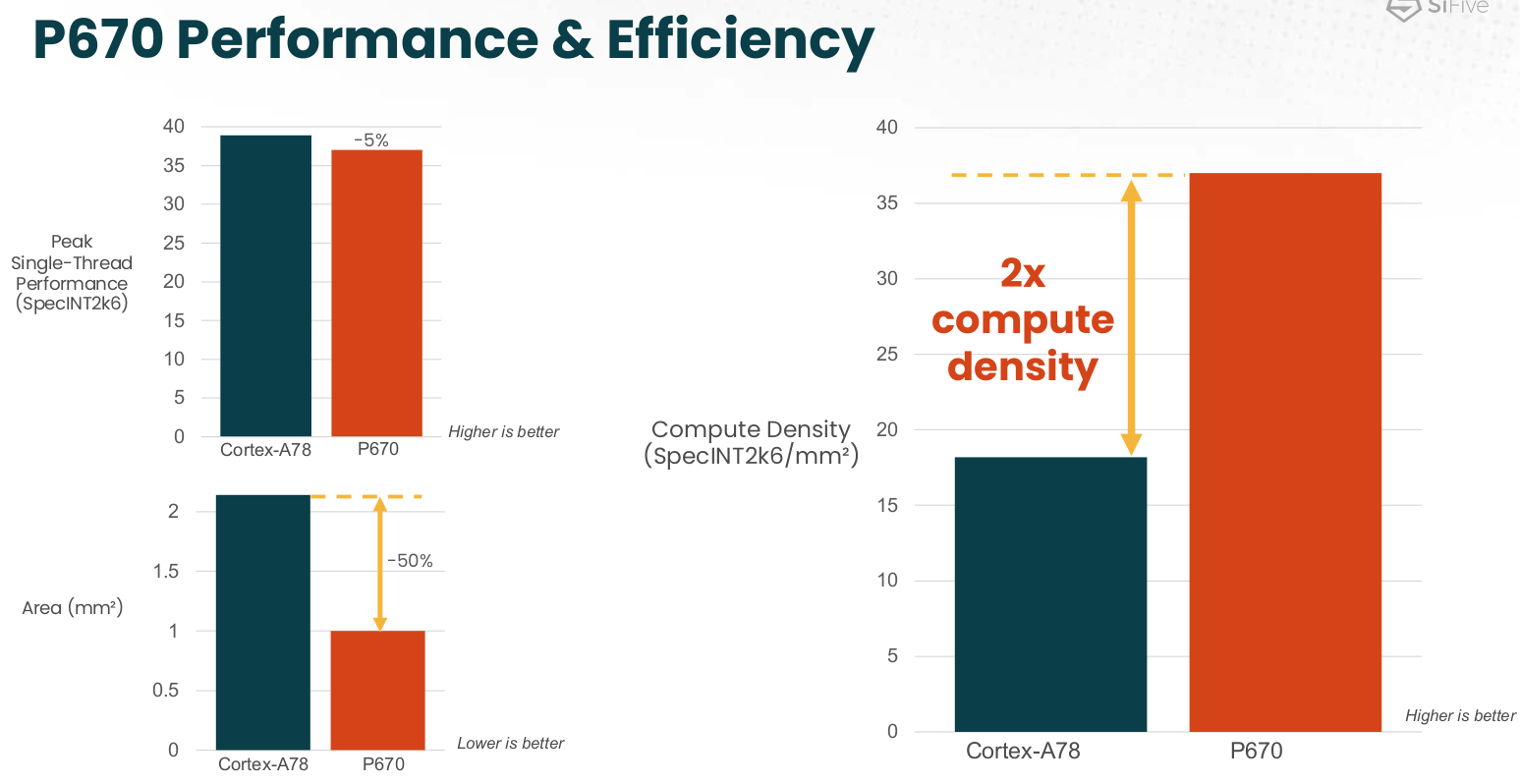

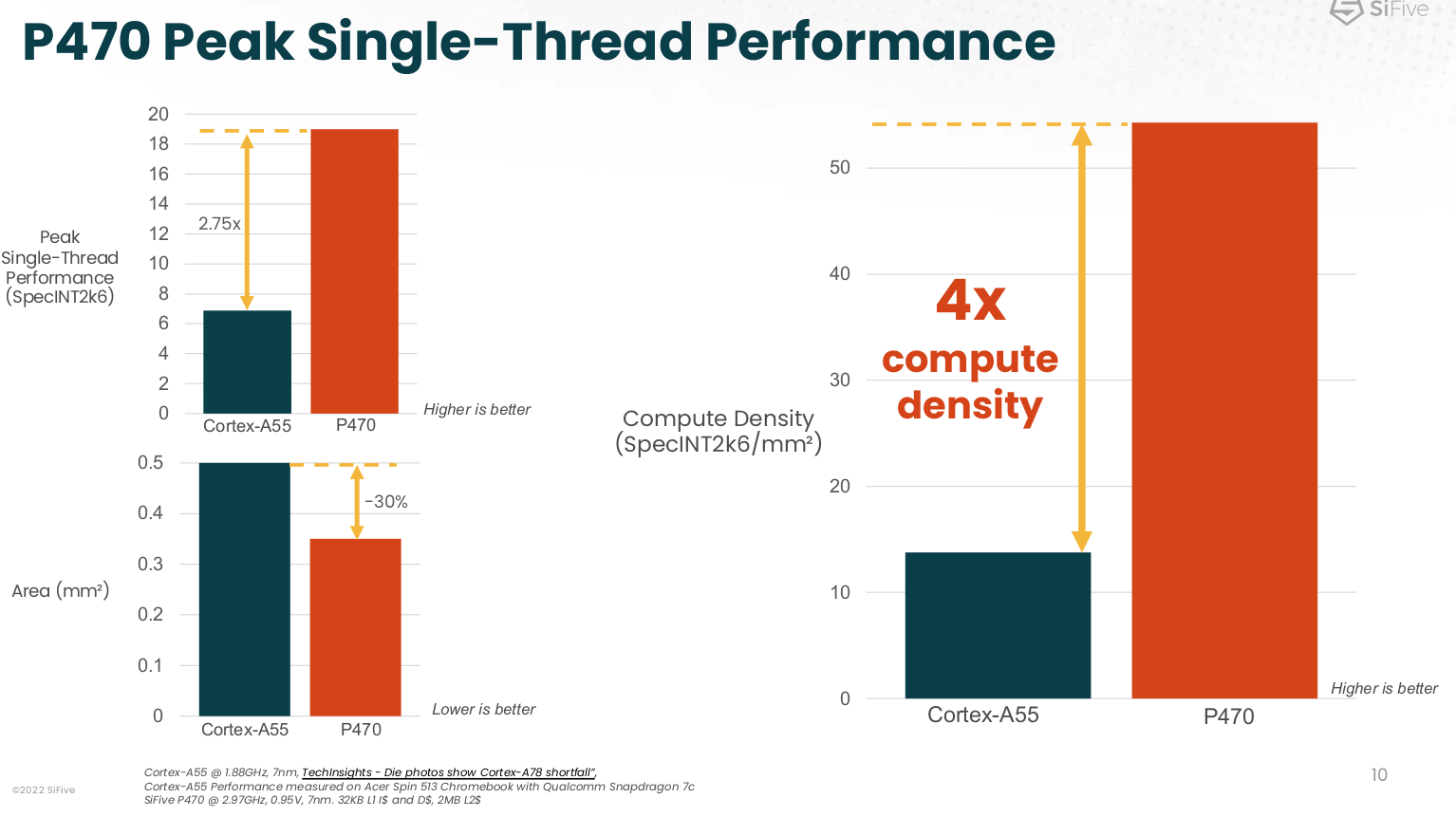

Die vom im Allgemeinen gut informierten Branchendienst cnx-software unter https://www.cnx-software.com/2022/11/02/sifive-p670-and-p470-risc-v-processors-add-risc-v-vector-extensions/ als Alternativen zu ARMs Cortex A78- und A55 beschriebenen Chips sind beide für den Smartwatch-Bereich vorgesehen:

1 |

The P670 is ideal for applications like premium wearables, networking, robotics, and mobile. The P650, which excludes the vector unit, is already shipping to lead customers |

2 |

. . . |

3 |

The P470 is SiFive’s first efficiency-focused Out-of-Order, area optimized, vector processor, ideal for applications like wearables, consumer, and smart home devices. |

(Bildquelle: cnx)

Im Rahmen der Ankündigung erwähnte SiFive außerdem die Arbeiten an der Android-Integration:

1 |

Additionally, as the upstream enablement of RISC-V has started within the Android Open Source Project, (AOSP), designers will have unrivaled choice and flexibility as they consider the positive implications with that platform for future designs. |

Was folgt daraus?

Die Entwicklung eigener Einplatinencomputer auf Basis eines SoC ist eine Aufgabe, die für Kleinunternehmen nicht oder nur schwierig zu bewältigen ist – die Bausteine sind sowohl im Bezug auf die Spannungsversorgung als auch im Bezug auf das Speicherinterface auf keinen Fall mit “gewöhnlichen” MCUs vergleichbar. Das Aufkommen der hier gezeigten Controller ist trotzdem von Relevanz: wer an einem Projekt arbeitet, ist in der heutigen Weltlage immer gut beraten, die politischen “Seiteneffekte” bestimmter Designentscheidungen im Hinterkopf zu behalten. Über kurz oder lang werden einige der hier vorgestellten Chips in Einplatinencomputern zum Einsatz kommen – wer die Schlagworte bzw Chipnamen kennt, kann den hauseigenen SBC-Lieferanten ausserdem oft in die richtige Richtung stupsen...