BAE-Tutorial

Einleitung

Bartels Auto Engineer (BAE) ist ein EDA-System, das eigentlich aus dem Highend-Bereich stammt. Mit der Light-Version steht dabei eine preislich auch für den ambitionierten Hobbyisten erschwingliche Version zur Verfügung (159 EUR+MwSt+Versand, Stand 19.4.2010), die auf eine Platinengröße einer Eurokarte (100 x 160 mm², zuzüglich Ränder für die Layouterstellung) und zwei Lagen beschränkt ist, aber ansonsten alle Features der Profi-Versionen besitzt. Das System verfügt über einen Autorouter, der recht ansehnliche Ergebnisse erzeugen kann, wenn man sich die Mühe macht, ihn passend zu parametrieren.

Das gesamte System einschließlich der Dokumentation kann wahlweise in deutsch oder englisch installiert werden. Es ist sowohl auf Windows-Systemen als auch auf Linux (sowie einigen anderen Unixen) lauffähig. Die Linux-Version lässt sich unter FreeBSD in der Linux-Emulation problemlos benutzen. BAE benötigt zur ordnungsgemäßen Funktion die Open-Motif Bibliotheken und lässt sich mit Lesstif nicht vernünftig nutzen.

Das Handbuch enthält eine Schritt-für-Schritt-Anleitung für ein einfaches Beispielprojekt, die man als Neuling unbedingt erst einmal durcharbeiten sollte. Der gesamte Einarbeitungsaufwand ist nicht unerheblich, aber das System stellt sich nach längerer Nutzung als recht gut durchdacht heraus, wobei man im Hobbybereich viele der Möglichkeiten nur streift.

Schaltplan-Editor

Der Schaltplan-Editor gestattet die Verteilung der Pläne über mehrere Blätter, sodass es keine Notwendigkeit gibt, alles auf ein einzelnes riesiges Blatt zu zwängen. Manche Symbole sind (damit man sie noch gut erkennen kann) recht groß, sodass ein A3-Format ggf. sinnvoll sein kann. Die Schaltplanerstellung kann hierarchisch erfolgen, d. h. ein Schaltplanblatt kann einen Schaltplanmodul beschreiben, der seine Verbindungen zur Außenwelt einerseits über globale Netze (wie GND oder VCC) und andererseits über sogenannte Modulports herstellt. Damit lassen sich gleichartige Baugruppen effektiv realisieren.

Vorteilhaft am Schaltplaneditor ist, dass man eine optische Anzeige besitzt, ob eine bestimmte Verbindung am gewünschten Bauteil tatsächlich "angedockt" hat: unverbundene Anschlüsse werden durch ein kleines ockerfarbenes Quadrat dargestellt, das beim Anfügen einer Verbindung verschwindet. Werden das Quadrat und die Leitungen des zugehörigen Netzes schwarz, dann "stimmt etwas nicht" mit diesem Netz (bspw. endet eine Verbindung irgendwo in der Luft).

Obacht sollte man jedoch auf die nicht im Schaltplan sichtbaren globalen Netze geben, die allesamt per Namen miteinander verbunden werden. Manche Bauteile benutzen bspw. GND als negative Spannung, andere wiederum VSS. Gleiches trifft auf VDD oder VCC zu. Wenn man es verpasst, diese Netze im Stromlaufplan zu verbinden, dann sind sie auch im Layout nicht verbunden.

BAE besitzt umfangreiche Attribute, die intern für die Steuerung der Komponenten genutzt werden. So lassen sich an einem Netz im Stromlaufplan Routingbreiten und Mindestabstände festlegen, die dann sowohl beim manuellen Routing als auch im Autorouter die Voreinstellung der Routingbreite überschreiben. Die Attribute selbst werden wie Schaltplansymbole behandelt. Sie befinden sich in der Bibliothek route.ddb. Das Symbol für die Routingbreite heißt =att_rw= (routwidth), das für den Mindestabstand =att_md= (mindist).

Layout-Erstellung

Die Layoutelemente selbst sind hierarchisch strukturiert. Dies erlaubt eine volle Flexibilität für deren Gestaltung. Jedes Pin (bei durchsteckbaren Bauteilen [THT]) bzw. Pad (bei SMD) wird durch einen sogenannten Padstack dargestellt. Der Padstack besteht wiederum aus einzelnen Pads und ggf. aus Bohrungen. Die Pads dienen dabei einerseits als Kupferflächen für tatsächliches Kupfer. Diese werden bei THT typischerweise auf "Alle Lagen" gelegt, während sie bei SMD-Padstacks normalerweise auf Lage 2 (grün) liegen. Andererseits werden mit Pads auch Flächen definiert für die Lötstoppmaske (die damit andere Abmessungen als die Kupferfläche besitzen kann) oder den SMD-Lotpastenauftrag.

Auf Bauteilebene kann man jedem Bauteil neben dem Symbol/Umriss für den Bestückungsplan einen Bestückungsdruck ("Baugruppen") zuweisen sowie eine DRC-Fläche hinterlegen. Die DRC-Flächen der Bauteile werdeim beim Design Rule Check (DRC) auf Nichtüberlappung getestet, ggf. vorhandene Überlappungen werden als DRC-Fehler gemeldet.

Die Standard-Farbpalette enthält dabei nicht für alle diese Dokumentationslagen Farbzuweisungen, da das Bild dann schnell sehr unübersichtlich wird. Die Farbpalette lässt sich im Darstellungsmenü ändern (mittlere Maustaste), wobei man eine einmal erstellte Palette mit Namen ablegen kann. Die Rechtecke mit den Zahlen 1 bis 4 in der Werkzeugleiste gestatten dann eine Schnellauswahl von 4 Paletten (normalerweise "toolbar1" bis "toolbar4" genannt, aber der Präfix lässt sich in dem rechteckigen Feld mit dem kleinen s auch ändern), oder das Rückschalten auf die Standard-Palette (Rechteck mit dem kleinen d).

Beim Verlegen von Leiterzügen werden die unter "Einstellungen" vorgenommenen DRC-Abstände als Umrandung um den aktuellen Leiterzug angezeigt. Wenn beim Verlegen an irgendeiner Stelle der aktuellen Bahn der DRC-Abstand unterschritten wird, verfärbt sich diese Umrandung von der Farbe der entsprechenden Ebene in weiß. Wird der Leiterzug dennoch platziert, dann wird die DRC-Fehlerstelle mit einem kleinen Rechteck in der Fehlerfarbe sofort angezeigt, ohne dass man erst manuell einen DRC-Check aktivieren muss.

Tipps & Tricks

Layout-Ausdruck zum Selbstätzen

BAE bringt umfangreiche Funktionalität zum Erstellen, Sichten und Verändern professioneller Fertigungsdaten mit sich, die Programmteile CAM-Prozessor und CAM-View sind ausschließlich zu diesem Zweck geschrieben. Für die einfache Platine in der Hobbywerkstatt sind diese Tools meist ziemlich oversized und vernachlässigen einen wichtigen Aspekt der Selbstbau-Platine völlig: Das händische Bohren. Dank zweier Patches von Jörg Wunsch ist es problemlos möglich Layouts mit Zentrierlöchern auf Papier oder Folie zu bringen.

Beide diffs patchen gegen die original ulc's der Version 7.2 und funktionieren nicht mit neueren Version, z. B. den auf der Bartels-Website herunterladbaren Aktualisierungen. Nach dem Patchen das Compilieren (mit dem Programm "ulc") nicht vergessen ;-)

Danach findet sich im GED unter 'Einstellungen' -> 'Einstellungen bae.ini' ein neuer Punkt 'Radius Bohrloch-Mittelpunkt' der mit 0.15 mm vorbelegt ist und nach den eigenen Wünschen angepasst werden kann.

Die Patches wurden in leicht veränderter Form in BAE 7.2 ab Build 29 offiziell eingearbeitet. Die Voreinstellung des Bohrloch-Radiusses erfolgt dort immer noch in bae.ini, aber die Änderung erfolgt nicht mehr über "Einstellungen bae.ini", sondern man kann den Wert dann direkt in jeder Bohrungs-Lage explizit angeben, wenn "Bohrloch-Mittelpunkt" ausgewählt worden ist.

Die Druckausgabe befindet sich im GED etwas versteckt unter 'Datei' -> 'Import/Export' -> 'EPS/PDF-Ausgabe'. Dort in die Batchausgabe wechseln und einen neuen Batch anlegen. Es bietet sich an einen aussagekräftigen Namen wie z. B. 'PDF, Bottom-Drill' zu vergeben. Eine neue Ausgabedatei anlegen, z. B. mit der Dateiendung '_bot.pdf'. Über die Seitenauswahl zur Lagenauswahl vordringen und dort folgende Layer in dieser Reihenfolge hinzufügen:

- Lötseite ("Signallage 1")

- Alle Lagen

- Umrandung

- Der gewünschte Bohrlayer. Hier sollte als Darstellung 'Mittelpunkt' ausgewählt werden und die Farbe muß auf Weiß (1.0, 1.0, 1.0) gesetzt werden.

Hat man sich über eine Unzahl an 'Fertig'- und 'OK'-Buttons wieder zurück zur Batchauswahl geklickt ist der Job fertig angelegt und steht ab dann dauerhaft zur Verfügung.

Analog kann ein Ausdruck der Oberseite erstellt werden wenn man Signallage 2 verwendet (Spiegeln einschalten nicht vergessen!) Sinnvollerweise sollte man die Zentrier-Bohrlöcher jedoch nur auf einer von beiden Seiten ausgeben. Dadurch bleibt bei einem leichten Versatz zwischen beiden Seiten auf der gegenüberliegenden Seite in jedem Falle noch die volle Kupferfläche zur Verfügunng, auch wenn die Bohrung nicht exakt mittig liegt.

Schaltplan: ganzen Bus auf einmal anschließen

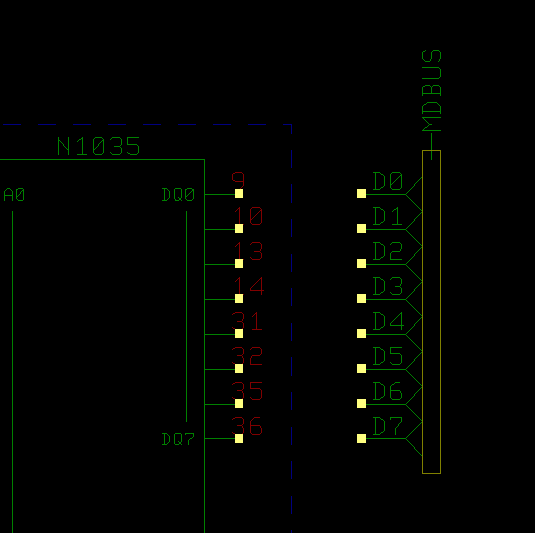

Wenn man ICs mit ganzen Bussen anschließen will, steht man häufig vor der Aufgabe, dass man sehr viele völlig gleichartige Verbindungen im Schaltplan zeichnen muss. Ein typisches Beispiel sieht ungefähr so aus:

Das Zeichnen der einzelnen Verbindungen ist zeitraubend, und wenn man die Anschlüsse nicht gleich beim ersten Versuch "trifft", muss man nochmal nachzeichnen.

Schön wäre es doch, wenn man alle gleichartigen Verbindungen zugleich zeichnen lassen könnte... Ja, das geht!

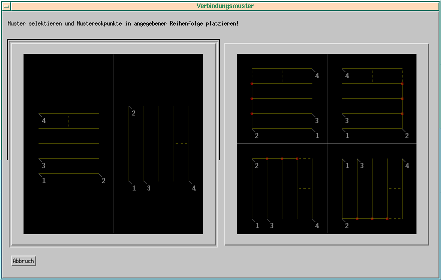

Man wählt aus: Verbindungen, Weitere

Funktionen, Muster zeichnen, und erhält zwei

Knöpfe zur Auswahl des Verbindungsmusters:

Das linke Muster ist hier das interessante.

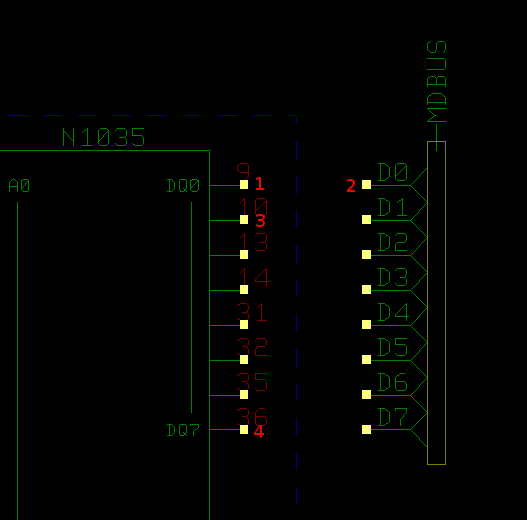

Danach muss man die vier Punkte festlegen; diese sind im folgenden Bild mit roten Ziffern markiert:

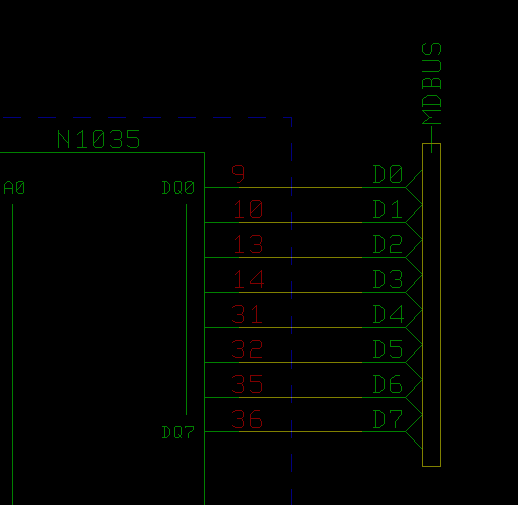

Danach werden die Verbindungen gezeichnet, das Ergebnis sieht dann so aus:

Bauteile auf Platine gleichmäßig nummerieren

Wenn das Layout komplett ist, möchte man u. U. alle Bauteile schön gleichmäßig durchnummeriert haben, beispielsweise von links oben nach rechts unten. Damit ist man dann das beim Schaltplanzeichnen entstandene ziemliche Durcheinander von R1013, R1011, C1023, IC10 usw. los, und der Bestückungsplan lässt sich gut lesen.

Der Weg dazu ist, dass man zuerst das Layout fertig stellt, bis man sich sicher ist, dass es keine weiteren Verschiebungen mehr gibt. Dann wählt man den Menüpunkt "Bauteile" -> "Weitere Funktionen" -> "Bauteile benennen" -> "Alle Präfixe". Anschauen, ob die gewünschten Zählrichtungen so passen, danach "OK". Abspeichern, und dann im Schaltplaneditor die Backannotation aufrufen (unter "Utilities"), danach stimmen die Bezeichnungen im Schaltplan und Layout überein.

Abschließend kann man bei Bedarf noch die Namen der Bauteile so schieben, dass sie im Bestückungsplan gut lesbar sind.

Motif-Version für Linux

BAE linkt gegen eine etwas ältere Version der Motif-Bibliothek, die in aktuellen Linux-Distributionen nicht mehr enthalten ist. Hier: Datei:LibXm.so.2.tar.bz2 ein .tar.bz2-Archiv, relativ zu /, mit dem BAE in der Lage ist zu arbeiten.

Auspacken (als root):

cd / tar xvjf /tmp/LibXm.so.2.tar.bz2 ldconfig

Autorouter parametrieren

Die Qualität der Ergebnisse des Autorouters hängt sehr wesentlich davon ab, dass man ihn passend parametriert. Generell ist die Vorgehensweise bei der Benutzung des Autorouters eine völlig andere als beim manuellen Routen. Man kann das ungefähr mit der Programmierung in Assembler gegenüber der mit einem Compiler für eine höhere Sprache vergleichen: in aller Regel benutzt man den vom Compiler generierten Assemblercode ja nicht als Basis für künftige manuelle Weiterentwicklung, sondern nimmt die Weiterentwicklung in der Hochsprache vor, bis das Ergebnis den Zweck erfüllt. Der Vorzug des Autorouters liegt darin, dass er, einmal parametriert, auch nach einer künftigen Änderung ("Oh, wir müssen schnell noch diese drei Steckverbinder auf der anderen Seite der Platine unterbringen!") in endlicher Zeit einfach wieder das gewünschte Ergebnis abliefert.

Baugruppen, bei denen das Layout kritisch ist (analoge Baugruppen, Stromversorgungswege, wenn keine Versorgungslagen verwendet werden können oder sollen), routet man dabei manuell. Anschließend selektiert man alle Leiterbahnen und fixiert diese Teile über die Menüpunkte Bearbeiten -> Gruppe fixieren, sodass der Autorouter diese Teile später nicht mehr verändert. Wenn der Autorouter daran gehindert werden soll, durch bestimmte Bereiche Bahnen zu legen, dann müssen über diese Bereiche noch Sperrflächen gelegt werden, entweder in der/n Lage(n), in denen das gewünscht ist, oder einfach auf Alle Lagen. Diese Sperrfläche wandelt man anschließend in eine Autorouter-Sperrfläche um, damit der DRC sich nicht darüber beklagt, dass sich in der Sperrfläche manuell verlegte Bahnen befinden. Dies geht entweder über das Kontextmenü, das man für eine Ecke der Sperrfläche aufruft, und dort dann die Eigenschaften der Fläche auswählt (Drücken der Taste 'P' über einer Ecke geht ebenfalls). Damit der Mauskontext nicht versehentlich statt der Sperrfläche ein Bauteil erfasst, kann man die Mausfunktion einschränken, dass sie bestimmte Dinge nicht betrachten soll (Leertaste oder kleines Maussymbol in der Werkzeugleiste, danach dann die entsprechenden Kästchen abwählen). Alternativ kann man die Sperrflächen über folgende Menükombination modifizieren: Flaechen -> Weitere Funktionen -> Polygontyp/-netz setzen, dann im aufklappenden Menü Sperrfläche -> Nur Autorouting -> (Lage auswählen) -> Einzelelemente -> (Fläche auswählen).

Die einzelnen Autorouter-Parameter sind im BAE-Autorouter-Handbuch dokumentiert, teilweise auch mit Bildern, die die Wirkung illustrieren sollen. Besonders interessant sind diese Links:

sowie die einzelnen darin verlinkten Parameter-Erklärungen.

Generell gilt, je feiner das Autorouter-Raster, desto besser kann er die gewünschte Bauteil-Anordnung entflechten, aber desto feiner müssen die Leiterbahnen werden und desto länger rechnet er am Ergebnis. Die minimalen Strukturabmessungen sind in der Regel ein Prozessparameter der nachfolgenden Fertigung und daher von vornherein gesetzt. Die Fähigkeit des Routers, das Layout zu entflechten, kann man auch durch die Einstellung eines sogenannten Halbrasters verbessern, ohne dass es feinerer Strukturgrößen bedarf, und schließlich kann das Routing auch rasterfrei erfolgen (wobei die eingestellten Bahnbreiten und -abstände natürlich weiterhin benutzt werden). Dabei steigt jeweils der Rechenaufwand an.

Wenn für bestimmte Netze eine größere Bahnbreite oder größere Abstände

als die Standardparameter des Autorouters benötigt werden (bspw. GND

und Vcc, sofern diese nicht ohnehin vollständig mit der Hand verlegt

worden sind), dann kann man im Schaltplan die sogenannten

tag-Symbole att_rw (route width) und

att_md (minimal distance) an die entsprechenden Netze

anhängen. Diese Symbole befinden sich in der Bibliothek

route.ddb.

Generell arbeitet der Autorouter am besten, wenn er Vorzugsrichtungen für die einzelnen Lagen erhält, da er dann besser mit dem Verlegen der Bahnen starten kann. Der Flächenverbrauch der Vias sollte nicht unterschätzt werden, gerade wenn vielpinnige ICs mit feinem Anschlussraster aufgefächert werden müssen. Sinnvollerweise wählt man für die Autorouter-Vias (über Leiterbahnen -> Definieren Via(s)) daher die kleinste Via-Größe aus, die technologisch sinnvoll herstellbar ist.

Nach dem Autorouter-Lauf empfiehlt es sich, dass man die vom Autorouter teilweise sehr "zappelig" verlegten Bahnen glätten lässt: Leiterbahnen -> Weitere Funktionen -> Bahnbegradigung -> Alle Bahnen auswählen -> OK.

Arbeiten mit hierarchischen Blöcken

Gelegentlich benötigt man in einem Projekt einzelne Teile der Schaltung und des Layouts mehrfach in gleicher Form. In diesem Falle bietet sich die Arbeit mit hierarchischen Blöcken an.

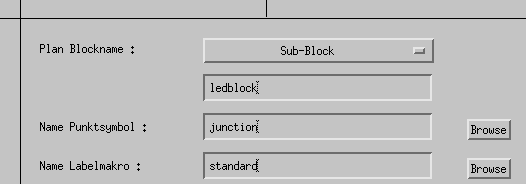

Dabei entwirft man zuerst den wiederkehrenden Teil der Schaltung auf einem eigenen Schaltplanblatt. Dieses Schaltplanblatt wird unter "Einstellungen" -> "Einstellungen" als "Sub-Block" gekennzeichent, der einen Namen bekommt:

Der Block selbst wird dabei mit seiner Umgebung verbunden, indem er globale Labels (wie GND oder VCC) benutzt sowie sogenante Modulports ("Symbole" -> "Neuer Modulport"), die in jeder Instanz des Sub-Blocks einen eigenen Anschlusspunkt nach außen bilden. Der komplette Schaltplan eines solchen Sub-Blocks sieht dann beispielsweise so aus:

Für den Sub-Block legt man im Projekt ein eigenes Schaltplansymbol an, das den gleichen Namen bekommt wie der Blockname. Alle Modulports müssen in diesem Symbol als Pin auftauchen. Mit "Symbollogik editieren" legt man das Symbol als virtual fest und fügt eine call-Anweisung ein, die den Namen des Schaltplanblocks benennt (der in der Regel ja identisch zum Symbolnamen ist):

part ledblock : virtual {

call ledblock;

pin (ctrl);

}

Dieses Symbol wird anschließend im übergeordneten Schaltplan

entsprechend der gewünschten Anzahl der Sub-Blöcke angeordnet und

verdrahtet:

(Die globalen Labels sind in der Netzliste automatisch miteinander verbunden, wie auch sonst üblich.)

Beim Erstellen des Layouts beginnt man zweckmäßig damit, den Sub-Block selbst zu erstellen. Dabei sollte darauf geachtet werden, dass alle Verbindungen, die die Sub-Blöcke in ihrem späteren Verbund untereinander haben sollen (hier also GND und VCC) mit ausreichend Überlappung im Kupfer ausgeführt werden, sodass sie bei Vervielfältigen dann miteinander Kontakt bekommen. BAE erkennt dabei automatisch, dass diese miteinander elektrisch verbunden sind und zu einem Netz gehören, auch wenn sie durch Kopieren aus mehreren Teilstücken entstanden waren.

Der fertige Sub-Block könnte dann im Layout ungefähr so aussehen:

(Die beiden grünen Leiterzüge sind VCC und GND, mit denen die Blöcke dann später verbunden werden. Das blaue Quadrat auf Ebene Bestückungsplan dient nur der Orientierung, um die Blockgrenzen zu markieren. Der farblich hervorgehobene Leiterzug ist der Modulport "CTRL", an den später weitere Leitungen anzuschließen sind.)

Nun gibt es zwei Möglichkeiten, diese Sub-Blöcke zu replizieren. Die erste findet sich unter "Bauteile" -> "Weitere Funktionen" -> "Hierarchie-Kopie":

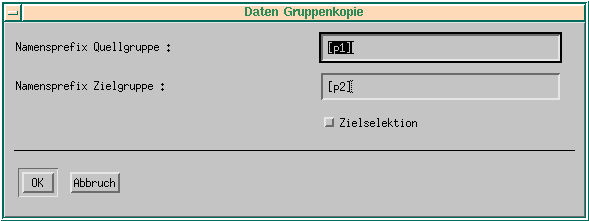

Die Bauteile der einzelnen Subblöcke bekommen Namenspräfixe der Form "[pN]", wobei N eine aufsteigende Zahl ist. Die Hierarchie-Kopie stellt dabei fest, dass die Bauteile des Blocks "p1" bereits platziert sind und bietet den nächsten noch nicht platzierten Block automatisch als Voreinstellung für die Kopie an, in diesem Falle also "p2".

Die Checkbox "Zielselektion" legt fest, ob die kopierten Bauteile anschließend als neue Gruppenselektion erhalten bleiben sollen, falls man mit diesen noch weitere Operationen vornehmen möchte (beispielsweise Drehen der ganzen Gruppe, was bei der Hierarchie-Kopie selbst nicht möglich ist). Bequem ist hier die Funktion, dass man über die linke (oder rechte, wenn global in den Einstellungen geändert) Maustaste jeweils die letzte aus einem Menü ausgewählte Operation erneut ausführen kann.

Nachdem man die Bauteilblöcke kopiert hat (gegebenenfalls sollte man dazu in den Raster-Einstellungen den Winkel freigeben, um nicht nur vertikal, horizontal und im Winkel von 45° kopieren zu können), sieht das Bild dann so aus:

Es ist zu erkennen, dass die Hierarchie-Kopie nur die Bauteile kopiert, nicht aber die Leiterbahnen. Das sollte nicht verwundern, schließlich ist sie ja Teil des Menüs "Bauteile". Die Leiterbahnen kann man aber anschließend als gewöhnliche Gruppenkopie vervielfältigen, da es hier ja keine Besonderheiten bezüglich Bauteilnamen etc. gibt. Sofern sich noch nichts anderes als der Sub-Block im Layout befindet, geht das Erstellen der Gruppe einfach über "Bearbeiten" -> "Weitere Funktionen" -> "Selektieren" -> "Alle Leiterbahnen".

Hier das Layout nach dem Kopieren der Leiterbahnen:

Eine alternative Möglichkeit existiert in neueren (ab Mitte 2010) BAE-Versionen: "Bearbeiten" -> "Weitere Funktionen" -> "Matrix-Kopie". Wenn diese Funktion feststellt, dass der aktuell als Gruppenselektion ausgewählte Bereich einen platzierten Block darstellt, zu dem weitere unplatzierte Blöcke existieren, dann schlägt sie die Möglichkeit vor, die Matrixkopie auf diese Blöcke anzuwenden; dies ist am Button mit dem Text "[p1] 15 benannte Blockkopie(n)" zu erkennen, den man dafür dann betätigt:

Anschließend muss man nur noch die Position des zweiten Blocks relativ zum ersten vorgeben, und bekommt alle 15 weiteren Blöcke angeordnet:

Da es sich um eine Gruppenkopie handelt, werden hier auch die Leiterbahnen mit kopiert, die sich in der Gruppe befinden.

(Derzeit (2011-06) hat diese Matrixkopie noch einen Schönheitsfehler: die Sortierung erfolgt alphabetisch und nicht numerisch, es entsteht also eine Matrix "p1", "p10", "p11", ..., "p15", "p2", "p3", ... Einen Patch dafür kann der BAE-Support oder Jörg Wunsch bei Bedarf liefern, wird aber sicher auch bald im offiziellen BAE drin sein.)

Hier noch das fertig geroutete Layout als Beispiel:

Gerber-Ausgabe

BAE kann Gerberdaten erzeugen. Es ist sinnvoll, diese vor dem Herausgeben zur Produktion mit einem externen Gerberviewer zu kontrollieren. Näheres zu Gerberviewern findet sich unter Gerber-Tools.

AVR-Bauteilbibliothek

Datei:BAE-AVR.zip (Mittlerweile auch "offiziell" bei BAE Contrib)

Das Zip-Archiv enthält zwei Dateien: avr.ddb (die eigentliche Bauteilbibliothek) und avr.def (die Loglib-Quelldatei). Zwar wurden die logischen Bibliothekselemente bereits mit dem loglib-Kommando in die DDB-Datei übertragen, aber die Quelldatei enthält zusätzlich noch Benutzungshinweise als Kommentar.

Die in der DDB-Datei als Element enthaltenen AVR-Typen beziehen sich jeweils auf die älteste Bezeichnung eines AVRs mit dem entsprechenden Pinout (viele Elemente in dieser Bibliothek sind schon ein paar Jahre alt). So wird man also vergeblich einen ATmega324PA darin suchen, weil dessen Pinout erstmals beim AT90S4434 aufgetaucht ist.

Als besondere Schwierigkeit gibt es AVRs in teilweise nicht gleich nummerierten Gehäusen. Insbesondere die älteren AVRs gab es noch in PLCC-Ausführungen, die eine völlig andere Pin-Nummerierung benutzen. Auch Dinge wie mehr GND- und Vcc-Pins bei TQFP-Gehäusen im Vergleich zu DIP machen es einem EDA-System leider nicht so einfach, so eine Bibliothek universell aufzubauen. Es genügt hier nicht mehr, das Attribut $plname (physical library name) zuzuweisen, mit dem man normalerweise Gehäuse und Pinout für ein Bauteil festlegt, sondern man muss mit dem Attribut $rlname (requested logical library name) arbeiten.

Die Tabelle listet die möglichen Zuordnungen der Bauformen sowie einige Alternativtypen zum jeweiligen Basistyp. Die Spalte $rlname listet dabei aus Gründen der Übersichtlichkeit nur den Suffix des Attributs $rlname, voranzustellen ist noch jeweils der SCM-Bauteilname. Ein ATmega16 im TQFP-Gehäuse muss also ein $rlname mit dem Wert at90s4434fp bekommen.

| SCM-Bauteilname | Mögliche AVR-Typen | $rlname | Gehäuse |

|---|---|---|---|

| at90s2313 | AT90(L)S2313, AT90(L)S1200 | (leer) | DIL20 |

| ATtiny2313 | so | SOIC20 | |

| so | SSOP20 (1200 only) | ||

| at90s2323 | AT90(L)S2323 | (leer) | DIL8 |

| so | SOIC8 | ||

| at90s2333 | AT90(L)S2333, AT90(L)S4433 | (leer) | DIL28 |

| ATmega8, ATmega48/88/168 | fp | TQFP32 | |

| at90s2343 | AT90(L)S2343 | (leer) | DIL8 |

| ATtiny11/12/13/15/25/45/85 | so | SOIC8 | |

| qfn | QFN20/MLF20 | ||

| at90s4414 | AT90(L)S4414, AT90(L)S8515 | (leer) | DIL40 |

| ATmega8515, ATmega162 | plcc | PLCC44/PLCC44s | |

| fp | TQFP44 | ||

| at90s4434 | AT90(L)S4434, AT90(L)S8535 | (leer) | DIL40 |

| ATmega16, ATmega164/324/644 | plcc | PLCC44/PLCC44s | |

| fp | TQFP44 | ||

| at90usbx2 | AT90USB162, AT90USB82 | (leer) | VQFP32 |

| atmega103 | ATmega103(L), ATmega128(L) | (leer) | TQFP64 |

| ATmega1281, ATmega2561 | |||

| atmega1280 | ATmega640, ATmega1280, | (leer) | TQFP100 |

| ATmega2560 | |||

| attinyx4 | ATtiny24, ATtiny44, ATtiny84 | (leer) | DIL14, SOIC14 |

| qfn | QFN20, MLF20 |

Falls beim Packager-Lauf die Fehlerausschrift kommt: "Logische Bibliothek nicht gefunden: at90s4434fp", muss die logische Bibliothek noch in die Zieldatei kopiert werden. Die einfachste Methode dafür wäre es, mittels des loglib-Kommandos einfach die komplette avr.def-Datei (und damit alle darin enthaltenen logischen Bibliotheken) auf die Zieldatei zu kopieren:

loglib avr.def meinprojekt.ddb

Wer es gern "sauber" haben möchte, kopiert stattdessen nur die tatsächlich benötigte logische Bibliothek. Methode 1 benutzt dafür die Kommandozeile und das Kommando copyddb:

copyddb avr.ddb meinprojekt.ddb -ms -llib at90s4434fp

Methode 2 geht über die Menüs im Schaltplaneditor: Datei -> Library Utilities -> Elemente kopieren -> Logische Bibliothek -> Dateiauswahlbox Quelldatei, avr.ddb auswählen -> Elementauswahlbox, at90s4434fp auswählen -> Dateiauswahlbox Zieldatei, meinprojekt.ddb auswählen -> Menü Alles kopieren auswählen.

(at90s4434fp und meinprojekt.ddb sind natürlich nur Beispielnamen.)

Weblinks

- bartels.de - Herstellerseiten

- BAE Dokumentation - pdf-Dateien auf den Herstellerseiten