JTAG

Joint Test Action Group, entwickelte den Standard IEEE 1149.1. Das JTAG-Protokoll ermöglicht das Programmieren, Debuggen und Testen von ICs, Prozessoren und FPGAs direkt in der Schaltung.

Hardware

AVR JTAG

- AVR JTAGICE (gelegentlich auch JTAGICE mkI genannt) von Atmel.

- AVR JTAGICE mkII von Atmel.

- AVR JTAGICE 3 von Atmel.

- ATMEL-ICE von Microchip/Atmel.

- AVR Dragon von Atmel.

- AVR077: Opto Isolated Emulation for the DebugWIRE (auch für AVR JTAGICE mkII nützlich)

- Evertool und Evertool light von Martin Thomas. Evertool unterstützt JTAG analog zu AVR JTAGICE und ISP nach STK500 Protokoll. Evertool light nur JTAG.

- JTAG for AVR processors bei Aquaticus ROV. (Englisch)

- AVR-JTAG und AVR-USB-JTAG von Olimex (kommerziell). Alternativer Lieferant ist der Elektronikladen.

- AVR-JTAG und AVR-USB-JTAG von gadgetPool (kommerziell)

- IsoJtagISP und IsoJTAG von Floppy Sponge Automation (USB, optisch isoliert). Hier eine modifizierte Version von Madwizard.

- JTAGAVRU1 (AVR JTAGICE kompatibel, USB, 1.8-5.5V) (existiert wohl nicht mehr ?)

- JTAGcable II (AVR JTAGICE kompatibel, USB, 1.8-6 V)

- MB-JTAG-TWICE (AVR JTAGICE kompatibel, RS232, 2.7-5.5V, +ISP STK500v2) - Free update to version compatible with AVR JTAG MKII (coming soon)

Pinout AVR-JTAG

AVR benutzt einen 10poligen IDC-Stecker mit 2,54 mm Pinabstand und folgendem Pinout:

| Signal | Pin | Pin | Signal |

|---|---|---|---|

| TCK | 1 | 2 | GND |

| TDO | 3 | 4 | VTref |

| TMS | 5 | 6 | nSRST |

| (frei) | 7 | 8 | (nTRST) |

| TDI | 9 | 10 | GND |

| Signal | Pin | Pin | Signal |

|---|---|---|---|

| TCK | 1 | 2 | GND |

| TDO | 3 | 4 | VTref |

| TMS | 5 | 6 | nSRST |

| Vcc | 7 | 8 | (nTRST) |

| TDI | 9 | 10 | GND |

Bemerkungen:

- VTref muss beschaltet werden, von dieser Spannung werden die Pegelwandler des JTAG-ICE gespeist, und das ICE weigert sich zu arbeiten wenn keine Spannung anliegt

- nTRST wird vom JTAG ICE nicht benutzt, soll aber aus Kompatibilität mit anderen JTAG-Implementierungen frei bleiben

- Pin 7 war in der ersten Version des Atmel JTAG ICE als Vsupply bezeichnet und diente dort der Speisung des JTAG ICE aus der Zielhardware

- nSRST muss nicht zwingend an /RESET des AVR gelegt werden; wenn er fehlt, kann das JTAG ICE eine schlafende CPU nicht wecken oder mit einem Controller arbeiten, dessen JTAG-Schnittstelle von der Software außer Betrieb genommen worden ist (Bit JTD im Register MCUCSR)

AVR-JTAG lässt sich mit anderen JTAG-Implementierungen (oder weiteren AVRs) zu einer daisy chain verketten; dabei schiebt jeder AVR 4 Bits.

ARM JTAG

USB Anschluss auf Basis des FTDI FT2232

Diese Adapter funktionieren mit Opensource-Tools wie OpenOCD (ARM-Debugger), xc3sprog (Xilinx Programmer), urjtag (generisches JTAG-Tool), gojtag, etc. Manchmal sind leichte Anpassungen des Source nötig. Bei einigen Adaptern ist auch die serielle Schnittstelle (3.3V-Level) herausgeführt.

- USB to JTAG Interface von Hubert Högl, Schaltplan

- USB JTAG Interface für usbprog und OpenOCD von Benedikt Sauter (Zurzeit gibt es Bausätze für 22€. Der Adapter ist ein Universaladapter der mit verschiedenen Firmwares zu verschiedenen Geräte werden kann. Pläne, Quelltexte usw... Open Source!!!)

- Amontec JTAGkey, JTAGkey-Tiny - Firma Amontec existiert nicht mehr, JTAGbox von Bitrelle ist abwärtskompatibel zu JTAGkey, JTAGkey-2, etc.

- ICEbear ICEbear (Plus|Light) JTAG adapter, spezielle Unterstützung für Flashen/Debuggen von Analog Devices Blackfin-Plattformen.

- EKK-LM3S811 von LMI. Auf dem Testboard ist ein "on-board" JTAG-Adapter, der zu Ansteuerung des LM3S811 auf dem Board genutzt wird, aber auch an externe Controller angeschlossen werden kann. (Alle LMI Testboards verfügen über den JTAG Ein- und Ausgang.)

- SEGGER J-Link sehr professioneller schneller JTAG Adapter. Für nichtkommerziellen Einsatz gibt es den J-Link Edu schon für 50€.

- ARM-USB-OCD von Olimex

- Xverve Signalyzer Tool

- Bitrelle JTAGbox läuft mit OpenOCD, galvanisch vom Target getrennt

Parallelport-Anschluss (Wiggler und Wiggler-"kompatibel")

- Macraigor Original Wiggler

- Olimex ARM-JTAG Wiggler-Nachbau

- k9spud Wiggler-Schaltplan

- bigakis Wiggler-Schaltplan (74HC244 Levelshifter, BC547 Transistor zum Invertieren)(Webarchiv-Link,Orginal gelöscht)

- Wiggler Schaltplan von OpenWRT (ebenfalls mit 74HC244).

- ST FlashLink JTAG Programming Cable STM Application-Note

Man findet einige Schaltpläne für Wiggler-Nachbauten im Netz. Nicht alle sind identisch. Der original Schaltplan von Macraigor ist meines (M. Thomas) Wissens nicht verfügbar.

"Vollständige" Belegung des Wiggler-Clones von Olimex (Quelle: sparkfun-Forum)

- DB25.2 → INVERSE → JTAG.15 (NTRST) (mthomas: hier ist wohl nSRST gemeint)

- DB25.3 → JTAG.7 (TMS)

- DB25.4 → JTAG.9 (TCK)

- DB25.5 → JTAG.5 (TDI)

- DB25.6 → JTAG.3 (TRST)

- DB25.9 → VCC for the Level shifter i.e. JTAG enable/disable

- DB25.11 ← JTAG.13 (TDO)

- DB25.13 ← Target VCC sense (only when JTAG is enabled i.e. DB26.9 = 1)

DB25.18, DB25.19, DB25.20, DB25.21, DB25.22, DB25.23, DB25.24, DB25.25 werden mit GND verbunden.

Soll das Wiggler-Interface auch mit der Software ocdremote von Macraigor genutzt werden, ist eine Brücke zwischen zwischen DB25.8 und DB25.15 einzubauen. ocdremote ab (ca.) Version 2.06 erkennt daran das original Wiggler und auch einen mit der Brücke ausgestattenen Nachbau. Nutzt man zur Ansteuerung andere Software (z. B. OpenOCD oder H-JTAG) wird diese Verbindung nicht benötigt.

Man beachte die Beschaltung von SRST und TRST:

Üblicherweise wird Pin DB25.2 des Druckeranschlusses über eine Inverterschaltung (NPN Transistor) mit dem Reset-Pin des ARM-Controllers verbunden (nSRST).

Pin DB25.6 des Druckeranschlusses wird über Levelshifter direkt mit dem TRST-Pin des Controllers verbunden. In manchen Schaltplänen findet man auch für TRST einen Inverter, aber dies scheint eher unüblich.

Bei den sonstigen Pinbelegungen herrscht weitestgehend Einigkeit. Man muss lediglich Levelshifter (Pegelwandler) zwischenschalten, um zwischen den 5V des Druckeranschlusses und der Spannung des Controllers (üblicherweise 3,3V) zu "übersetzen".

Allein ein 74HC244 als Levelshifter, wie in vielen Schaltungen verwendet, ist nicht ideal. Der Baustein wird dabei mit 3,3V aus der Zielschaltung betrieben und die Anpassung an die nominell 5V vom Druckerport an die 3,3V des HC244 erfolgt entweder durch Spannungsteiler oder durch Strombegrenzungswiderstände und die internen Überspannungsschutzdioden. Das Ausgangssignal TDO zurück zum Druckeranschluss ist maximal 3,3V. Beides nicht optimal aber es funktioniert zumindest meistens. Aufwändigere Schaltungen, wie z. B. der Olimex Wiggler-Nachbau ("ARM-JTAG"), nutzen eine Kombination aus einem 74AC244 und einem 74LCX244.

sonstige

- ARM-JTAG-COOCOX, CoLinkEX Nachbau von Olimex, unterstützt JTAG sowie SWD

- unterstützte uC

- unterstütze IDEs: Keil MDK-ARM 4.03 oder neuer, IAR Embedded Workbench 5.xx oder neuer sowie die CooCox CoIDE

- Abatron BDI2000

- Amontec JTAG Accelerator, Chameleon POD

- AZ-Electronics

- JtagConnection

- Lauterbach Trace

- Macraigor Systems LLS

- Peedi

- Rowley Associates CrossConnect

Anschlussbelegung

Auf Evaluation-Boards verschiedener Hersteller (z. B. Atmel, IAR, Keil, Olimex) ist die JTAG-Schnittstelle über einen 20-poligen Wannenstecker (2x10, Raster 2,54mm) herausgeführt.

Signal Nr. Nr. Signal Vcc 1 2 NC nTRST 3 4 GND TDI 5 6 GND TMS 7 8 GND TCK 9 10 GND GND 11 12 GND TDO 13 14 GND nRESET

nSRST15 16 GND NC 17 18 GND NC 19 20 GND

Neuerdings propagiert ARM eine sehr kompakte Variante mit 2x5 Pins in einem 1,27 mm Raster:

Signal Nr. Nr. Signal Vcc 1 2 TMS GND 3 4 TCK GND 5 6 TDO RTCK 7 8 TDI GND 9 10 nRESET

nSRST

Daneben existiert noch eine weniger gebräuchliche aber dokumentierte Variante mit 14 Polen (2·7).

Bei fertigen Geräten, für die keine Schaltpläne vorliegen, muss man sich die herstellerspezifische Anschlussbelegung anhand des Datenblatts des verwendeten Controllers und mittels Messgerät selbst ermitteln.

Cortex Debug Connectors von ARM

In diesem PDF Dokument hat ARM die Anschlussbelegung für Cortex-Prozessoren definiert.

Signal Nr. Nr. Signal Vcc 1 2 SWDIO

TMSGND 3 4 SWDCLK

TCKGND 5 6 SWO

TDOKey

(kein Pin)7 8 NC

TDIGNDDetect 9 10 nRESET

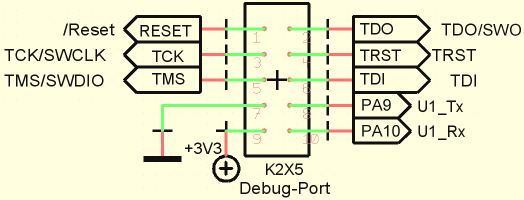

Der 10-polige JTAG Stecker von mmvisual (ARM, Cortex, Seriell kombiniert)

mmvisual hat mit dieser Steckerbelegung die Standard JTAG Schnittstelle erweitert:

Ich habe einen 10-poligen Debug-Stecker entworfen, der alle Varianten sowie einen UART-Anschluss enthält und die Pins optimal angeordnet sind. Mit diesem Stecker können ARM7/9 und Cortex CPUs programmiert werden. An allen JTAG-Steckervarianten fehlen leider Funktionen, bzw. die Pins waren nicht optimal angeordnet. Daher habe ich den "perfekten" Stecker designt der viele Funktionen beinhaltet.

Die Funktionen

- JTAG

- SWD

- Debug-UART-Anschluss (verbunden mit einem freien UART vom STM32) (alternativ ein MAX232 Chip dazwischen schalten)

- Weniger Platzbedarf auf der Platine (Standard-JTAG 20 Polig)

- Über 4-Poligen Würfel kann der UART benutzt werden (Pin 7/8/9/10)

- Es kann ein Jumper gesteckt werden für eine Option (Pin 9/10) ohne dass es sich mit dem RS232 Chip beißt (sofern er eingebaut wurde)

- Über einen 5-Poligen einreihigen Stecker kann SWD verwendet werden (Pin 1/3/5/7/9)

- den ganzen Stecker braucht es nur, wenn man den herkömmlichen JTAG nutzen möchte.

- Kurzschlussschutz, da GND und +3V3 nicht gegenüber liegen

In all meinen Projekten verwende ich nur noch diese Anordnung, denn sie ist einfach praktisch. Alles drauf und die Pins sind perfekt angeordnet für jede Art der Anwendung.

In diesem Beispiel ist der UART 1 (STM32) benutzt mit den Pins PA9/PA10. Wenn die Boot-Pins auf einen separaten Jumper-Block gelegt werden, so könnte auch mit der ST Software ein Flash Update durchgeführt werden.

Hier die Erklärung warum es die BOOT-Pins nicht auf dem JTAG-Stecker benötigt. Ich habe mir einen eigenen Bootloader geschrieben, der kommt ohne das Interne Boot-ROM (und ohne die BOOT-Pins) aus. Ich habe den in die ersten 8KB Flash programmiert.

- Das PC-Programm senden über den UART den Befehl "GoTo Bootloader", damit wird mein Bootloader angesprungen.

- Dann sendet das PC Programm die Update-Daten.

- Wenn fertig, dann geht es zurück in die Applikation.

- Der Bootloader ist immer beim Einschalten des Boards aktiv. Sobald eine Tastenkombination gedrückt wird, bleibt er "hängen" und irgend welche LEDs blinken. Also wenn das Flash "Zerschossen" sein sollte kann man mit einem Restart/Tasten den Bootloader aktivieren und erneut den Update ausführen.

- Der ST eigene Bootloader hat mir nicht gefallen, weil da keine LED's Blinken und dem User sagen, "Hallo ich lebe und bin im Bootloader".

- Wenn die Tasten beim Einschalten nicht gedrückt werden, dann springt der Bootloader in die Applikation

- Der Bootloader kann jeden beliebigen UART nutzen.

Die Adapterplatine

Mit der Adapterplatine kann von dem 10-poligen Stecker auf einen 20-poligen Standard JTAG Stecker verbunden werden. Zusätzlich ist hier ein TTL/V24 Wandler integriert um die UART Signale auf V24 um zu setzen. Hier kann der Schaltplan/Layout geladen werden: Datei:10-Pol-JTAG.zip Die Platine ist 33×19mm klein.

10-pin JTAG im 20'tel-Zoll Raster

- Forumsbeitrag "neuer JTAG-Stecker für ARM"

- Keil ULINK2 (und Pinouts anderer JTAG-Stecker)

MSP430 JTAG

Anschluß an Parallelport:

- Olimex MSP430 JTAG (PDF) bzw. ((GIF)). Siehe auch Diskussion im Forum.

- Forumsbeitrag mit Anhang eines chinesischen? Schaltplans (PDF)

Anschluß an USB/Seriell:

- GoodFET von Travis Goodspeed. The GoodFET is an open source tool for programming microcontrollers and memories by SPI, I2C, JTAG (MSP430, ARM), and a slew of vendor-proprietary protocols. (Stub für 26C3 Vortrag)

FPGA JTAG

- Für Xilinx

- Xilinx JTAG programmer (CPLD, FPGA)

- Xilinx JTAG XSVF Player mit USBprog (CPLD, FPGA)

- Xilinx Platform Cable I Nachbau - Nachbau des Originalem Xilinx Platform Cable I (DLC9)

- Cheaptag - Xilinx Parallel Jtag programming cable

- XSVF Player FTDI Bitbang - XSVF Player with FTDI Bitbang mode

- XSVF Player FTDI Bitbang for Android - XSVF Player with FTDI Bitbang mode for Android

- Für Altera

- Marsblaster für Altera FPGA, serieller Port

- ALTERA ByteBlaster

- EEBlaster, sehr günstig, kompatibel zu ALTERA USB-Blaster

- Build A ByteBlaster bei www.pyroelectro.com

- USB-JTAG-Adapter, kompatibel zu ALTERA USB-Blaster

- ColdFire BDM Pod

Universal JTAG Hardware

Versaloon

Versaloon is a full-opensource multi-functional platform based on generic USB_TO_XXX protocol, which can now support more than 10 kinds of interfaces including ISP, JTAG, SWD, SPI, IIC and so on. Programming is supported for:

- STM8 support(SWIM)

- STM32 support(ISP/JTAG/SWD) siehe auch Forumbeitrag von Bingo [1]

- LPC1000 support(ISP/JTAG/SWD)

- LM3S support(JTAG/SWD)

- AT91SAM3 support(JTAG/SWD)

- AT89S5X support(ISP)

- PSOC1 support(ISSP)

- MSP430(without TEST) support(JTAG)

- C8051F support(C2/JTAG)

- AVR8 support(ISP/JTAG)

- LPC900 support(ICP)

- HCS08 support(BDM)

- HCS12(X) support(BDM)

- SVF support(JTAG)

Software

AVR JTAG

- AVR-Studio (Windows)

- GDB in Verbindung mit AVaRICE und AVR JTAGICE kompatibler Hardware. (Linux)

ARM JTAG

- OpenOCD - kostenlose Open Source Software, Debug Monitor für GDB (läuft als Server mit eigenem TCP/IP Socket, mit dem sich GDB einfach verbinden lässt), unterstützt zur Zeit 190 verschiedene Prozessoren

- GDB bzw. Insight und auf die ARM JTAG Hardware abgestimmte GDB-Server (OCDRemote, OpenOCD, BDI2000, Peedi)

- H-JTAG und RDI-kompatible Debugger (SDT2.51, ADS1.2, RealView and IAR)

- Herstellerspezifische Software z. B. von Lauterbach

- Komplette kostenlose Open Source Toolchain Eclipse-GDB-OpenOCD, läuft auf Linux/Windows/Mac, unterstützt alle Prozessortypen, die von OpenOCD unterstützt werden

FPGA JTAG

- Altera: Quartus Programmer (quartus_pgm)

- Lattice: ToDo... (Lattice setzt seit 2011 auf die JTAG-Funktionalität des FT2232 und benötigt daher keine speziellen USB-JTAG-Adapter mehr)

- Xilinx: Impact, xc3sprog, ...

Allgemeine Tools

- TopJTAG: boundary-scan software for circuit debugging and flash programming.

- Universal Scan

- UrJTAG: Kommandozeilentool für Boundary Scan, FPGA und CPLD und Speicher lesen und schreiben u.v.a.m., Nachfolger von openwince JTAG Tools.

- goJTAG: graphisches Boundary-Scan-Tool zum manuellen Durchtesten von Verbindungen, besonders für Nicht-JTAG-Experten geeignet. Obwohl in Java geschrieben, funktioniert es nur unter Windows. Funktioniert im Prinzip mit allen FT2232(H) basierten Adaptern.

- FT2232 BoundaryScan Tool: free boundary-scan software for flash programming [S29GL128N, S29GL256N, S29GL512N, M25PX16, M25PX32, M25PX64, etc ].

- [2]: boundary scan test system M-1 for board and system testing, runs on Linux, open source, no licensing ! Read more on http://www.blunk-electronic.de/products.html