RFM12

Beschreibung der Funkmodule RFM01, RFM02 und RFM12.

Benötigt werden in der Minimal-Version im FIFO-Modus nur die Anschlüsse nSEL, SDO, SDI und SCK, eben das komplette SPI-Interface. Der Zugriff auf das Sende- und Empfangs-FIFO ist per Software möglich, ebenso die Abfrage der Statusbits. Deshalb werden z. B. nIRQ und nFFS nicht unbedingt benötigt. nIRQ signalisiert unter anderem, dass das Modul bereit ist Daten zu empfangen. Wenn Daten empfangen wurden, kann dies über den FFIT-Pin abgefragt werden (falls die Füllschwelle eingestellt wurde). nFFS dient dazu das FIFO direkt anzusprechen (es ist quasi der Chipselect für das FIFO), davon wird in der Minimalversion aber kein Gebrauch gemacht. Der Pin muss daher auf high-Pegel gelegt werden! An CLK kann eine Frequenz von 1MHz bis 10MHz eingestellt werden. Hiermit kann dann z. B. der Mikrocontroller versorgt werden. Reset ist ein Open-Collector-Ausgang und gleichzeitig der Reset-Eingang. Er sollte daher entweder gar nicht, oder aber hochohmig angeschlossen werden.

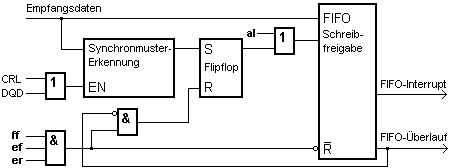

Im FIFO-Mode kann das Modul konfiguriert werden mit dem Empfang zu warten, bis die Daten 0x2DD4 empfangen wurden. Sobald dieses Bitmuster empfangen wurde, werden Daten in das FIFO geschrieben, bis man das FIFO abschaltet und die Mustererkennung neu startet.

Als weitere Modi stehen unter anderem ein synchroner Modus zur Verfügung (no FIFO mode), in dem der Sender/Empfänger den Bittakt ausgibt, und synchron dazu die zu sendenden Daten einliest bzw. die empfangenen Daten ausgibt. Der SPI Bus ist trotzdem zur Initialisierung des Moduls notwendig.

Grundlagen

Wichtig zu erwähnen ist, dass der beim RFM12 von HopeRF verwendete Chip ein SI4420 (RFM12B SI4421) von Silicon Labs ist. Warum HopeRF diesen Chip abschmirgelt bzw unkenntlich macht versteht keiner, denn der Chiptyp ist bekannt. Jedoch ist das Datenblatt von HopeRF teilweise fehlerhaft weshalb das DB von Silicon Labs verwendet werden sollte. Neuanfänger haben es jedoch schwer den Chiptyp herauszufinden, weshalb hier nochmals deutlich mitgeteilt wird, dass es sich um einen "4420" von Silicon Labs handelt!

HF-seitiges Funktionsprinzip

Ich möchte hier etwas das Funktionsprinzip des RFM12 erläutern, da das Verständnis wichtig ist, um die Parameter Frequenzhub, Datenrate, Tiefpassfrequenz usw., daraus folgend Bandbreite und Kanalraster sinnvoll auswählen zu können. Schließlich ist ein sauberer Frequenzplan wichtig für die kollisionsfreie Funktion mehrerer gleichartiger Geräte.

(1)

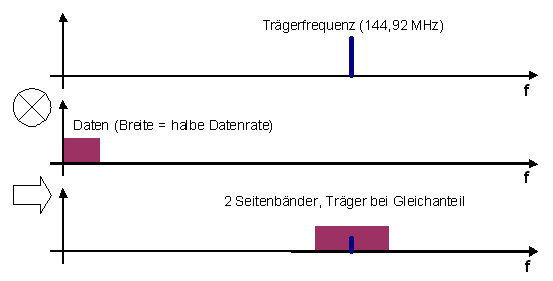

Betrachten wir zunächst die Amplitudenmodulation:

Multiplikation im Zeitbereich bewirkt Faltung im Frequenzbereich.

Das Ein- und Ausschalten eines hochfrequenten Trägers im Takt eines Datensignals ist eine Multiplikation und lässt rings um den Träger zwei Seitenbänder entstehen. Deren Breite ist jeweils die halbe Datenrate, sofern die Daten bandbegrenzt (also verschliffen) werden. Zur einfacheren Rekonstruktion verschleift man das Datensignal deutlich weniger; etwa ein 8-kBit/s-Signal auf 8 kHz (statt 4 kHz). Der RFM12 verschleift die Daten gar nicht.

Ist das Datensignal gleichspannungsfrei (gleich viel +1 wie -1), verschwindet der Träger, und die gesamte Sendeleistung steckt in den Seitenbändern, also der gewünschten Information. Das hilft den Rauschabstand zu verbessern und/oder die Sendeleistung zu verringern (weniger Elektrosmog).

(2)

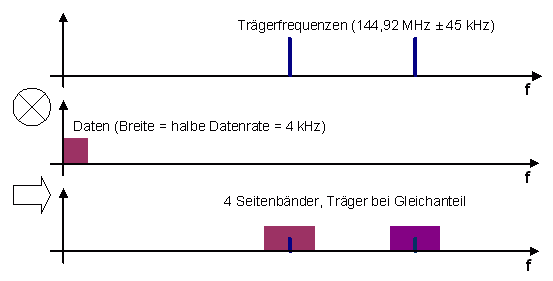

Die Frequenzumtastung (FSK) wird gern als ein Sonderfall der Frequenzmodulation betrachtet. Bei Modulationsgrad η > 1 (der RFM12 kann eh' nichts anderes demodulieren) kann man das Ganze auch als doppelte Amplitudenmodulation interpretieren:

Hier wird die Bandbreitenverschwendung offensichtlich, aber im 433-MHz-Band ist ja genug Platz dafür. FM-Signale lassen sich viel leichter verstärken als AM-Signale: man braucht sie nur durch einen (Energie sparenden, digitalen) Begrenzerverstärker zu schicken.

Da die Sendedaten nicht bandbegrenzt werden (der Träger wird hart umgeschaltet) entstehen theoretisch unendlich breite Seitenbänder, die in einer sinc-Funktion (= sin(x)/x) abfallen.

Das ist möglicherweise der Grund, warum die meisten Beispiele genau in der Mittenfrequenz des 433-MHz-Bandes, nämlich 433,92 MHz, funken und so die übrigen Störer geradezu magisch anziehen. Die Störung außerhalb der Zulassungsgrenzen (433,05 .. 434,79 MHz) ist so definitiv minimal. Beim wesentlich breiteren amerikanischen 915-MHz-Band ist's deutlich entschärfter.

(3)

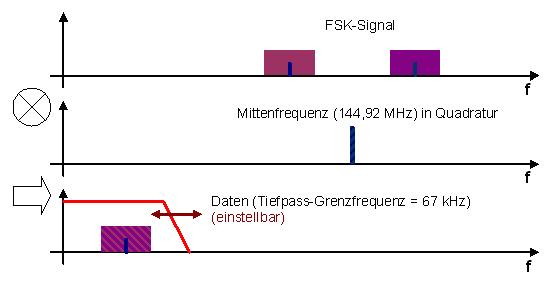

Die Demodulation erfolgt beim RFM12 im Basisband. Es wird also keine Zwischenfrequenz (wie die 10,7 MHz beim analogen UKW-Rundfunk) verwendet. Das FSK-Signal wird (wahrscheinlich) mit der Mittenfrequenz multipliziert, und heraus kommt dieses Bild:

Danach kommt das Signal durch den einstellbaren Tiefpass. Diesen dimensioniert man so, dass der Frequenzhub plus die Nutzsignalbandbreite durchpasst.

Die Multiplikation erfolgt zweimal, mit dem Träger und dem 90° verschobenen Träger. Mit dieser sogenannten I/Q-Demodulation kann man recht viel machen, so AM, FM und PM demodulieren. Die Funktion im RFM12 ist etwa so:

Das gesendete FSK-Signal wird um die Mittenfrequenz gefaltet, somit entsteht eine Differenzfrequenz, unabhängig davon, ob gerade die obere oder untere Frequenz empfangen wird. Sozusagen Spiegelfrequenzdämpfung = 0. Damit könnte man ohne I/Q gar nichts anfangen.

Das Ergebnis der I/Q-Demodulation ist ein umlaufender (komplexer) Zeiger. Die Drehzahl ist gleich der Differenzfrequenz, der Umlaufsinn ist jedoch bei der unteren (Spiegel-)Frequenz anderherum! Man muss also nur noch die Drehrichtung detektieren, genauso wie bei Inkrementalgebern. Das ist einfach ein D-Flip-Flop.

Die beteiligten Schaltfrequenzen liegen im Frequenzbereich des Tiefpasses, also im kHz-Bereich.

(4)

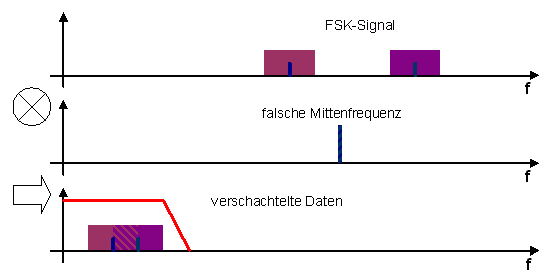

Typischerweise gibt es einen Unterschied zwischen der Sende- und Empfangsfrequenz von ein paar kHz. Entsprechend einer Quarzabweichung im Bereich von 10 ppm oder 1 s pro Tag. Dann ergibt sich folgendes Bild:

Die eingebaute AFC misst die beiden Frequenzen je nach empfangenem Bit (= Frequenzhub = Umlaufsinn hinter dem I/Q-Demodulator), und regelt so, dass die beiden Frequenzen etwa gleich sind. Sie werden also getrennt per Frequenzzähler gemessen.

Die AFC-Schaltung kann nur in 2,5-kHz-Schritten arbeiten, demnach den Frequenzversatz um 5 kHz ändern. Die AFC dient also vor allem dazu, dass das Empfangssignal immer schön durch den Tiefpass passt.

Daher muss man bei der Auswahl der Tiefpass-Eckfrequenz auch die zu erwartende Quarzabweichung mit einrechnen. Diese ist aber im 433-MHz-Bereich noch nicht so relevant.

(5)

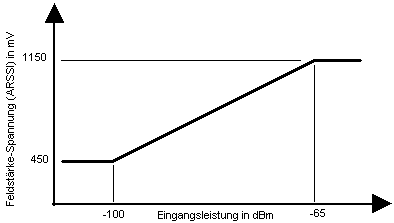

Der ARSSI-Anschluss (analog received signal strength indicator, svw. Feldstärke) hat laut Datenblatt (RFM12B Seite 3) die folgende Kennlinie:

Dieser Anschluss ist bei den RFM12-Modulen nicht herausgeführt, aber an einem der SMD-Kondensatoren leicht abgreifbar. Beispielsweise kann man damit AM oder ASK (Amplitude Shift Keying) demodulieren.

FAQ

Soll ich 433 oder 868 MHz nehmen?

Wähle das für deine Anwendung kleinere der beiden Übel: Bei 433 MHz sind i.d.R. mehr Störer unterwegs und bei 868 MHz sind die maximale Belegungsdauer bzw. das listen-before-talk (LBT) Verfahren gemäß Allgemeinzuteilung zu beachten. Siehe auch im Forum [1] und [2].

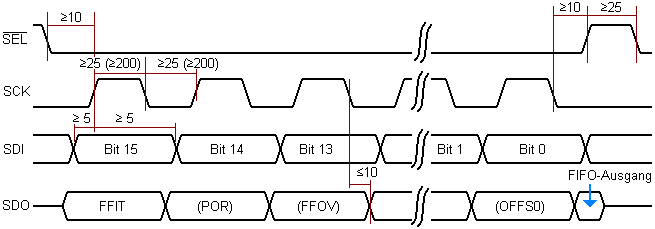

SPI (Serial Peripheral Interface)

Alle Zeiten in ns. Die angegebenen Bits im Datenblatt (RFM12B Seite 13) sind falsch! So wie hier ist es richtig.

- Maximale SCK-Frequenz: 20 MHz

- Maximale SCK-Frequenz zum Auslesen der Empfänger-FIFO (Kommando 0xB000 oder via FFS): 2,5 MHz = 10 MHz {Quarz} / 4

- Nicht zur seriellen Kaskadierung gedacht oder geeignet

- Man kann sich SEL und FFS als zwei separate Chip-Select-Anschlüsse vorstellen; letzterer adressiert direkt die Empfangs-FIFO (sofern er gesetzt) oder das Sende-Latch (andernfalls). Bei ersterem muss man für jedes Byte (mindestens) ein Kommandopräfix 0xB0 und damit 8 Takte voranstellen. Da die Aktivierung von SEL ohne jeden Takt den FIFO-Zustand an SDO meldet, lässt sich so zwischendurch der FIFO-Füllstand überprüfen.

- Welches der beiden Signale SEL und FFS bei gleichzeitiger Aktivierung Priorität hat ist undokumentiert. Vermutlich FFS.

Kann man auf SPI verzichten?

- Auf der RFM12-Seite: nein! Man benötigt SPI zum Einstellen der Frequenz, der sonstigen Sende- und Empfangsparameter sowie zum Ein- und Ausschalten des Sendebetriebs. Wenn man ohne die integrierte Empfangs-FIFO arbeitet, kann man notfalls auf SDO verzichten, da man ohnehin nur Kommandos hinschicken muss. Eine echte Statusabfrage bei Interrupt ist dann nicht möglich.

- Auf der Mikrocontroller-Seite: Es ist freigestellt, ob man die eingebaute SPI-Hardware benutzt oder nicht. Eingebaut läuft schneller; für Empfangs-FIFO-Zugriff muss man aber bei der maximalen Taktfrequenz aufpassen. Außerdem ist man bei der Auswahl der Anschlusspins festgelegt, und man steht in Konkurrenz mit einem SPI-Programmierinterface. Damit das Programmiergerät nicht unbeabsichtigt Kommandos zum RFM12 sendet, muss an SEL ein externer Pull-Up-Widerstand beschaltet werden (oder aber RESET sind verbunden oder RES mit PullDown)! Dies kann Konsequenzen für einen beabsichtigten Schlafmodus haben, siehe unten.

Kann man SEL permanent auf LOW halten?

Jein.

- Ein Kommando beginnt stets mit der High-Low-Flanke von SEL. Mit Masse verbinden darf man den Eingang also nicht.

- Man kann SEL auf LOW halten, um mit der Low-High-Flanke von SDO einen alternativen Sende- bzw. Empfangsinterrupt auszulösen. Das hilft einen Mikrocontroller-Anschluss (das für IRQ) einzusparen und trotzdem Interrupts zu verwenden. Das ist insbesondere bei solchen Controllern vorteilhaft, bei denen man den seriellen Dateneingang mit Pin-Change-Interrupt belegen kann (also ATtiny oder ATmega88, nicht aber ATmega8) und so aufwecken kann.

- Beim RFM12B ist die Möglichkeit ausführlich dokumentiert, das Senderegister fortwährend mit Bytes zu füllen (ohne das Kommandopräfix 0xB8 und weitere 8 Takte pro Byte), High an SDO signaliert jeweils die Bereitschaft dafür. Beim Vorgängertyp (ohne B) ist der entsprechende Passus zweifelhaft formuliert, funktioniert aber wahrscheinlich genauso.

- Im Gegensatz zu FFS enthält SEL keinen Pull-Up-Widerstand, sodass man diesen Anschluss auch im Schlafmodus ohne zusätzlichen Strombedarf nach LOW ziehen darf. Man darf nur nicht vergessen, am entsprechenden Mikrocontroller-Eingang (ATmega: MISO, ATtiny: SDI) keinen Pull-Up zu aktivieren, da SDO des RFM12 zumeist LOW liefert. ACHTUNG! Das RFM12 (ohne B) hat auch am FFS KEINEN Pull-Up-Widerstand

Was passiert, wenn man bei aktivem SEL mehr als 16 Takte ausgibt?

Ist er (Empfängerfreigabe) gesetzt, kann man so die Empfangs-FIFO auslesen. Ab da ist die maximale SCK-Taktfrequenz von 2,5 MHz einzuhalten, sonst kommt Murks. Ist die FIFO nicht entsprechend gefüllt, kommt ebenfalls Murks. Insofern holt das Kommandopräfix 0xB0 die FIFO-Bits nur 8 Takte nach vorn.

Ist er gelöscht ist das Verhalten undokumentiert. Wahrscheinlich erscheint RGIT an SDO, und das Senderegister wird nach je 8 Takten mit einem Byte gefüllt (wie beim Kommandopräfix 0xB8 oder bei Benutzung von FFS).

Sollte man RES mit dem Reset-Anschluss des Mikrocontrollers verbinden?

Jein.

- Tatsächlich ist das vom Hersteller des RFM12 so angedacht!

So kann ein etwas minderbemittelter Mikrocontroller von den Überwachungs- und Stromspar-Features des RFM12 profitieren. Auch spart man sich so den Brown-Out-Detektor eines AVR-Controllers (10 µA) und überlässt das den RFM12 (0,5 µA). - Gelegentlich kommt es vor, dass der RFM12 auf Grund eines ungewollten Kommandos (welches?) oder wackliger Speisespannung RES permanent nach LOW zieht: Deadlock!

Die brutale Methode des Bastlers ist es in diesem Fall, diese Verbindung kurz auf Speisespannung zu klemmen, damit der Mikrocontroller loslaufen und den RFM12 mit entsprechenden Initialisierungskommandos enteisen kann.

Also: Im Allgemeinen ja, bei Mondfahrzeugen oder Omas Fernbedienung in 'zig Kilometer Entfernung würde ich davon erst mal abraten.

Die günstigste Beschaltung für (optionale) 250 kBit/s?

Hier für ATtiny2313 sowie alle ATmega via UART: Keine permanente Bitsynchronisation; eine höhere Bitfehlerrate (BER) durch zeitliche Fehlerkennung des Startbits muss in Kauf genommen werden.

- FFS (nun FSK/DATA (3)) an RxD und TxD

- 100 pF an FFIT (nun CFIL (4)) nach Masse

- Senden und Empfangen mit eingebauter UART in einer Art RS-485:

- Beim Senden müssen Empfangsdaten ignoriert werden

- Beim Empfang muss der TxD-Ausgangstreiber abgeschaltet werden

- Bitsynchronisation gibt's nicht und wird nicht benötigt

- Bytesynchronisation erreicht man am besten durch 1-2 x Aussenden von 0xFF in halber Baudrate (empfängt theoretisch 0xFE), dann Aussenden eines Rahmenstartwortes mit 250 kBaud

- Senden und Empfangen bis 115,2 kBit/s ist ohne Schaltungsänderung mit der eingebauten FIFO weiterhin möglich, da das SPI-Interface ohnehin benötigt wird

CLK-Ausgang bleibt bei 1 MHz

- Vor dem Umschalten (mit 0xC0E0) länger warten.

RFM12 empfängt ein paar Bytes, dann nur Müll

- Es wird zu langsam gesendet (TX FIFO underrun)

- Es wird zu langsam empfangen (RX FIFO overrun)

Die Status-Bits helfen hier beim Debuggen. SPI sollte auf maximaler Transferrate stehen.

RFM empfängt nur Müll

http://www.mikrocontroller.net/topic/73560#605528

Deine Module verhalten sich normal. Man muß mit den Gain- und AFC-Bits eine ganze Weile spielen, bis die Module korrekt laufen (kommt auf die Anwendung an). Fakt ist: der Empfänger empfängt ständig Datenmüll als Rauschen. Wenn der FIFO durch die Präambel getriggert wird, sind die Daten im FIFO ziemlich korrekt, wenn alles "gut" eingestellt ist. Der FIFO sollte per Interrupt dann auch sofort abgeholt werden, da sonst das nächste Byte das alte direkt überschreibt. Jeder zusammenhängende Datensatz (mehrere Bytes an einem Stück) muß von einer Präambel eingeleitet werden. Nach dem kompletten Einlesen eines Datensatzes muß der FIFO abgeschaltet, wieder eingeschaltet und für den Empfang der nächsten Präambel neu scharf gemacht werden. (FifoFill bit)

RFM hängt sich auf

Der Wertebereich für die AFC, der die maximale Abweichung korrigiert, sollte begrenzt werden. Ansonsten können die Offsetbits im Status maximal werden => es geht gar nichts mehr, der Empfänger hängt fest.

edit: Leider bringt die Beschränkung der AFC auf Minimum bei mir keine Verbesserung. Zumindest ist obige Aussage nicht allgemein gültig.

Siehe auch

- Forenbeitrag RFM12: Erfahrungen

- Erklärung im Anhang zur AFC

Kommunikation mit RFM funktioniert nur sporadisch

- Ist die Versorgungsspannung stabil? (evtl. Kondensator einbauen)

Interrupt nIRQ klappt nicht bei 868MHz

Wenn bei der Verwendung der 868er Module die üblichen Sourcen (dasLabor, etc) verwendet werden, müssen einige Änderungen gemacht werden, die sich leicht finden lassen. Ohne weiteres funktionierte der blockierende Empfang, der Interruptbetriebene (nIRQ) machte in mindestens einem Fall Probleme. Hier half die Anpassung des FIFO IT Level . In vorhandenen Sourcen ist 0xCA83 zu finden, eine Änderung auf 0xCAF3 hilft dabei.

Bei Interruptbetrieb ist darauf zu achten, dass wirklich auf jeden Interrupt reagiert wird. Solange ein Interrupt nicht behandelt wird bleibt nIRQ auf LOW! Durch das Lesen des Statusregisters können alle Interrupts ausser FFIT und RGIT "gelöscht" werden. Für FFIT ist das FIFO zu lesen und für RGIT das TxRegister zu beschreiben.

Was passiert, wenn ich beim Senden die Daten nicht schnell genug liefere?

Es kommt zum Interrupt wegen Latch-Unterlauf.

Der Sender wiederholt die letzten beiden Bytes im Wechsel. Er wird nicht abgeschaltet.

Die maximale erlaubte Latenzzeit zwischen Auftreten des Interrupts und Einschreiben des letzten der 8 Bits beträgt 8 Bitzeiten.

Was passiert, wenn ich beim Empfang die Daten nicht schnell genug abhole?

Es kommt zum Interrupt wegen FIFO-Überlauf.

Logisch wäre, die ältesten Bits werden verworfen. Laut Doku wird hingegen das weitere Schreiben der FIFO unterbunden, bis die FIFO hinreichend geleert ist und das Synchronwort (typisch 0x2DD4) erneut erscheint.

Vorausgesetzt, der Interrupt ist bei FIFO-Füllstand 8 Bit gesetzt (Voreinstellung), beträgt die maximale Latenzzeit zwischen Auftreten des Interrupts und Abholen des ersten Bits aus der FIFO 7 Bitzeiten, für jedes weitere Bit eine Bitzeit mehr.

Bei derart knapper Kalkulierung muss der Interrupteingang pegelgetriggert sein! Bei Verwendung eines flankengetriggerten Interrupts (Pin-Change-Interrupt) sollte die Interruptbedienungsroutine (ISR) die Pegeltriggerung simulieren, indem der Kode so lange in einer Schleife ausgeführt wird, bis der Interrupteingang inaktiv geworden ist.

Was passiert, wenn der Empfangsdatenstrom abbricht?

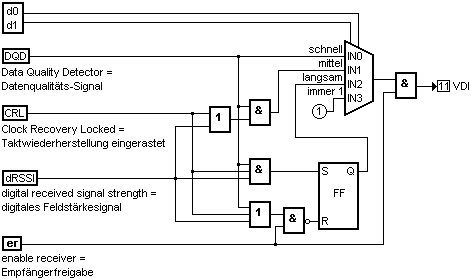

DQD wird inaktiv. Das kann man mittels Status-Read abfragen. Oder mit dem Extra-Ausgang VDI. Die Erkennung ist jedoch mehr oder weniger verzögert und kann nicht als echte Endekennung herangezogen werden.

Der Empfang, die Taktrückgewinnung und das Daten-Schieben laufen einfach in der vorgegebenen Baudrate weiter! Man braucht sich daher nicht um Inter-Character-Timeouts zu kümmern; Daten kommen immer.

Die Datenlänge muss demnach in das Übertragungsprotokoll eingebaut werden, typischerweise:

- mit einer festen Paketlänge

- mit einer Paketlängenangabe am Anfang (dadurch begrenzte Paketlänge)

- mit einer speziellen Endekennung (unbegrenzte Paketlänge möglich; unfair)

Die Wahl der maximalen Paketlänge ist gemeinsam mit der Baudrate ein wichtiges Kriterium für das zeitliche Verhalten des gesamten Funkprotokolls.

Register

Von https://www.mikrocontroller.net/attachment/24947/RFM12.txt

Dieses Dokument beschreibt die Nutzung des RFM12 TRX Moduls!

WICHTIG

Dieses Dokument wurde aus mehreren Quellen zusammengestellt, und kann Fehler enthalten! Es können Abweichungen in Bezug auf RF01 / RF02 / RF12 / RFM01 / RFM02 und andere Module auftreten! Es wurde das Datenblatt vom RFM12B und RF12 von www.hoperf.com als Basis genuzt. Zusätzlich wurden diese Informationen mit Hilfe von Forums-Nutzern (https://www.mikrocontroller.net/topic/71682) weiter vervollständigt!

WICHTIG

Hinweis: Die LNA-Eingangsimpedanz beträgt 250Ω, und muss beim Anschluss einer 50-Ohm-Antenne entsprechend angepasst werden, um das Rauschen zu minimieren! -- (Auf den Pollin-Modulen bereits vorhanden)

WICHTIG

Vor der Einstellung der Konfiguration sollte dem RFM12-Modul ausreichend Zeit für seine Power-On-Sequenz gegeben werden. Manche Module brauchen dazu nur 10ms, manche aber 100ms. Ist die Power-on Zeit zu kurz, können durchaus einige Konfigurationswerte gesetzt sein, andere aber nicht.

Das Datenblatt zum RFM12B schreibt 100 ms vor (wenn auch durch die Blume).

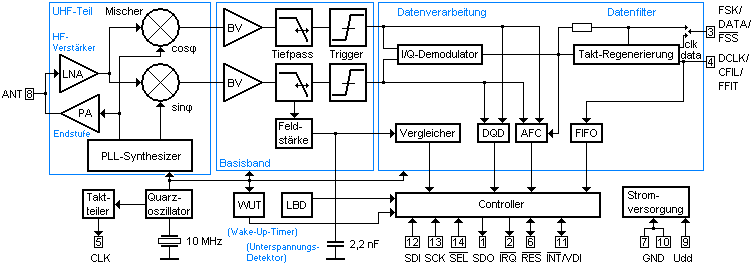

Blockdiagramm

Die angegebenen Pin-Nummern beziehen sich auf das (bei Pollin erhältliche) SMD-Modul.

Grundkonfiguration (Configuration Setting 80xx)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | el | ef | b1 | b0 | x3 | x2 | x1 | x0 | 0x8008 |

| el | enable latch (TX-FIFO) |

Sendepuffer (2 Bytes) für Daten-Senden nutzen. Typischerweise permanent einschalten! |

0 = aus |

|---|---|---|---|

| 1 = ein | |||

| ef | enable fifo (RX-FIFO) |

Empfangspuffer (16 Bits) für Daten-Empfang nutzen. Typischerweise permanent einschalten! |

0 = aus |

| 1 = ein | |||

| b | band (Band) |

Zu nutzendes Frequenzband. Muss in Übereinstimmung mit der Modulbestückung gesetzt werden, insbesondere wegen der Antennen-Anpassung |

00 = 315 MHz |

| 01 = 433 MHz | |||

| 10 = 868 MHz | |||

| 11 = 915 MHz | |||

| x | xtal (Quarz) |

Kapazität des eingebauten Ballastkondensators („Ziehkondensators“) für den Quarzoszillator. Diese sollte entsprechend den Herstellervorgaben des Quarzes ausgewählt werden. Höhere Werte „ziehen“ die Frequenz nach unten. Der exakte Abgleich erfolgt mit einem hochgenauen Frequenzzähler am CLK-Ausgang ⑤ auf bspw. 1 MHz. |

0000 = 8,5 pF |

| 0001 = 9 pF | |||

| ... | |||

| 1000 = 12,5 pF | |||

| 1111 = 16 pF |

Bei el = 0 erscheinen die Daten an DATA und der Takt an DCLK.

Komponentenauswahl (Power Management 82xx)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

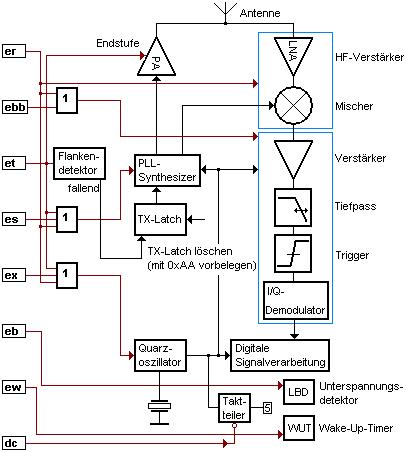

| ← | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | er | ebb | et | es | ex | eb | ew | dc | 0x8208 |

| er | enable receiver | Empfänger-Trakt komplett einschalten (11 mA) | 0 = aus |

|---|---|---|---|

| 1 = an | |||

| ebb | enable baseband | Basisband-Empfangsteil einschalten / eingeschaltet halten (mA-Bereich). Dient zum Verkürzen von Umschaltzeiten |

0 = aus |

| 1 = an | |||

| et | enable transmitter | Sendertrakt komplett einschalten (22 mA bei max. Ausgangsleistung). Der Sender beginnt sofort mit dem Senden. Die beiden Sendepuffer werden beim 1-0-Übergang mit 0xAA (0-1-Bits im Wechsel zur Taktsynchronisation beim Empfänger) gefüllt, können aber vor dem 0-1-Übergang mit einer anderen Präambel besetzt werden. |

0 = aus |

| 1 = an | |||

| es | enable synthesizer | PLL-Synthesizer einschalten oder eingeschaltet halten Dient zum Verkürzen von Umschaltzeiten |

0 = aus |

| 1 = an | |||

| ex | enable xtal (Quarz) |

Schaltet den Quarz-Oszillator ein (3 mA). Der Quarzoszillator hat eine erhebliche Hochlaufzeit von 1..5 ms. |

0 = aus |

| 1 = an | |||

| eb | enable brownout | Aktiviert Betriebsspannung-Überwachung (0,5 µA). Generiert Interrupt bei Unterschreitung einer einstellbaren Schwelle |

0 = aus |

| 1 = an | |||

| ew | enable wakeup | Aktiviert den eingebauten WakeUp-Timer (1,5 µA). Generiert Interrupt nach Ablauf einer einstellbaren Zeit |

0 = aus |

| 1 = an | |||

| dc | disable clock | Deaktiviert die Ausgabe des Taktes auf dem CLK-Ausgang ⑤ Der Takt ist zwischen 1 .. 10 MHz einstellbar kann zur Speisung eines Mikrocontrollers dienen. |

0 = Takt ausgeben |

| 1 = LOW ausgeben |

er bzw. et schalten alle zum Empfangen bzw. Senden benötigten Module (Quarz-Oszillator, PLL-Sythesizer, Basisband-Block) ein auch wenn ebb, es oder ex nicht gesetzt sind. er hat Vorrang vor et.

Durch separates Einschalten von ebb, ex oder es kann aber die Startzeit für den Empfänger bzw. den Sender verkürzt werden. Am nützlichsten ist dies für ex, da die Hochlaufzeit des Quarzes mit einigen Millisekunden deutlich länger ist als die der anderen Komponenten (unter 1 ms).

Wird der WakeUp-Timer verwendet ist ew nach jedem Aufwecken zu löschen und wieder zu setzen.

Ist dc = 0, läuft der Quarzoszillator unabhängig von ex weiter, solange eine Unterbrechungsanforderung (Interrupt) vorliegt. Daher müssen Interrupts unbedingt bedient werden, damit der RFM12 den Oszillator abschalten kann. Der Taktausgang liefert nach einem Status-Lesen, gefolgt vom Abschaltkommando des Quarzes (ex = 0) noch einige (192) Taktimpulse, um den angeschlossenen Prozessor ein paar Befehle bis zum Schlafmodus ausführen zu lassen.

Taktgenerator-Einstellungen (PLL Setting CCxx, nur RFM12B)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | ob1 | ob0 | lpx | dly | ddit | bw1 | bw0 | 0xCC77 |

| ob | output buffer | Legt die Treiberstärke des Taktausgangs CLK ⑤ fest. Höhere Treiberstärke bedeutet steilere Flanken, aber auch mehr Störungen des Empfangsteils |

0x = für ≤ 2,5 MHz |

|---|---|---|---|

| 10 = für 3,3 MHz | |||

| 11 = für 5 oder 10 MHz | |||

| lpx | low-power xtal | Wählt den Low-Power-Mode für den Quarz-Oszillator aus. (Fix 1 in der RFM12B-Dokumentation) |

0 = 1 ms Hochlaufzeit, 620 µA |

| 1 = 2 ms Hochlaufzeit, 460 µA | |||

| dly | delay | Verzögerung im Phasendetektor aktivieren. (Keine weiteren Erläuterungen verfügbar) |

0 = keine Verzögerung |

| 1 = Verzögerung aktiv | |||

| ddit | disable dithering | Schaltet das Dithering in der PLL ab. (Dithering verbreitert ein eventuelles Störspektrum.) |

0 = eingeschaltet |

| 1 = abgeschaltet | |||

| bw | bandwidth | Wählt die Bandbreite des PLL-Signals aus. Angegebene Werte = Phasenrauschen für 1 MHz Offset. (bw1 = 1 in der RFM12B-Dokumentation) |

x0 = -107dBc/Hz für max. 86,2 kBit/s |

| x1 = -102dBc/Hz für max. 256 kBit/s |

Unterspannungs-Detektor und Taktausgangsteiler (LowBatt / µC Clock Control C0xx)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | d2 | d1 | d0 | v4 | v3 | v2 | v1 | v0 | 0xC000 |

| d | divider | Bestimmt den Teilungsfaktor für die Taktausgabe am CLK-Anschluss ⑤. Die Ausgangsfrequenzangaben beziehen sich auf 10 MHz Quarzfrequenz. |

000 = 1 MHz (:10) | 001 = 1,25 MHz (:8) |

|---|---|---|---|---|

| 010 = 1,6 MHz (:6) | 011 = 2 MHz (:5) | |||

| 100 = 2,5 MHz (:4) | 101 = 3,3 MHz (:3) | |||

| 110 = 5 MHz (:2) | 111 = 10 MHz | |||

| v | voltage | Bestimmt die Betriebsspannung, bei der der RFM12 einen Unterspannungs-Interrupt auslöst. Im Power-Managment muss das eb-Bit aktiv sein, damit dies funktioniert. Im Datenblatt zum RFM12B ist v4 = 0 angegeben. |

00000 = 2,25 V, Minimum | |

| xxxxx = (2,25 + 0,1*v) V | ||||

| 11111 = 5,35 V, Maximum (Quatsch) | ||||

Frequenzeinstellung (Frequency Setting Axxx)

Bestimmt die Sende- und Empfangsfrequenz.

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 1 | 0 | 1 | 0 | f11 | f10 | f9 | f8 | f7 | f6 | f5 | f4 | f3 | f2 | f1 | f0 | 0xA680 | |

F = f11 .. f0 = Bestimmt den Offsetwert der Frequenz.

Als Basis gilt das eingestellte Band im Grundeinstellungs-Kommando.

Voreingestellt ist F = 1664 = 0x680.

Zulässig sind nur 96 ≤ F ≤ 3903. Falsche Werte werden beim Einschreiben ignoriert.

f = 10 MHz * C1 * (C2 + F/4000) (gilt für 10-MHz-Quarz)

| Band [MHz] | C1 | C2 | fmin [MHz] | fmax [MHz] | ∆f [kHz] | Vorgabe [MHz] | f berechnen [MHz] | F berechnen (f in MHz) | ISM-Bereich [MHz] |

|---|---|---|---|---|---|---|---|---|---|

| 315 | 1 | 31 | 310,24 | 319,7575 | 2,5 | 314,16 | 310 + F/400 | (f - 310) * 400 | (beim RFM12B nicht vorhanden) |

| 433 | 43 | 430,24 | 439,7575 | 434,16 | 430 + F/400 | (f - 430) * 400 | 433,05 .. 434,79 (Europa, BW = 1,74) | ||

| 868 | 2 | 860,48 | 879,515 | 5 | 868,32 | 860 + F/200 | (f - 860) * 200 | 868 .. 870 (kein ISM! BW = 2) | |

| 915 | 3 | 30 | 900,72 | 929,2725 | 7,5 | 912,48 | 900 + 3*F/400 | (f - 900) * 133,3 | 902 .. 928 (Amerika, BW = 26) |

Gesendet wird mit einem (weiter unten) einstellbaren Frequenzhub. Empfangen wird mit der hiermit einstellbaren Mittenfrequenz, zuzüglich einem AFC-Offset.

Bitrate (Data Rate C6xx)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | cs | r6 | r5 | r4 | r3 | r2 | r1 | r0 | 0xC623 |

| cs | clock select | Vorteiler mit Faktor 8 aktivieren für Bitraten kleiner 2694 s-1. | 0 : Basistakt = 10 MHz / 29 |

|---|---|---|---|

| 1 : Basistakt = 10 MHz / 29 / 8 | |||

| r | rate | Bitratenteilerfaktor | 0000010 = Maximum (2) ≈ 115200 s-1 (cs=0) |

| xxxxxxx : Baudrate = Basistakt / (r+1) | |||

| 0100011 = Vorgabe (35) ≈ 9600 s-1 (cs=0) | |||

| 1111111 = Minimum (127) ≈ 336 s-1 (cs=1) |

Die theoretisch maximale Bitrate von 250 kBit/s muss zu Fuß ohne FIFO-Beteiligung sowohl generiert als auch eingelesen werden. Dafür benutzt man am ehesten eine im Mikrocontroller eingebaute RS-232-Schnittstelle und verzichtet auf die elegante Taktrekonstruktion, nimmt einfach das Startbit. Einige wenige Mikrocontroller enthalten eine Serialisierungseinheit für magnetische Speichermedien, Infrarot- oder Funkstrecken, die dafür bestens geeignet ist.

Die Anzahl der notwendigen Bitwechsel (1-0 oder 0-1) im Datenstrom bzw. deren Ausbleiben ist davon abhängig, wie sehr sich die Baudraten auf Sender- und Empfängerseite unterscheiden und ob eine langsame oder schnelle Taktsynchronisierung eingestellt wurde. Wenn sich zwei RFM12-Module gegenüber stehen, ist die Taktregenerierung kaum ein Problem; laut Datenblatt dürften bei einer Quarzabweichung von 10-5 430 Bytes ohne Bitwechsel korrekt erfasst werden

Die hier eingestellte Bitrate wirkt sowohl auf den Sender als auch den Empfänger, hat aber keinen Einfluss auf bestimmte, davon abhängige Parameter wie Frequenzhub, Sender- und Empfängerbandbreite. Dies muss nach folgender Empfehlung eingestellt werden:

| Bitrate in kBit/s | 1,2 | 2,4 | 4,8 | 9,6 | 19,2 | 38,4 | 57,6 | 115,2 | 250 |

|---|---|---|---|---|---|---|---|---|---|

| Basisband-Empfängerbandbreite in kHz | 67 | 134 | 200 | 400 | |||||

| Frequenzhub in kHz (±) | 45 | 90 | 120 | 240 | |||||

| PLL-Bandbreite (bw0) | 0 | 1 | |||||||

Kurios: Die maximale Bitrate beim Senden mittels Senderegister beträgt 172 kBit/s; hier darf der Teilerwert r = 1 sein. Empfangen kann man damit nicht, jedenfalls nicht mit der FIFO.

Empfängersteuerung (Receiver Control 9xxx 9000 .. 97FF)

Bestimmt Eigenschaften des Empfänger-Traktes, insbesondere die Bandbreite des Tiefpasses.

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 1 | 0 | 0 | 1 | 0 | pi | d1 | d0 | i2 | i1 | i0 | g1 | g0 | r2 | r1 | r0 | 0x9080 | |

| pi | pin int/vdi | Bestimmt die Funktion des Pins INT / VDI ⑪ Typischerweise einschalten. Als INT dient es zum Kaskadieren einer weiteren Interruptquelle (die am Mikrocontroller durch IRQ ② verloren geht). |

0 = INT, Interrupt-Eingang |

|---|---|---|---|

| 1 = VDI, Daten-Gültig-Ausgang | |||

| d | valid data indicator response | Definiert die Geschwindigkeit, mit der bestimmt wird, ob ein Empfangssignal korrekt ist oder nicht. Je nach eingestellter Variante werden unterschiedliche Verknüpfungen benutzt. Siehe Schaltbild unten. | 00 = schnell |

| 01 = mittel | |||

| 10 = langsam | |||

| 11 = immer an | |||

| i | i/q demodulator bandwidth | Bestimmt die Bandbreite des Empfängers (einstellbarer Tiefpass). Da sollte der Frequenzhub und die Nutzsignalbandbreite hineinpassen. Siehe Vorbetrachtungen. | 000 = reserviert |

| 001 = 400 kHz | |||

| 010 = 340 kHz | |||

| 011 = 270 kHz | |||

| 100 = 200 kHz | |||

| 101 =134 kHz | |||

| 110 = 67 kHz | |||

| 111 = reserviert | |||

| g | lna gain select | Verstärkungsfaktor des UHF-Verstärkers am Eingang (LNA = Low Noise Amplifier, als ob das nicht selbstverständlich ist). Werte in dBm (Dezibel [Größe: Milliwatt]). Da negativ handelt es sich effektiv um Dämpfungen bezüglich der Maximalverstärkung. | 00 = 0 dB |

| 01 = -6 dB | |||

| 10 = -14 dB | |||

| 11 = -20 dB | |||

| r | rssi detector threshold | Relative Empfangsfeldstärke, bei der das digitale Feldstärkesignal dRSSI aktiv wird, in 6-dB-Schritten. Die Dämpfung des UHF-Verstärkers geht in die tatsächliche Berechnung noch ein. Die Vorgabe ist maximal empfindlich, bereits 6 dB weniger brachte versuchsweise eine sinnvolle Funktion. Die Schaltschwelle ergibt sich aus Subtraktion der (negativen) UHF-Verstärker-Verstärkung von der Schaltschwelle. Das Plus im Datenblatt ist falsch. |

000 = -103 dB |

| 001 = -97 dB | |||

| 010 = -91 dB | |||

| 011 = -85 dB | |||

| 100 = -79 dB | |||

| 101 = -73 dB | |||

| 11x = reserviert |

Synchronmuster (Synchron Pattern 0xCExx, nur RFM12B)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | 0xCED4 |

| b | byte | Legt den Wert fest, der als Synchronisations-Byte für die Datenfilterung verwendet werden soll. |

|---|

Empfangsdatenrekonstruktion (Data Filter C2xx)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | al | ml | 1 | s | 1 | q2 | q1 | q0 | 0xC22C |

Die beiden 1-Bits sind unbekannt. (Auch im Datenblatt von IA4420 so beschrieben.)

| al | auto lock | Bittakt-Rekonstruktion schaltet automatisch vom schnellen in den langsamen Modus, sobald ein Takt erkannt wurde | 0 = aus, siehe ml |

|---|---|---|---|

| 1 = ein, ml unwirksam | |||

| ml | manual lock | schneller/langsamer Modus der Bittakt-Rekonstruktion | 0 = langsam (für 12 bis 16 Bit Takteinlauf) |

| 1 = schnell (für 4 bis 8 Bit Takteinlauf) | |||

| s | select filter | Typ des Datenfilters auswählen. Bei Analogfilter kann weder die FIFO noch die Taktrekonstruktion genutzt werden! |

0 = Digitalfilter |

| 1 = Analogfilter | |||

| q | quality | Bestimmt den Schwellwert, ab dem ein Signal als gut befunden wird und der Empfänger dieses weiterverarbeiten soll. DQD (data quality detection) zählt die „Spikes“ des ungefilterten Signals und bestimmt darüber die Qualität der Daten. | 000 = DQD immmer EIN (?) |

| 100 = mittlere Schwelle | |||

| 111 = Maximum (7) |

Die maximale Bitrate für die Verwendung des Digitalfilters (und damit der FIFO und Taktrekonstruktion) beträgt 115 kBit/s. Das Digitalfilter ist eine digitale Implementation eines RC-Filters, gefolgt von einem hysteresebehafteten Komparator. Dessen Zeitkonstante wird automatisch an die programmierte Bitrate angepasst.

Die maximale Bitrate für die Verwendung des Analogfilters beträgt 250 kBit/s. Zu seiner Nutzung ist ein Kondensator an CFIL ④ zu beschalten. Der intern wirksame Widerstand hat 10 kΩ.

| Datenrate in kBit/s | 1,2 | 2,4 | 4,8 | 9,6 | 19,2 | 38,4 | 57,6 | 115,2 | 256 |

|---|---|---|---|---|---|---|---|---|---|

| Filterkapazität | 12 nF | 8,2 nF | 6,8 nF | 3,3 nF | 1,5 nF | 680 pF | 270 pF | 150 pF | 100 pF |

Der „Datenqualitätsmesser“ (Data Quality Detector) ist eine digitale Signalverarbeitungsstufe, die das Demodulatorsignal abgreift. Er wird automatisch aktiviert, sobald der Empfänger läuft, und stellt den Empfang eines FSK-Signals fest. Der einstellbare Schwellwert entscheidet, wie sauber das Empfangssignal sein muss, damit es als gültiges Signal erkannt wird. Wenn der intern berechnete DQD-Wert für mindestens 5 HIGH-Bits und mindestens 5 LOW-Bits größer als der Schwellwert ist, dann ist das resultierende Ausgangssignal HIGH. Der Schwellwert q sollte nach folgender Vorschrift gewählt werden:

- 4 × (Frequenzhub - Frequenzdifferenz[TX-RX]) / Bitrate

- ≥ 4, sonst wird möglicherweise Rauschen als FSK erkannt

- Maximal 7

- Man kann getrost kleinere Werte verwenden, wenn DQD nicht wichtig ist.

FIFO-Steuerung (FIFO and RESET Mode CAxx)

Legt Eigenschaften der Empfänger-FIFO fest

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | f3 | f2 | f1 | f0 | sp | al | ff | dr | 0xCA80 |

| f | fifo interrupt level | Legt den Füllstand fest, bei dem die FIFO einen Interrupt auslöst. Die Vorgabe von 8 bit ist am sinnvollsten, weil passend zum Sende-Latch, welches fest 8 bit breit ist. |

0000 = verboten |

|---|---|---|---|

| 0001 = 1 (Interrupt bei jedem Bit) | |||

| 1000 = 8 (Interrupt bei vollem Byte) | |||

| 1111 = 15 (Interrupt bei 15 Bit) | |||

| sp | sync pattern length | Legt die Länge des Synchronmusters fest, nur RFM12B | 0 = 2 Byte, typ. 0x2DD4 |

| 1 = 1 Byte, typ. 0xD4 | |||

| al | always fill | Legt fest, ab wann das Füllen der FIFO beginnt | 0 = Nach erkanntem Synchronmuster |

| 1 = sofort alles | |||

| ff | fifo fill | Freigabe der FIFO zum Beschreiben durch den Empfänger, oder Leeren der FIFO Die FIFO wird zusätzlich von er gesteuert. |

0 = FIFO leeren und sperren |

| 1 = FIFO freigeben | |||

| dr | disable sens-reset | Abschalten des hochsensitiven Power-On-Resets. Normalerweise wird bei einer Speisespannung unter 1,6 V oder einem Anstieg von 0,6 V ein Reset ausgelöst |

0 = Resetschaltung aktiv |

| 1 = Resetschaltung AUS |

Zum Neustart der Synchronmustererkennung bei durchlaufendem Empfänger (er = 1) sollte ff auf 0 und danach wieder auf 1 gesetzt werden.

Bei der Synchronmustererkennung darf kein Bitfehler auftauchen, d.h. es wird eine Hammingdistanz von 0 erwartet.

Automatische Frequenznachregelung (Automatic Frequency Control, AFC C4xx)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | a1 | a0 | rl1 | rl0 | st | fi | oe | en | 0xC4F7 |

Die AFC ist unbrauchbar!

Entweder abschalten (und manuell Axxx oder 80xx x korrigieren) oder per Software die Korrektur des Frequenzregisters Axxx über das Auslesen des Offset-Registers OFFS im Modus a = 11 bei Empfang eines Senders (VDI = 1) vornehmen - Details im Anhang.

| a | auto mode | Modus der AFC-Schaltung

AFC-Fangbereich: 0,8·δf (Frequenzhub: δf=(fmax-fmin)/2) |

00 = kein automatischer Betrieb |

|---|---|---|---|

| 01 = einmalig nach POR (Power-on reset) | |||

| 10 = solange VDI high ist (keine Funktion - siehe Anhang) | |||

| 11 = unabhängig von VDI (unbrauchbar - siehe Anhang) | |||

| r | range limit | Korrekturwertbegrenzung (AFC arbeitet immer im Bereich -64∆f .. +63∆f - siehe Anhang) ∆f beträgt: |

00 = unbegrenzt: -64∆f .. +63∆f |

| 01 = -16∆f .. +15∆f | |||

| 10 = -8∆f .. +7∆f | |||

| 11 = -4∆f .. +3∆f | |||

| st | strobe edge | Eine steigende Flanke (0->1) übernimmt den berechneten Wert ins Offset-Register | |

| fi | fine mode | Genauer Berechnungsmodus (besser aber lansgamer) | 0 = normal |

| 1 = präziser | |||

| oe | offset enable | AFC-Offset freischalten (zum PLL-Synthesizer durchschalten)

(Sicherlich nur sofern der Empfänger läuft, also er aktiv ist!) |

0 = aus, AFC unwirksam |

| 1 = ein, AFC wirksam | |||

| en | enable afc | AFC-Berechnung aktivieren | 0 = aus |

| 1 = ein | |||

Warum ist die AFC unbrauchbar:

Die AFC arbeitet immer im Bereich -64∆f .. +63∆f, die Begrenzung r für das Offset-Register erfolgt mittels digitaler Begrenzung.

Dadurch kann es schnell passieren, dass die AFC vom eigentlichen Signal wegdriftet und das ursprüngliche Signal nicht mehr im Fangbereich (0,8·Frequenzhub) liegt und somit nichts mehr empfangen wird.

Aus diesem Grund ist die Einstellung AFC immer an (a = 11) wohl völlig unbrauchbar.

Siehe dazu Diagramm S.23 des Datenblatts.

Die Einstellung mit VDI a = 10 scheint (zumindest bei den RFM12B - RFM12S Rev 4.0) nicht zu funktionieren, da egal welchen Status VDI hat, das Offset-Register immer den Wert 0 hat. Auch ein manuelles Übernehmen der Offsetwerte mittels steigender Flanke an strobe st = 0->1 liefert immer Offset 0. Siehe dazu auch den Forumbeitrag RFM12 - AFC mit VDI ohne Funktion?

Der Fangbereich der AFC ist relativ klein und eignet sich meist nur für geringfügige Frequenzkorrekturen (Abhängig vom Frequenzhub des Signals). Bei größeren Frequenzabweichungen (Toleranzen der Quarze), kann es deshalb notwendig sein, einen Frequenzscan (über Axxx oder 80xx x) zum Finden der Senderfrequenz durchzuführen (manuell oder per Software). Das Ergebnis sollte dann gespeichert und nach einem Neustart zurückgeschrieben werden (EEPROM des µCs). Damit ist eine Grundabstimmung gewährleistet, auf eine AFC kann dann möglicherweise verzichtet werden.

Zum Auslesen des AFC-Offset-Werts ist folgendes zu beachten:

Eine AFC-Berechnung ist beendet, wenn sich im Statusregister ATGL ändert.

Das Statusregister gibt nur sinnvolle Werte für OFFS aus, wenn vorher die AFC abgeschaltet wird (en = 0), da der Teil des Statusregisters bei der Ausgabe nicht zwischengespeichert wird, sondern einfach raustaktet. Dabei könnte es während des Abrufs zu einer Änderung der Offset-Werte kommen und das Ergebnis wäre falsch.

Siehe dazu Diagramm und Anmerkung S.28 des Datenblatts.

Das funktioniert nur vernünftig, wenn das Register regelmäßig gepollt wird (der Interruptbetrieb macht dann im Rx-Modus keinen Sinn mehr)

Der Vollständigkeit halber die Erklärungen aus dem Datenblatt:

Der Automatik-Modus a = 10 sollte bevorzugt verwendet werden, wenn mehrere RFM12-Transceiver angesprochen werden sollen, etwa in einem Peer-to-Peer-Netzwerk oder als Zentralknoten in einem sternförmigen Netzwerk. Der Modus a = 11 ist zu bevorzugen, wenn nur eine Gegenstelle angesprochen wird, also bei nur 2 Teilnehmern oder Endpunkte in einem sternförmigen Netzwerk.

Senderkonfiguration (TX Configuration 9800 oder 9900)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 0 | 0 | 1 | 1 | 0 | 0 | mp | m3 | m2 | m1 | m0 | 0 | p2 | p1 | p0 | 0x9800 |

| mp | modulation polarity | Bestimmt die Richtung der FSK-Erzeugung (entspricht Signalinvertierung). | 0 = normal (1-Bit = höhere Frequenz) |

|---|---|---|---|

| 1 = invertiert (0-Bit = höhere Frequenz) | |||

| m | frequency deviation | Legt den Frequenzhub fest, die Frequenzablage von der eingestellten Mittenfrequenz, in 15-kHz-Schritten. Dieser ist als ±-Wert zu sehen. Zum Vergleich: Der (maximale) Frequenzhub beim UKW-Rundfunk beträgt ± 75 kHz. |

0000 = ± 15 kHz, Minimum |

| xxxx = (m+1) * 15 kHz | |||

| 1111 = ± 240 kHz, Maximum | |||

| p | relative output power | Bestimmt die relative Ausgangsleistung des Senders relativ zu seiner Maximalleistung. (Dezibel [Größe: Milliwatt]) RFM12: 3-dBm-Schritte. RFM12B: 2,5-dB-Schritte. Der Wert steht im Zusammenhang mit der angeschlossenen Antennen-Impedanz. | 000 = 0 dB, Maximum |

| xxx = -3 * p bzw. -2,5 * p | |||

| 111 = -21dB bzw. -17,5dB, Minimum |

Zeitgeber für Wake-Up (Wake-Up Timer Exxx .. Fxxx)

Bestimmt die Zeitperiode der zyklischen Einschaltung des WakeUp-Timers. Nach Ablauf der Zeitperiode erfolgt ein WKUP-Interrupt, der zum Aufwecken eines Mikrocontrollers verwendet werden kann.

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 1 | 1 | r4 | r3 | r2 | r1 | r0 | m7 | m6 | m5 | m4 | m3 | m2 | m1 | m0 | 0xE196 |

Das Bit ew muss aktiv sein, damit der Zeitgeber funktioniert

| r | radix | Exponent zur Basis 2. Erlaubt: 0 .. 29 |

|---|---|---|

| m | mantissa | Mantisse. Erlaubt: 1..255. Die Schlafzeit Twake-up = m * 2r ms |

- Minimale Schlafzeit: 1 ms

- Vorgabe: 150 * 21 ms = 300 ms

- Maximale Schlafzeit: ≈ 2 Jahre

Bei Wake-Up-Interrupt ist ew nach jedem Zyklus zu löschen und wieder zu setzen. Vor der ersten Benutzung sollte einmal ein „Dummy-Lauf“ mit einer kurzen Zeitperiode absolviert werden, d.h. der Interrupt sollte einmal ausgelöst werden. Danach kann die gewünschte Wake-Up-Zeit eingestellt werden. Ohne den „Dummy-Lauf“ kann es zu unverständlichen Interrupts kommen. Der Zeitgeber rekalibriert sich bei jedem Hochlauf am Quarzoszillator und benötigt dafür 0,5 ms (nach der Quarz-Hochlaufzeit von bis zu 7 ms).

Im Datenblatt zum RFM12B ist ein zuzurechnender Faktor von 1,03 angegeben, der aber in der gleichsam angegebenen Genauigkeit von 10 % untergeht. Ist also Quatsch, selbst wenn man der beim RFM12 angegebenen 5 % glaubt.

Software-Reset (0xFE00)

Das Kommando 0xFE00 löst einen Software-Reset aus. Die Wirkung ist vermutlich wie bei Power-On-Reset (also Interrupt aktiv). Der Befehl ist im Datenblatt für den RFM12 nicht beschrieben, scheint aber wie beim RFM12B zu wirken.

Der Befehl funktioniert nur im high-sensitive reset mode. Nach dem Befehl muss wie beim POR eine Wartezeit von 100ms eingehalten werden.

Automatisch zyklischer Empfänger (Low Duty-Cycle C8xx)

Neben der Möglichkeit des zyklischen Aufweckens eines angeschlossenen Mikrocontrollers besteht beim RFM12 auch die Möglichkeit, den Empfänger kurzzeitig zu aktivieren ohne den Controller zu wecken, und den Mikrocontroller erst bei gültigem Signal (etwa vom Ausgang VDI ⑪ oder bei Synchronmusterempfang) zu wecken. Somit kann der Empfänger autonom eine feste Frequenz bei geringem Stromverbrauch überwachen.

Mit dem Wake-Up-Timer wird die Periodendauer (mithin die Einschaltfrequenz) des Empfängers eingestellt (bspw. alle 500 ms), und mit dem hier einstellbaren Wert wird bestimmt, wie lange der Empfänger dann aktiv sein soll (bspw. 30 % von 500 ms = 150 ms. Werden während der Einschaltdauer gültige Daten empfangen, bleibt der Empfänger bis zum Ende von DQD aktiv. Wird dabei schließlich ein Synchronmuster erkannt und die FIFO gefüllt, gibt es einen FIFO-Interrupt.

Der WakeUp Timer muß zur Nutzung des Low Duty Cycles weder aktiviert sein, noch muss er in jedem Zyklus zurückgesetzt werden.

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | d6 | d5 | d4 | d3 | d2 | d1 | d0 | en | 0xC80E |

| d | duration | Einschaltdauer während der zyklischen Einschaltung Einschaltverhältnis = (d*2+1)/m Einschaltdauer = (d*2+1) * 2r ms |

0000000 = 2r ms, Minimum |

|---|---|---|---|

| 0000111 = 2r × 15 ms = 30 ms (r = 1) | |||

| 1111111 = Quatsch, Einschaltdauer ≥ Zykluszeit | |||

| en | enable | Zyklische Einschaltung aktivieren | 0 = aus |

| 1 = ein |

Normalerweise muss die Sendeseite ein permanentes oder eng gelücktes Signal über die gesamte Periodendauer ausstrahlen, damit der Empfänger davon Notiz nehmen kann. Um sowohl beim Sender als auch beim Empfänger Strom sparen zu können, ist es hilfreich, wenn die Wachzeiten der Gegenseite in etwa bekannt sind. Dazu sind hinreichend genau gehende Wake-Up-Zeitgeber erforderlich. Dies wird beim RFM12 bewerkstelligt, indem der Timer beim Einschalten an der Quarzfrequenz abgeglichen wird, um Streuungen zu minimieren.

Ein deutlich exakteres Arbeiten ist möglich, wenn auch aufwändiger, wenn man auf den Zeitgeber des RFM12 verzichtet und statt dessen eine 32-kHz-basierte Uhrenquarzzeitbasis des Mikrocontrollers verwendet, typischerweise am asynchronen Oszillator am Timer2 eines ATmega-Controllers.

Empfänger-FIFO lesen (RX FIFO Read B000)

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0xB000 |

Dieses Kommando löst die Rückgabe eines Datenbytes (synchron mit dem 8. Bit) aus. Es ist nötig, dass das ef-Bit (RX-FIFO) im Configuration Setting gesetzt wurde, um diese Funktion nutzen zu können!

___ _ __

SEL \________________________________________________________________________________/ \___|?|__________________

_ _ _ _ _ _ _ _ __ __ __ __ __ __ __ __ _ _ _ _

SCK ___/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \__/ \__/ \__/ \__/ \__/ \__/ \__/ \__/ \_______|?|__/ \_/ \_/ \_/ \_

_____ _______ ggf. reduzierte Schiebetaktfrequenz _______ ____ _______

SDI _/ \___/ 0xB0 \_______________________________________________________________/_______|?|/ \___/ 0xB0 \_

________________________________ _____ _____ _____ _____ _____ _____ _____ _____ _ ____________________

SDO -________________________________X_____X_____X_____X_____X_____X_____X_____X_____X_---___/↑

FFIT (sollte HIGH sein) D7 D6 D5 D4 D3 D2 D1 D0 D? └─Interrupt

D? = FIFO ist vom Fall-Through-Typ; ungültig oder nächstes Datenbit wenn nicht leer

|?| = warten bis SDO = HIGH (nicht auf die L-H-Flanke, diese könnte ausbleiben!)

--- = Tristate, der Bus-Holder hält den Ausgang auf den letzten Pegel fest

Bei entsprechender Füllstands-Einstellung kann man hiermit auch mehr (bspw. 9 Bit) oder weniger (bspw. 7 Bit oder auch jedes Bit einzeln) abholen. Da das Senderegister auf 8 Bit festgelegt ist, hat das meistens keinen Sinn.

Die Taktfrequenz darf für das FIFO-Auslesen maximal 2,5 MHz betragen.

Alternativ kann das Auslesen der FIFO ohne den 0xB0-Präfix mittels FFS ③ erfolgen. Das Bit er muss dazu eingeschaltet sein, ansonsten beschreibt man damit das Sende-Register. Um festzustellen, ob ein Byte verfügbar ist, ist im Datenblatt die Auswertung von FFIT ④ angegeben. Mit einiger Sicherheit genügt auch der LOW-Pegel an IRQ ②. Hat man nur SDO ① zur Verfügung, muss man FFS zwischendurch deaktivieren und SEL ⑭ aktivieren. Was bei gleichzeitiger Aktivierung der beiden Chip-Select-Signale passiert ist undokumentiert.

Senderegister schreiben (TX Register Write B8xx)

Dieses Kommando schreibt Daten in den TX-Puffer. Wenn der Sender aktiv ist, wird dieses gesendet, sobald das andere Register leer ist.

el muss eingeschaltet sein.

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| ← | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | t7 | t6 | t5 | t4 | t3 | t2 | t1 | t0 | 0xB8AA |

| t | transmit | Das Datenbyte, welches gesendet werden soll. |

|---|

(Senden Funktioniert nur wenn zuvor der Status abgefragt wurde - Nö!)

___ _ _

SEL \_________________________________________________________________|?|_________________________________|?|________________________________/

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

SCK __/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \__/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_|?|_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_|?|_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \__

__ ___________ ___ ___ ___ ___ ___ ___ ___ _____ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___ ___

SDI _/ \___/ = B 8 \____________/___X___X___X___X___X___X___X_____|?|X___X___X___X___X___X___X___X___X|?|X___X___X___X___X___X___X___X___\_

__________________________________________ ___________ ___________

SDO - = RGIT \\\\\____________________/ \\\\\___________________/ \\\\\__________________-

|?| = warten bis SDO ① wieder HIGH wird, bspw. per Interrupt

Datenbytes können, bei aktiv LOW gehaltenem SEL ⑭, bei HIGH an SDO ① nachgeschoben werden, ohne das Präfixbyte 0xB8 wiederholen zu müssen.

Alternativ kann das Einschreiben der Daten mittels FFS ③ erfolgen.

Die beiden Senderegister werden beim Power-On-Reset und beim Ausschalten von et mit 0xAA vorbelegt und eins davon (?) als leer markiert.

Solange der Sender ausgeschaltet ist, kann man durch Einschreiben zweier anderer Bytes eine andere Präambel (Takteinlauf) beim Einschalten des Senders erzwingen.

Um das Aussenden des passenden Synchronmusters (typ. 0x2DD4) für den Empfänger muss man sich selbst kümmern! Der typische Sendeverlauf ist daher:

- Senden von mehr oder weniger Takteinlauf-Bytes (viele Flankenwechsel, möglichst gleich viele 0-Bits und 1-Bits, etwa

0xAA, 0x55, 0xCCusw. - Senden des Synchronmusters

- Senden der Daten, typischerweise:

- Längenangabe voraus (da der Empfänger keine sichere Endeerkennung hat)

- eigentliche Nutzdaten, ggf. hamming-kodiert gegen einzelne Bitfehler

- Fehlersicherung (CRC)

Um den korrekten Moment zum Ausschalten des Senders zu finden, ist es am günstigsten, am Ende ein Dummy-Byte (typischerweise 0xAA) einzuschreiben und danach auf ein erneutes HIGH von SDO ① zu warten. In diesem Moment beginnt der Sender mit dem ersten Bit des Dummy-Bytes, und man kann et sicher und zeitnah auf Null setzen.

Status lesen (Status Read 0000)

Dieses Kommando löst die Rückgabe des Statusregisters aus. Im wesentlichen werden damit Interruptanforderungen gelöscht. Das Null-Bit im MSB entscheidet hierbei, dass Statusbits geliefert werden. (Vermutlich sind die anderen Sende-Bits don't care, also egal.) Wie auch sonst erscheint das erste Bit ganz ohne Takt SCK ⑬ nach der fallenden Flanke von SEL ⑭.

| Byte | MSB | LSB | Vorgabe | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Ausgabe-Bits (er≡1) Ausgabe-Bits (er≡0) |

FFIT RGIT |

POR | FFOV RGUR |

WKUP | EXT | LBD | FFEM | RSSI ATS |

DQD | CRL | ATGL | OFFS6 | OFFS3 | OFFS2 | OFFS1 | OFFS0 | 0x4000 |

Wie weiter oben betrachtet kann man mit weiteren Takten die Empfangs-FIFO auslesen.

| er=1 | er=0 | Unterbrechungsanforderungen (Interrupts), 6 Bits | verschwindet durch … | ||

|---|---|---|---|---|---|

| 15 | RGIT | register interrupt | Senderegister ist bereit für neue Sendedaten |

| |

| FFIT | fifo interrupt | Die Anzahl der Datenbits im FIFO-Puffer hat das eingestellte Limit (Standard: 8 Bits) erreicht |

| ||

| 14 | POR | power-on reset | Power-On-Reset: Alle Register wurden mit Vorgabewerten geladen / überschrieben |

| |

| 13 | RGUR | register underrun | Der Datenstrom ist beim Senden abgerissen, da nicht schnell genug Daten nachgeladen wurden. Es wurden und werden abwechselnd die letzten beiden Bytes gesendet.

Oder aber es wurde in ein volles Senderegister geschrieben. |

| |

| FFOV | fifo overflow | Die Empfangs-FIFO ist übergelaufen, weil Daten nicht zügig genug abgeholt wurden. Die FIFO ist blockiert bis zum nächsten Synchronwort |

| ||

| 12 | WKUP | wakeup | Der Aufweck-Timer ist abgelaufen |

| |

| 11 | EXT | external interrupt | Es liegt Low-Pegel am Eingang INT ⑪ vor |

| |

| 10 | LBD | low battery detected | Es liegt Unterspannung vor |

| |

| Statusangaben, 10 Bits | |||||

| 9 | FFEM | fifo empty | Der FIFO-Puffer ist leer | ||

| 8 | RSSI | received signal strength | Die Signalstärke ist über dem eingestellten Limit | ||

| ATS | antenna tuning: strong | Das Antennenabstimmschaltung hat ein starkes Radiosignal detektiert (Was auch immer das bedeutet. Könnte auch perfekte Antennen-Fehlanpassung beim Senden sein.) | |||

| 7 | DQD | data quality detector | Der Ausgang des Datenqualitätsbewerters | ||

| 6 | CRL | clock recovery locked | Die Taktwiederherstellung ist eingerastet | ||

| 5 | ATGL | afc toggle | Kippt mit jedem AFC-Zyklus, d.h. nachfolgende Bits ändern sich (gemessen wurden etwa 4 kHz, s.u.) | ||

| 4 | OFFS6 | sign of offset | MSB = Vorzeichen des AFC-Offsets | ||

| 3:0 | OFFS3:0 | offset | Letzte 4 Bits vom AFC-Offset. Bei entsprechend begrenzter AFC (Vorgabe) entspricht dies dem tatsächlichen AFC-Offset. Ansonsten muss man den AFC-Abstimmvorgang durch zyklisches Auslesen des Statusregisters beobachten und die fehlenden Bits extrapolieren. | ||

Einen Interrupt bei FIFO-Unterlauf (Auslesen von zu vielen Bits) scheint es nicht zu geben.

Beachte: Solange irgendein Interrupt aktiv ist sowie der Taktausgang aktiv ist (dc=0), kann der RFM12 nicht in den Schlafmodus wechseln, und der Quarzoszillator läuft durch. Grundsätzlich sollte bei jedem Interrupt eine Statusabfrage (über die Interruptquelle) erfolgen und danach die Ursache getilgt werden. Bei Verwendung eines flankengetriggerten Interrupt-Eingangs (etwa Pin-Change) läuft man Gefahr, nicht alle Interrupts zu bedienen! Hier sollte pegelgetriggerter Interrupt simuliert werden, indem der Kode in einer Schleife so lange ausgeführt wird, bis der Eingang inaktiv (HIGH) ist.

Die AFC-Werte sind nur glaubhaft, wenn nicht gerade eine automatische AFC läuft. (Da fehlt wohl ein Puffer.) Um hiermit korrekte AFC-Werte zu lesen, sollte die AFC-Berechnung vor dem Status-Lesen ausgeschaltet werden (Bit en = 0).

Mit vagabundierender Spannung bei deaktiviertem Pull-Up-Widerstand an SDO ① braucht man nicht rechnen, da (laut Datenblatt) dieser Ausgang mit Bus-Hold ausgestattet ist. So bezeichnet man eine hochohmige Rückführung eines nichtinvertierenden Eingangstreibers, die den Eingang im zuletzt vorgefundenen Spannungspegel hält (tatsächlich ein Flipflop-Effekt).

Einstellungen für maximale Reichweite

Für eine maximale Reichweite eignen sich folgende Einstellungen:

- Bitrate: 2k - 10kbit/s.

- Receiver Baseband Bandwidth: 134kHz

- RSSI Threshold: -97dBm

- LNA gain: 0dB. Falls in der Gegend Störer im gleichen Frequenzbereich sind, dann -6dB, ansonsten kann die Eingangsstufe übersteuern.

- FSK frequency deviation: +/-90kHz

- Output Power: 0dB

Und vor allem: Eine gute (Richt-) Antenne.

Quarzfrequenz ändern

Im Datenblatt wird die Verwendung eines 10 MHz-Quarzes empfohlen. Man darf die Frequenz aber nach oben und unten variieren, wie Messungen mit einem DDS-Generators anstelle des Quarzes zeigen: PLL-Einrast-Tabelle. Eine Tabelle: Quarzfrequenzen von 8,5-11 MHz zeigt die damit erreichbaren Frequenzen. Quarze für 3. oder auch 5.Oberton sollten auch auf ihrer Grundfrequenz verwendbar sein, dafür bieten sich u.a. CB-Funk- und 10m-Amateurbandquarze an.

Den Einfluß der vier unteren Bits im Configuration Setting Register und des mp-Bits (Modulations-Polarität?) auf die PLL-Frequenz zeigt diese Kapazitäts-Tabelle. Pro Stufe sind es hier etwa 4 kHz, das kann je nach Quarz schwanken. Möglicherweise ist so auch Schmalband-FSK möglich, ohne Änderung des PLL-Teilers.

Was können wir damit anfangen? Neben dem regulären Einsatz auf den beiden zugelassenen Bändern 433 und 868 MHz sind das unter anderem (bitte weitere Ideen einfügen):

- Packet-Radio mit 9600 Baud im 70cm-Amateurband 430-440 MHz. Die einfachste Möglichkeit ist das Programm Soundmodem, das für Windows und Linux existiert. Wer es komfortabler haben will findet hier eine Beschreibung wie Soundmodem mit den Programmen Flexnet und Paxon zusammenarbeitet. Eine Karte der Packet-Radio-Digipeater im 70cm-Band kann man mittels Hammap erstellen. Leider werden die Daten in den letzten Jahren nicht mehr sehr gepflegt, es dürften einige Karteileichen enthalten sein.

- Empfang der POCSAG-Funkrufsender am oberen Ende des Amateurbandes auf 439,9875 MHz 2-FSK mit 4kHz Hub und 1200 bit/s im POCSAG Radio Paging Code 1 (Liste der Sender, Stand 18.09.07). Zur Decodierung existieren mehrere Programme, aufbauend auf Multimon die Weiterentwicklungen Monitor und MonitorD. Im Prinzip könnte man damit auch die verschlüsselten Wettermeldungen auf 466,23 MHz mitschreiben, aber nicht decodieren.

- Empfang der D-Star-Relais. Das ist eine patentierte digitale Sprach- und Datenübertragung, deren Eigentümer dafür sorgt, dass kein käufliches oder Selbstbaufunkgerät ohne den "AMBE"-Modemchip D-Star senden und empfangen darf. Es gibt eine kleine Ausnahme, das Programm r00t's D-Star Decoder V0.2a für die Soundkarte, das nur Rufzeichen und Datentelegramme der beteiligten Funkamateure darstellt.

- Panoramaempfänger (die Bezeichnung Spektrumanalysator wäre etwas übertrieben) unter Verwendung des analogen RSSI Ausgangs (Anschluß am Kondensator in der Ecke). Damit ließe sich z. B. auch die Bandbelegung im PMR-Bereich 446,0-446,2 MHz oder im Mobilfunkband um 900 MHz anzeigen.

- Pegelanzeige für Mobilfunksender. Im 900 MHz Mobilfunkbereich könnte man mit dem RSSI-Ausgang die umliegenden Funkmasten anpeilen und ihre Pegel anzeigen. Laut Datenblatt nur ein Anzeigeumfang von 35 dB, aber mit umschaltbarem Grundpegel.

- In Verbindung mit einem Frequenzumsetzer lassen sich weitere Frequenzbereiche erschließen, z. B. Packet-Radio im 23cm- (1240-1200 MHz) und 13cm- (2320-2450 MHz) Amateurband. Leider liegt die Zwischenfrequenz der Satellitentuner (479,5 MHz) schon am oberen Ende des PLL-VCO-Einrastbereiches. Damit wäre ein preiswerter Konverter für 23cm möglich, meistens schon mit I2C-Bus PLL.

- Local Oscillator für einen Empfänger. Mit den ca. 5 Milliwatt des RFM12 läßt sich ein passiver Diodenringmischer ansteuern. Damit kann man einen Überlagerungsempfänger oder -sender mit hoher erster Zwischenfrequenz bauen.

- Umsetzer für DVB-T Amateurfunkrelais Manche ATV-Relais haben eine digitale Ausgabe im 23cm-Band, beispielsweise DB0FT auf dem großen Feldberg im Taunus mit 1285 MHz. Übliche DVB-T-Empfänger sind aber auf die terrestrischen TV-Bänder 47-862 MHz beschränkt. Ein Umsetzer mit einer LO-Frequenz von 850 MHz, z.B. ein RFM02 mit 9,8 MHz-Quarz setzt auf 435 MHz um.

Antennen-Anpaßnetzwerk

Soll das RFM12 auf anderen Frequenzen betrieben werden, ist nur eine Änderung des Antennennetzwerks nötig. Das Datenblatt bietet knappe aber ausreichende Informationen.

Zwischen Pin 12 und 13 liegt eine Spannungsquelle, die ihre maximale Sendeleistung in eine komplexe Last nach der Tabelle "Note4" abgibt. Das bedeutet, ihr Innenwiderstand ist konjugiert-komplex zu dieser Last, also dieselben Zahlenwerte, nur mit Minuszeichen vor dem "j".

Das Anpassnetzwerk läßt sich auf zwei Bauteile reduzieren: von der Antenne ausgehend, die als reeller 50Ω- Widerstand angenommen wird, ist ein Kondensator in Reihe geschaltet. C8 und C9 (in der Tabelle C9 und C10 bezeichnet) liegen in Reihe und sind gleich groß, dürfen also in einem Kondensator mit der halben Kapazität zusammengefasst werden. Dann liegt noch L1 parallel zur Quelle, L3 hat mehr als den 20-fachen Wert und kann vernachlässigt werden. Das ganze läßt sich im Smith-Diagramm gut darstellen.

Von der Antenne im Mittelpunkt ausgehend bewegen wir uns mit dem Serien-C Cs auf einem Kreisbogen nach unten (kapazitive Halbebene) auf den Punkt "Unendlich" rechts außen zu. Ungefähr senkrecht unter dem Zielpunkt, hier für 433 MHz gezeichnet, biegen wir ab auf eine Kreisbahn für die Parallelinduktivität Lp. Sie führt in die obere (induktive) Halbebene auf den Nullpunkt links zu. Der genaue Schnittpunkt beider Kreise kann "mit Zirkel und Lineal" oder einem der Hochfrequenz-Berechnungsprogramme ermittelt werden.

Die Kreise für Lp oder Cp sind im Smith-Diagramm nicht eingezeichnet , um die Übersicht zu wahren. Man könnte ein gespiegeltes Diagramm darüberlegen, aber stattdessen spiegelt man die Kurve am Diagramm-Mittelpunkt (dünne blaue Kurven). Am Rand kann man jetzt die auf 50Ω (bzw. 1/50Ω für die gespiegelte Kurve) normierten Blindwiderstände ablesen. Für Cs lesen wir eine Differenz zwischen Start und Zielpunkt von etwa Xc=(3,2-0) * 50Ω ab, für Lp sind es (0,25 +0,32) = 0,57*(1/50Ω). Damit erhalten wir Cs=1/(2*Pi*f*Xc)=2,3 pF das war wie gesagt die halbe Kapazität der beiden hintereinandergeschalteten Kondensatoren, Tabellenwert ist 4,7pF und Lp=1/(2*Pi*f*0,57*(1/50))= 32,2 nH, der Tabellenwert ist 27nH.

Im RF12 wird ein um zwei Bauteile (im Bild C2 und L1 genannt) erweitertes Netzwerk empfohlen, das macht man um eine breitbandigere Anpassung zu erreichen.

Betriebsspannung

Achtung nicht alle Module sind für 5V geeignet, alle Typen mit "B" am Ende sind nur für 3,3V. Man muß dann entweder den Mikrocontroller ebenfalls mit 3,3V betreiben, oder Pegelwandler verwenden.

Messungen

Drei Messungen am RFM12 zeigen den Einfluß von Eingangpegel, Frequenzhub und Mittenfrequenz auf das Ausgangssignal, gemessen am Filterkondensator CFIL. Zwei weitere Kurven zeigen die ARSSI-Spannung (Anschluß am Kondensator in der Ecke) und die damit gemessene Filterkurve.

Was folgt aus diesen Messungen?

- Der ARSSI-Anschluß zeigt uns über mehr als 100 kHz ein Sendesignal an. Decodierbar ist es aber nur im Abstand von weniger als 5 kHz von der Mittenfrequenz. Ohne Abgleich von Sender und Empfänger ist also die AFC unverzichtbar.

- Das "Loch" in der Mitte der Durchlasskurve stammt von dem im Datenblatt gezeigten Hochpass "> 7 kHz". Für ein unmoduliertes Sendesignal geht die ARSSI-Spannung fast auf den Rauschpegel herunter, hier wurde mit ±15kHz moduliert.

- Damit lässt sich der Empfänger abgleichen. Man braucht dazu nur ein unmoduliertes Sendesignal auf der Sollfrequenz. Das kann ein mittels Frequenzzähler abgeglichenes zweites RFM12 sein. Der Empfängerquarz wird mit den 4 Bit für die Oszillatorkapazität genau auf dieses "Loch" der ARSSI-Spannung eingestellt.

Die AFC-Messdauer ist im Datenblatt nicht genannt, eine schnelle Abfrage des ATGL-Bit im Statusregister im "Auto-AFC" - Modus liefert minimale Pulsbreiten von ca. 250..270 µs, entsprechend einer Messfolgefrequenz von 4 kHz (schneller oder präziser AFC-Modus?) - leider nicht ausreichend um 9600 Baud Schmalband-FM zu demodulieren. Im Auto-Modus werden zwei Messungen zusammengefasst, damit beträgt die Updaterate sogar nur 2 kHz. Weitere Messung: ab etwa ± 10 kHz Hub synchronisiert sich das ATGL-Bit auf der Mittenfrequenz mit einem bis zu 1,8...2 kHz FM-modulierten Signal.

Neue Idee: "Dithering und FM-Flankendemodulator":

Wenn das Empfangssignal nicht weit genug FM-moduliert ist, müssen wir eben den Empfänger modulieren. Im Timer-Interrupt wird die Quarzkapazität oder die PLL z. B. mit 38,4 oder 76,8 kHz und mindestens ±15kHz Hub umgeschaltet, sodass bei Empfang eines unmodulierten Signals am CFIL-Ausgang ein symmetrisches Rechteck dieser Frequenz erscheint. Ist das Empfangssignal schmalbandig FM-moduliert, und man stimmt den Empfänger leicht daneben ab, so sollte das CFIL-Signal mit dieser Modulation PWM-moduliert sein. Ein Tiefpass filtert die Dithering-Frequenz weg und übrig bleibt (wenns funktioniert) die Modulation, vielleicht sogar analoger Sprechfunk...

Motto "Engineering is the art of making what you want from things you can get." (von http://www.dsprelated.com)

Bezugsquellen

Links

- AVR RFM12

- RFM12 Protokoll Stack

- RF_SOAP

- RN-MikroFunk, kleines kompaktes AVR-Evaluationsboard für RFM12b und RFM12

- Pollin_Funk-AVR-Evaluationsboard

- Sehr kleines/stromsparendes Funk-AVR-Evaluationsboard RN-MikroFunk mit vielen RFM12B Beispielen

- Bezugsquellen

- Library zur Ansteuerung des RFM12

- Datenblatt des Chipherstellers Integration IA4420.pdf

- Silabs hat Integration im Juni 2008 gekauft, Chipbezeichnung jetzt Si4420

Folgende Links sind mit Vorsicht zu genießen, da die Datenblätter teilweise fehlerbehaftet sind. Es empfiehlt sich, direkt mit dem Datenblatt des RF12 (das ist das IC auf dem Modul) zu arbeiten. Dieses ist so gut wie fehlerfrei.