Speicher

Im Bereich der Mikrocontroller gibt es viele verschiedene Arten von Speicher.

| Typ | Geschwindigkeit | Größe | Schreibzugriffe | Datenerhalt ohne Spannung |

|---|---|---|---|---|

| RAM | ++++ | ++++ | beliebig oft | nein |

| EPROM | + | +++ | ~1000 | ja |

| EEPROM | + | +++ | 10.000-1.000.000 | ja |

| FLASH-ROM | ++ | +++++ | 1000-10.000 | ja |

| OTP-ROM | + | +++ | einmal | ja |

| Register | ++++++ | + | beliebig oft | nein |

| F-RAM | ++++ | +++ | beliebig oft | ja |

Die Angaben von Geschwindigkeit und Größe sind nur prinzipiell dargestellt.

RAM

Random Access Memory - Speicher mit wahlfreiem Zugriff.

Damit ist gemeint, daß man beim Zugriff keine Reihenfolge einhalten muß und jederzeit auf alle Daten zugreifen kann, lesend und schreibend. Allerdings trifft diese Eigenschaft mittlerweile auf viele Speichertypen zu. Spricht man heute von RAM, dann meint man meistens Speicher, den man beliebig oft lesen und beschreiben kann und der zum Datenerhalt Strom benötigt. Es gibt auch Speichertypen, die diese Eigenschaften nicht haben, aber trotzdem "RAM" im Namen tragen, z. B. FRAM. Über diese Speicher spricht man dann in ihrer vollen Form (z. B. FRAM), man nennt sie nicht einfach nur RAM.

SRAM

Static Random Access Memory - statischer RAM.

Hat man SRAM als einzelne ICs, dann liegt ihr Vorteil darin, dass sie zum Datenerhalt nur eine Versorgungsspannung brauchen und keinen Refresh (siehe DRAM weiter unten). Das bedeutet unter anderem, daß ein Mikrocontroller beliebig langsam getaktet werden kann (z. B. mit einem 32,768 kHz-Uhrenquarz) bzw. im Schlafmodus mit vollkommen gestopptem Takt betrieben werden kann, ohne seine Daten zu verlieren. Er kann mit einer hohen Geschwindigkeit gelesen und geschrieben werden, ohne Begrenzung an Lese-/Schreibzyklen.

Bei Mikrocontrollern und auch bei Mikroprozessoren (wie x86-kompatiblen) wird diese Speichertechnologie als RAM eingesetzt. Bei den heutigen Hochleistungsprozessoren, die im oberen MHz- bis GHz-Bereich arbeiten und viel RAM benötigen, ist meist nur der auf dem CPU-IC untergebrachte Cache als SRAM ausgeführt.

SRAM-Zellen benutzen als Grundprinzip der Speicherung FlipFlops, was sie sehr schnell macht, zum Datenerhalt aber eine ständig anliegende Spannungsversorgung nötig macht. Technisch gesehen besteht ein SRAM-Bit meist aus 4 oder 6 Transistoren, wodurch relativ viel Platz verbraucht wird. Die Stromaufnahme im inaktiven Zustand ist meist sehr gering (einige zehn Mikroampere oder weniger). Im aktiven Zustand haben SRAMs allerdings einen beträchtlichen Stromverbrauch; ein typischer Wert für ein 32kx8-SRAM sind ca. 100mA bei 5V.

Anschluss an den Mikrocontroller

Der Speicher wird über einen Daten- und einen Adressbus sowie die Steuerleitungen /OE (output enable, manchmal auch als /RD read enable bezeichnet), /WE (write enable) und /CS (chip select) angeschlossen. Der Datenbus für einen Speicher der Organisation 32k x 8 Bit hat eine Breite von 8 Bit, der Adressbus ist dann 15 Bit breit. Um den Speicher zu aktivieren, muß /CS auf LOW (Masse) gelegt werden. Das kann verwendet werden, um mehrere Speicher- oder andere Bausteine am selben Bus zu betreiben. Dabei muß sichergestellt sein, daß jeweils nur ein IC zur gleichen Zeit ein low-aktives /CS-Signal erhält, damit es nicht zum Kurzschluss auf dem Datenbus kommt (siehe Ausgangsstufen Logik-ICs). Ist außer dem Controller nur ein einziges IC an den Bus angeschlossen, kann /CS auch fest mit Masse verbunden und der Speicher somit permanent aktiviert werden. Das /OE-Signal dient hier dem Zweck, nach Anlegen einer Adresse am Adressbus den Speicher zum Übertragen eines Datenworts über den Datenbus zu veranlassen (Lesezugriff). Sollen Daten in das SRAM geschrieben werden, legt der Controller die Adresse und die Daten an, um den Speicher dann mit einem Low-Signal auf der /WE-Leitung zum Speichern zu bringen.

Die Reihenfolge der einzelnen Daten- und Adresspins am RAM kann nach Belieben variiert werden, wenn dadurch das Layout der Platine vereinfacht wird. D.h. D0 des RAMs kann auch an D5 des Controllers gehen. Der Grund dafür ist folgender: Die Daten werden zwar verstreut im RAM gespeichert (Adressleitungen vertauscht) oder in falscher Anordnung im Speicher angelegt (Datenleitungen vertauscht), jedoch kompensiert sich diese Unordnung beim Auslesen wieder. ACHTUNG, das geht nur bei einfachen SRAMs. DRAM oder neuere Speicher nehmen das fix übel, weil die Ansteuerung durcheinander kommt (Adressmultiplexing, Pagemodus, Byteslanes bei DDR-RAM etc.). Bei diesen ICs kann man bestenfalls Datenleitungen tauschen, bei DDR-RAMs nur innerhalb einer Byte-Lane. Prinzipiell sollte man davon aber nur sparsam Gebrauch machen, wenn es dem Layout wirklich hilft.

Ohne Latch

Die einfachste Art, eine externes SRAM an den Mikrocontroller anzubinden ist die direkte Verkabelung. Jeder Pin des SRAMs bekommt einen Pin am MC. Jedoch verschwendet diese Anschlußweise auch ziemlich viele IO-Pins. Bei dem nebenstehenden 32-KiBi-RAM verbraucht der Anschluß so 8+15+2 (25) Pins.

Am sinnvollsten verwendet man einen ganzen Port für die acht Datenleitungen, damit man schnell darauf zugreifen kann. Die Adressleitungen A0 bis A7 werden auch möglichst auf einen Port gelegt. An einen dritten Port wiederum werden A8-A14 angeschlossen; /WE und /OE können dann mit zwei weiteren freien Pins verbunden werden. Zusammen belegt diese Methode also 25 Pins für 32 KiBi. Auf diese Weise kann man an praktisch jeden Mikrocontroller einen SRAM anschließen, die Ansteuerung kann dann rein in Software vorgenommen werden. Das ist jedoch relativ aufwendig, in der Anwendung umständlich und langsam. Sinnvollerweise sollte der Mikrocontroller eine eingebaute Speicherschnittstelle haben, um den SRAM per Hardware direkt und schnell ansprechen zu können.

Mit Latch

Will man wertvolle Pins einsparen so benutzt man am besten ein Latch, das die Signale zwischenspeichert. Man kann wählen, ob nur A0-A7 eingespart werden soll, oder gleich alle Adressleitungen. Für den ersten Fall benötigt man ein 8-Bit Latch, das ausreichend schnell schalten kann, für den zweiten Fall zwei Latches.

Die Eingänge des Latches werden mit den Datenleitungen des Mikrocontrollers verbunden und das Enable-Signal bekommt einen eigenständigen Pin. Die Einsparung an Pins geht jedoch auf Kosten der Geschwindigkeit, da zuerst das Latch mit der Adresse geladen werden muß bevor die eigentliche Aktivierung des SRAMs beginnen kann. Bei einem 32-KiB-SRAM werden mit einem Latch nur noch 8+7+3 (18) Pins gebraucht, gegenüber der Variante ohne Latch also eine Einsparung von sieben Pins mit einem Bauteil.

Mit XMEM-Interface

Viele Controller (AVR, 8051) besitzen ein Speicherinterface, das es ermöglicht, SRAM anzuschließen und dieses als Erweiterung des internen RAM zu benutzen. Dieses wird dann mit einem Latch angeschlossen, um Pins zu sparen. Das Enable-Signal des Latch muß mit dem Ausgang ALE (Address Latch Enable) verbunden werden, wie es im Schema gezeigt wird. Nach der Initialisierung des externen Speicherinterfaces steht der Software auch das externe SRAM zu Verfügung. Der Vorteil gegenüber den beiden erstgenannten Methoden ist die höhere Geschwindigkeit und einfachere Nutzung, denn die Steuersignale müssen nicht per Software erzeugt werden, das macht die Hardware in den Mikrocontrollern allein.

- Forumsbeitrag: 512kB SRAM am ATXmega

BRAM

Block RAM - Block RAM

Damit wird ein Speicher bezeichnet, welcher sich in FPGAs befindet. Seine Blöcke sind physikalisch wie SRAM aufgebaut, sehr leicht anzusteuern und sehr schnell (200MHz++). Die Ansteuerung erfolgt jedoch synchron wie bei SDRAM mit einem Taktsignal. Die meisten FPGAs besitzen BRAM, das über zwei komplette Schnittstellen verfügt, (engl. Dual Port Memory). Damit ist es möglich, von zwei Seiten gleichzeitig auf die Daten zuzugreifen. Das ist sehr vorteilhaft für FIFOs, da hier gleichzeitig Daten gelesen und geschrieben werden können. Bei den meisten FPGAs sind die beiden Ports voneinander komplett unabhängig und können mit unterschiedlichen Takten betrieben werden, was immense Vorteile für asynchrone FIFOs bringt.

DRAM

Dynamic RAM - dynamischer RAM

Ein DRAM-Bit besteht aus einem Transistor und einem Kondensator, wodurch man es sehr klein bauen kann. Allerdings kann der Kondensator seine Ladung nicht unbegrenzt lange halten, weshalb diese regelmäßig erneuert (englisch Refresh) werden muß. Das macht DRAMs im Mikrocontrollerbereich etwas unbeliebt. Bei großen 16/32-Bit-Controllern befinden sich oft DRAM-Controller mit auf dem IC (on chip) die sich um den Refresh kümmern, da große, schnelle und billige RAMs nur als DRAM verfügbar sind. Heute wird fast nur noch der Nachfolger SDRAM dafür verwendet, der klassiche DRAM ist ein Auslaufmodell. Auch einige 8-Bit Prozessoren wie der Z80 unterstützten DRAM hardwareseitig. Bis zum Anfang der Pentium-Zeit war DRAM der Hauptspeicher in PCs (EDO-RAM). Die Ansteuerung erfolgt asynchron über verschiedene Steuersignale. Die Adressen werden dabei gemultiplext.

SDRAM

Synchronous DRAM - synchroner DRAM

Dabei handelt es sich um die Weiterentwicklung von DRAM. Wie der Name verrät, ist dieser Speicher synchron, d.h. sämtliche Steuer -und Datentransfers zwischen SDRAM und Speichercontroller erfolgen synchron zu einem Taktsignal. Das vereinfacht das Design wesentlich und ermöglicht höhere Datentransfergeschwindigkeiten (Taktfrequenz, typisch bis 133 MHz).

- Beschreibung von Synchronous Dynamic Random Access Memory bei Wikipedia

- Artikel zum SDRAM-Timing

- Forumsbeitrag: 16MB-SDRAM am ATXmega

DDR-SDRAM

Double Data Rate SDRAM - SDRAM mit doppelter Datenrate

Oft als DDR-RAM abgekürzt. Es handelt sich um eine Weiterentwicklung von SDRAM. Im Gegensatz zum Vorgänger werden sowohl bei steigender wie auch bei fallender Flanke des Taktsignals Daten übertragen, also pro Taktzyklus zwei Datenworte. Z.B. arbeitet DDR266 mit 133 MHz Taktfrequenz, DDR400 demzufolge mit 200 MHz. Die Steuerung erfolgt jedoch nach wie vor nur mit einfacher Taktfrequenz. Die höhere Taktfrequenz wird durch eine neue IC-Technologie, niedrigere Betriebsspannung (2,5V anstatt 3,3V) und andere IO-Standards (SSTL-2,5 anstatt 3,3V CMOS) erreicht. Das ist auch nötig, weil bei diesen Datenraten das Thema Wellenwiderstand bereits eine elementare Rolle spielt.

DDR2-SDRAM

Hier handelt es sich um die Weiterentwicklung von DDR-SDRAM. Durch weitere Verbesserungen der IC-Technologie, vor allem durch kleinere Strukturgrößen und niedrigere Betriebsspannung (1,8V anstatt 2,5V). Das Protokoll ist ähnlich zu DDR-RAM, die Taktfrequenzen sind höher als bei DDR-RAM.

DDR3-SDRAM

Eine Weiterentwicklung der DDR2-Architektur Die Versorgungsspannung wurde auf 1,5V reduziert. Stand 2011 war DDR3-RAM der am meisten eingesetzte Speicher. Häufig wird DDR3-1333 verwendet; dieser Speicher hat eine Taktfrequenz von 667 MHz. Die maximale Taktfrequenz von DDR3-Speichern liegt bei 800MHz (DDR3-1600). Diese Frequenz findet man als Maximalfrequenz für ein 0101-Bitmuster auch auf dem Datenbus (800MHz = 1600Mb/s). Der Kommando- und Adressbus wird mit einfacher Taktfrequenz und damit maximal mit der halben Frequenz (400 MHz = 800Mb/s) betrieben.

DDR4-SDRAM

Die neueste Variante ist die von Micron angekündigte DDR4-Speichertechnik. Sie lauft auf nur noch 1,2V statt 1,5V, bietet bis zu 16GB Speichervermögen je Chip und hat einige Verbesserungen im Bereich der Adressierung und der Spannungsversorgung.

PSRAM

Pseudo Static RAM

Pseudostatisches RAM ist intern ein DRAM, kann aber wie ein normales asynchrones SRAM angesteuert werden. Um den Refresh braucht man sich nicht zu kümmern. Der Nachteil ist die verglichen mit SRAMs langsame Zugriffszeit (z. B. 70 ns).

Manche PSRAMs, z. B. das CellularRAM von Micron, implementieren zusätzlich einen synchronen Betriebsmodus der schnelle Burst-Zugriffe erlaubt. Um den Refresh kümmert sich das PSRAM auch hier intern, allerdings muss der Benutzer ggf. Wartezeiten beim Zugriff einhalten oder Busy-Leitungen abfragen.

FRAM

Ferroelectric RAM - Ferroelektrisches RAM

FRAM is a registered trademark of Ramtron International Corporation (U.S.A.)

Bekannte Hersteller:

- Ramtron

- Fujitsu

- Epson

Links:

MRAM

Magnetic RAM - magnetisches RAM

Hier handelt es sich um Speicher, der die Daten nicht elektrisch, sondern magnetisch speichert. MRAMs behalten ihren Speicherinhalt auch ohne Stromversorgung.

Bekannte Hersteller:

NVRAM

Non Volatile RAM - nichtflüchtiger Speicher

NVRAM bezeichnet keine bestimmte Speichertechnologie, sondern allgemein ein RAM, das seinen Speicherinhalt beim Wegfall der Versorgungsspannung beibehält.

Realisierungmöglichkeiten:

- SRAM mit Lithiumbatterie, Speicherdauer mehrere Jahre; Hersteller: STM, Maxim

- SRAM mit Goldcap, Speicherdauer mehrere Wochen bis Monate

- FRAM, Speicherdauer 10 - 100 Jahre; Hersteller: Fujitsu, RamTron

- RAM mit automatischem EEPROM-Backup, Speicherdauer bis zu 100 Jahre; Hersteller: Intersil

[MLC]NRAM

NRAM ist eine neue nichtflüchtige DRAM-Alternative. Die Speicherzellen bestehen aus Kohlenstoff-Nanoröhrchen (CNT, carbon nano tube). NRAM-Zellen arbeiten mit elektrostatischer Abstoßung und Anziehung bzw. Dehnung und Schrumpfung dieser Kohlenstoff-Nanoröhrchen, und arbeitet mit etwa der selben Betriebsspannung und den gleichen Gegebenheiten wie DDR-SDRAM, braucht aber keine Refreshzyklen und auch keine permanente Versorgung mehr, um Daten zu erhalten. (Ähnlich wie beim NVRAM). Eine MLC-Speicherzelle kann verschiedene (analoge) Zustände annehmen, und daher auch mehr als nur 1 Bit speichern. Die Einsparung des Refreshs könnte im PC-Bereich über 10% Leistungssteigerung mit sich bringen. Und auch für Serveranwendungen wäre NRAM eine gute "Alternative" zum NVRAM oder Batteriegepufferten Speichern.

Zukunftsmusik: NRAM-Module könnten DDR4(!) Slot Speichermodule ablösen und sollen insgesammt günstiger als NVRAM werden. 16-GBit-Chips mit ECC sind möglich (in Planung?), es "mangelt" aber leider noch an der Serien- u. Massenfertigung, da die Röhrchen (noch) interne Kurzschlüsse erzeugen können. Dieser Speicher ist noch in der "Anfangs-Phase" und wird noch erforscht. Ob er sich durchsetzt, und wo er überall zu finden sein wird, steht noch in den Sternen. Hersteller: Fujitsu, Nantero, ...

Speichermodul

Bei einem Speichermodul sind mehrere einzelne Speicherchips zu einem handlichen, steckbaren Bauteil zusammengefaßt, wie sie z. B. in PCs zum Einsatz kommen.

- Forumsbeitrag: 2MB DRAM an AVR

- Forumsbeitrag: simm-DRAMs parallel

EPROM

Erasable Programmable Read-Only Memory" - löschbarer, programmierbarer Nur-Lese-Speicher

EPROMs sind elektronische Speicher, die in einem entsprechenden Programmiergerät elektrisch programmiert und mit UV-Licht, meist aus einem speziellen Löschgerät, wieder gelöscht werden können. Dazu hat das IC ein Fenster aus UV-durchlässigem Quarzglas. Da das aber relativ umständlich ist und die Gehäuse groß und teuer sind, werden heute meist andere Speicherformen benutzt, z. B. EEPROMs oder FLASH-ROMs.

EEPROM

("Electrically Erasable Programmable Read Only Memory") - elektrisch löschbarer, programmierbarer Nur-Lese-Speicher

Im Gegensatz zu FLASH-ROMs muß man bei EEPROMs nicht immer einen ganzen Block auf einmal löschen, sondern kann auch einzelne Bytes löschen und neu beschreiben. Ein Schreibzyklus dauert ca 3-5 msec.

Die meisten AVR-Controller haben ein integriertes EEPROM als Datenspeicher, es gibt jedoch auch externe EEPROMs, die über den I²C- oder SPI-Bus angeschlossen werden können. Serielle EEPROMs können beispielsweise mit dem universellen und frei verfügbaren Programmer PonyProg programmiert und ausgelesen werden. Eine Einführung dazu findet man im Pony-Prog Tutorial.

Wie oft ein EEPROM beschrieben werden kann, steht im Datenblatt. Typische Werte sind 10.000 bis 1 Million Schreibzugriffe. Danach kann es zu Datenverlusten kommen. Wer regelmäßig in ein EEPROM schreiben will, sollte unbedingt nachrechnen, wie viele Schreibzugriffe er konkret zu machen gedenkt. Schreibt man z. B. jede Sekunde auf die gleiche Stelle, dann macht man in drei Stunden 10.800 Schreibzugriffe und damit kann das EEPROM schon kaputt sein.

EEPROM-Schreibzugriffe minimieren

Sinnvollerweise schreibt man Daten nur direkt ins EEPROM, wenn man sicher ist, dass das nur selten vorkommt. Anderenfalls speichert man die Daten im RAM und kopiert sie nur in großen Zeitabständen ins EEPROM oder dann, wenn die Versorgungsspannung ausfällt. In letzterem Fall muss man durch eine Pufferschaltung gewährleisten, dass die Versorgungsspannung noch ein paar (hundert) Millisekunden stabil ist, nachdem das Netzteil ausgeschaltet wurde.

Wie immer bei Mikrocontrollern geht die Optimierung von Schaltung und Firmware Hand in Hand: Nur in seltenen Fällen müssen bei Spannungsausfall viele Daten geschrieben werden: Selten geänderte Daten werden besser sofort abgespeichert, und nur die automatischen, zeitgesteuerten Schreibvorgänge erfordern das Schreiben bei Stromausfall. Dann kann die Kondensatorstütze deutlich verkleinert werden. Auch das Schreiben in Flash statt EEPROM kann die Kondensatorstütze dramatisch verkleinern: Das Schreiben in ein einziges EEPROM-Byte kostet 4..10 ms (je nach Typ); das Schreiben in bspw. 64 Flash-Bytes einer bereits gelöschten Flash-Speicherseite dauert genauso lange. (Deswegen heißt der Speicher auch so: Flash = Blitz = blitzschnell!)

Eine Kondensatorstütze kann durch Verteilen der zyklischen EEPROM-Schreiblast auf mehrere Zellen oder Bits vermieden werden: Beispielsweise kann eine Uhr eines Arduino Uno mit ATmega328P, die Versorgungsausfall durch Stehenbleiben wie eine mechanische Uhr „überleben“ soll, minutenweise jeweils 1 Bit in einem 60 Bit (8 Byte) großen EEPROM-Abschnitt löschen. Oder sekundenweise in 3600 Bits (450 Byte). Dann wird jedes Bit nur noch stündlich mit einem Schreib- und Löschzugriff belastet. Die restliche Uhrzeit wird in einem anderen EEPROM-Abschnitt stündlich komplett gespeichert. Macht bei 100.000 Zyklen eine Lebensdauer von 100.000 Stunden. Das sind mehr als 11 Jahre. Sollte reichen. Bis dahin sind alle Leuchtdioden durch Alterungsprozesse nur noch halb so hell. Erforderlich dafür ist ein AVR mit EEPROM, bei dem man das automatische Löschen vor dem Schreiben abschalten kann, wie das beim ATmega328P der Fall ist.

Alle Arten von Stützen benötigen irgendeine Form der Meldung der jeweiligen Betriebsart, bevor die Stütz-Energiequelle versiegt, und müssen so ausgelegt sein, dass die Stützzeit länger als die Sicherungszeit ist. Bei Uhren wird die Stützzeit Gangreserve genannt und sollte den längsten zu erwartenden Stromausfall überbrücken.

Das kann mit großen Elektrolytkondensatoren, Goldcaps oder kleinen Batterien (Lithiumzellen) erreicht werden.

Kondensatorstütze

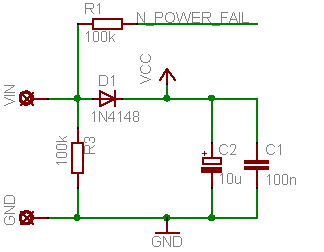

Ein Schaltungsbeispiel findet man in Folgendem:

Wenn die Versorgungsspannung plötzlich abgeklemmt oder kurzgeschlossen wird, verhindert Diode D1 zunächst, dass sich der Pufferkondensator C2 sofort entlädt. Über R1 wird ein externer Interrupt im Prozessor ausgelöst (auf fallende Flanke oder Low Level einstellen!). Dort muss nun der Datensatz aus dem RAM ins EEPROM kopiert werden. Das darf nicht zu lange dauern, denn der Pufferkondensator C2 kann nur für ein paar Dutzend Millisekunden die Betriebsspannung aufrechterhalten. Berechnet werden kann das durch

[math]\displaystyle{ t = \frac{C \cdot \Delta U}{I} }[/math].

- [math]\displaystyle{ t }[/math] : Pufferzeit

- [math]\displaystyle{ \Delta U }[/math] : Spannungsabfall während der Pufferzeit

- [math]\displaystyle{ I }[/math] : Stromaufnahme der Schaltung

Beispiel:

- Verbraucher: ATtiny2313 @ 1 MHz, 5 V, ca. 0,9 mA

- Datensatz: 32 Byte

- Schreibdauer / Byte: ca. 3,4 ms

Wir brauchen also ca. 32×3,4 ms = 108,8 ms, um die Daten im EEPROM zu speichern. Wenn wir den AVR mit 5 V betreiben und zulassen, dass die Spannung bis auf 3 V sinkt (→ ΔU = 2 V), ergibt sich daraus eine minimale Kapazität für C2 von

[math]\displaystyle{ C = \frac{I \cdot t}{\Delta U} = \frac{0{,}9\,\text{mA} \cdot 108{,}8\,\text{ms}}{2\,\text{V}} = 48{,}9\,\text{µF} }[/math].

Das ist das rechnerische Minimum! Real wird man eher den zwei- bis fünffachen Wert wählen müssen, weil

- man Reserven haben will,

- besonders Elektrolytkondensatoren große Toleranzen haben (+20/−60 %!!!),

- besonders Elektrolytkondensatoren bei niedrigen Temperaturen massiv an Kapazität verlieren,

- während des Schreibens des EEPROMs mehr Strom benötigt wird.

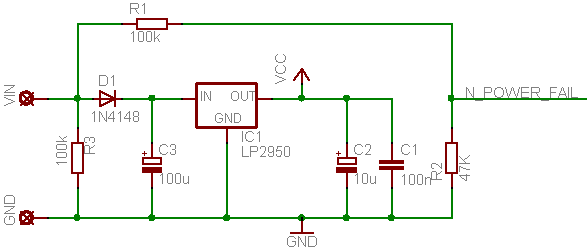

Kondensatorstütze via Längsregler

Verbraucht die Schaltung nun mehr Strom oder muss man größere Datensätze speichern, werden die Kapazitäten bisweilen sehr groß. Was kann man tun? Aus der Formel oben geht hervor, dass durch ein Erhöhen des zulässigen Spannungsabfalls die Kapazität verringert werden kann. Doch unser Controller benötigt eine Mindestspannung, kann aber auch nicht mit 10V betrieben werden. Ja, der Controller nicht, aber ein Spannungsregler! Dieser kommt mit schwankenden Eingangsspannungen problemlos klar. Es sollte unbedingt ein Typ mit geringem Querstrom genutzt werden, wie z. B. der LP2950 (siehe Versorgung aus einer Zelle). Sinnvollerweise werden nur der Prozessor und minimal notwendige Komponenten von diesem Spannungsregler versorgt, Verbraucher mit hohem Stromverbrauch (LEDs, Relais, etc.) werden über einen zweiten Spannungsregler oder direkt vom Spannungseingang versorgt. Der Spannungsteiler aus R1 und R2 muss so berechnet sein, dass beim Erreichen der minimalen Versorgungsspannung Uin ein Interrupt ausgelöst wird. Dazu kann man im AVR den Analogkomparator verwenden. Oder man rechnet mit einer Schaltschwelle von Ucc/2 und verwendet einen normalen externen Interrupteingang.

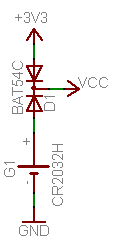

Batteriestütze

Eine andere Lösung ist die Verwendung einer kleinen Lithiumzelle. Diese springt nur ein, wenn sie wirklich gebraucht wird, sprich die Hauptstromversorgung ausfällt.

Die unterbrechungsfreie Umschaltung wird durch zwei Schottky-Dioden erreicht.

Nein! Lithiumzellen dürfen nicht mit Schottky-Dioden angebunden werden, weil diese einen nennenswerten Reversstrom haben!

Der Spannungsabfall über Schottky-Dioden beträgt ca. 320mV bei 1mA und 400mV bei 10mA, der von normalen Si-Dioden 600 mV bei (dann typischen) 10 µA. Noch besser ist die Verwendung eines kleinen MOSFETs, wie in diesem Beitrag gezeigt wird. Damit erreicht man eine Umschaltung der Versorgungsspannung ohne nennenswerten Spannungsabfall. Wesentlicher Vorteil dieser Schaltung ist die um Größenordungen längere Pufferzeit von Sekunden bis Minuten. Der Nachteil ist, dass die Batterie bei regelmäßiger Nutzung irgendwann leer ist und nicht mehr als Backup dienen kann.

Einige Mikrocontroller, namentlich STM32F103, bieten einen gesonderten Batterieanschluss UBAT, der dem Anwender sowohl die Diodenentkopplung als auch die Wurstelei mit der Zustandsmeldung erspart. Leider drehen sich die meisten Errata um dieses Feature, und die verbreiteten China-Clones haben weitere undokumentierte Probleme damit.

Akkustütze

Im Prinzip ist ein Akku wie ein sehr großer Kondensator zu betrachten. Daher gelten die Ausführungen, die unter Kondensatorstütze aufgeführt sind. Die früher üblichen NiCd-Akkus haben eine zu geringe Lebensdauer, deshalb sind diese weitestgehend verschwunden und entweder durch Superkondensatoren oder Lithiumzellen ersetzt worden. NiCd-Akkus sind nicht nur problematisch zu entsorgen, sondern bilden bei Defekt einen Kurzschluss und führen so zu einem Geräte-Totalausfall. Letzteres gilt leider auch für Superkondensatoren.

Mehrfachstütze

Eine von Dioden entkoppelte Reihenschaltung von großer (Akku-) und kleiner (Superkondensator-)Stütze ist praktisch keine Seltenheit sondern Bestandteil jedes Autoradios, wenn man die Starterbatterie als erste Stütze (nach der Lichtmaschine) ansieht. Je nach Situation benötigt der Mikrocontroller mehrere Statusleitungen, für jede Stütze eine.

Flash-ROM

Flash-ROMs sind nichtflüchtige Datenspeicher, ähnlich EEPROMs, die elektrisch lösch- und beschreibbar sind. Sie können Daten auch ohne Stromversorgung speichern. Man kann sie beliebig oft auslesen, aber nicht beliebig oft beschreiben. Wie oft genau, ist unterschiedlich (1.000-10.000 mal) und steht normalerweise im Datenblatt. Ein Flash-ROM kann im Gegensatz zum EEPROM nur sektorweise gelöscht werden, außerdem ist die Anzahl der erlaubten Lösch-/Schreibzyklen meist deutlich niedriger. Flash-ROMs sind als Programmspeicher in Mikrocontrollern weit verbreitet.

OTP-ROM

One Time Programmable-Read Only Memory - einmal programmierbarer Nur-Lese-Speicher

Bisweilen auch als PROM bezeichnet. Ein Speicher, der nur einmal beschrieben werden kann. Das bedeutet natürlich, daß man sich vorher sicher sein muß, daß die Daten bzw. das Programm korrekt sind.

Die interne Struktur besteht aus Leiterbahnen auf dem Chip, die beim Programmieren durchgebrannt werden und danach eine der Diodenmatrix ähnliche Verschaltung bilden. Diese Technik wurde auch bei PALs verwendet. Heute ist sie nur noch sehr selten anzutreffen. Bausteine, die durch ihre einmalige Programmierbarkeit ein OTP-PROM vermuten lassen, wie z. B. die PIC-Controller, benutzen meist die EPROM-Technik, bei der einfach das Quarzglasfenster zum Löschen weggelassen wird. Mikrocontroller mit OTP-ROM verwendet man z. B. in der industriellen Serienfertigung. Dazu entwickelt man die Software auf relativ teuren Controllern mit wiederbeschreibbarem Speicher (FLASH-ROM) und wenn man fertig ist, kommen die billigeren Versionen mit OTP-ROM zum Einsatz.

Datenformate

Was in einen Speicherbaustein geschrieben oder von dort gelesen wird, kann als Binärdatei oder Textdatei definiert werden. Bei Textdateien werden oft Formate mit einer Fehlerkontrollmöglichkeit verwendet. Gängig sind die Formate Intel-HEX (IHEX) und Motorola S-Record.

- Intel HEX-record Format

- Motorola S-records

- S19 File Format

- Motorola S-Record to BINARY File Converter von keil.com

- SRecord 1.32 is a collection of powerful tools for manipulating EPROM load files. (GPL)

- Hex2Bin Konverter unter GPL und von Atmel

- EPROM mit UV-LEDs löschen?

- Using Alternate UV Sources to Erase EPROMS

Register

Die Register eines Prozessors sind Speicher mit geringer Kapazität und kürzester Zugriffszeit. Sie dienen zur vorübergehenden Speicherung von Informationen, welche im Moment verarbeitet werden sollen. Viele CPU-Befehle funktionieren nur mit Registern. Will man z. B. zwei Zahlen addieren, dann müssen sich die beiden Summanden bei den meisten Controllern in Registern befinden. Befinden sich die Summanden im RAM, dann müssen sie vor der Addition in Register kopiert werden. Die Klassifizierung der CPU bzw. des Mikrocontrollers gibt die Breite dieser Register an (8/16/32/64 Bit-CPU).

Weiterhin haben alle Mikrocontroller sogenannte Special Function Register (SFR, spezielle Funktionsregister). Das sind spezielle Register, welche sämtliche Funktionen und Module des Mikrocontrollers steuern ( IO-Pins, UART, SPI, Timer, etc.). Diese befinden sich physisch zwar auf dem Mikrocontroller-IC, logisch allerdings ausserhalb der CPU und werden meist über andere Befehle angesprochen als die normalen CPU-Register.

WOM

Write Only Memory - Nur Schreib-Speicher

Derzeit ist nur ein Modell bekannt: Signetics 25120 9046xN (Datenblatt (PDF)). Weitere Berichte zu diesem zukunftsträchtigen Bauteil siehe The origin of the WOM - the "Write Only Memory" von Bob Pease. ;-)

WOMs lassen sich auch leicht selbst herstellen, indem z. B. bei SRAMs der /OE-Pin entfernt wird.

Externe Speichermedien

Siehe Artikel