DDS

Die Direkte Digitale Synthese (engl. Direct Digital Synthesis) ist ein Verfahren zur Erzeugung einer Wechselspannung mit definierter Kurvenform mittels digitaler Logik, wie Addierer, ROM und DA-Wandler. Sie ist eine der wichtigsten Funktionen der digitalen Signalverarbeitung und kann in Microcontrollern in Software oder digitalen Logikbausteinen in Hardware aufgebaut sowie als fertiger Chip inklusive DA-Wandler erworben werden.

Funktionsweise

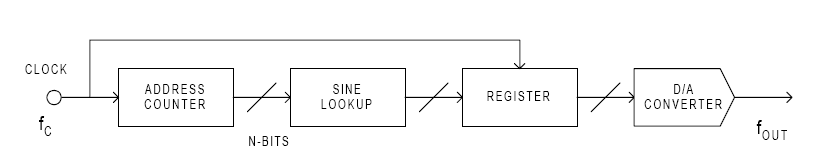

Der Takt für eine DDS wird meist mit einem Quarzoszillator generiert, manchmal auch noch zusätzlich über eine PLL für sehr hohe interne Takte im Chip, dem PLD oder dem Microcontroller. Der Addresszähler, der als Phasenakkumulator arbeitet, wird mit jedem Takt um eine definierte Schrittweite hochgezählt, die die Frequenz mitbestimmt. Der Wert des Akkumulators entspricht der Phase bezogen auf eine volle Schwingung von 0-360° und ist binär von 0 bis 2^M-1 dargestellt. Der Phasenakkumulator hat eine Breite M von typisch 8-48 Bit. Die höchstwertigsten N Bits (N <= M) bilden die Adresse für einen Speicher (Look UpTable), in welchem die Kurvenform abgelegt ist. Die niederwerigen Bits sind die Nachkommastellen, welche Rundungsfehler reduzieren. Sie sind wesentlich für das richtige Arbeiten der DDS. Die Gesamtauflösung des Akkumulators bestimmt letztlich die Auflösung, mit welcher die Frequenz erzeugt werden kann. Die Genauigkeit bestimmt die Taktquelle der DDS, meist ein Quarzoszillator. Die Anzahl N der MSBs des Phasenakkumulators bestimmt wiederum den lokalen Phasenfehler und damit das Phasenrauschen, die Bitbreite K des AD-Wandlers das | Quantisierungsrauschen.

Die Grundformel der DDS lautet

[math]\displaystyle{ f_{out} = \frac{FTW}{2^M} \cdot f_{clk} }[/math]

FTW: frequency tuning word, Einstellwert für die Frequenz im Bereich [math]\displaystyle{ 0-2^{M-1} }[/math]

Der Ausgangswert der Tabelle gelangt auf einen DA-Wandler, dem meistens ein analoges Filter nachgeschaltet werden muss, um die systematischen Störsignale des DA-Wandlers ("Treppenstufen" Oberschwingungen) herauszufiltern.

Die LookUpTable kann fest (ROM), programmierbar (RAM, Arbitrary Waveform Generator) oder auch in Echtzeit berecht sein. Die Kurvenform entspricht aus praktischen Gründen fast immer einer Sinusfunktion. Für den Fall anderer Wellenformen ist zu beachten, dass diese Oberwellen beinhalten, auf die ein nachgeschaltetes Filter Rücksicht nehmen muss. Auch ergeben sich dann niedrigere, maximal erzielbare Frequenzen, die noch sinnvoll dargestellt werden können. In der Regel kommt es bezüglich dieser Frequenzen zu Phasensprüngen (Jitter).

Die maximal erzielbare Ausgangsfrequenz ist immer kleiner gleich der halben Taktfrequenz, was durch das Abtasttheorem von Nyquist/Shannon erklärt wird. Real sind teilweise nur deutlich niedrigere Frequenzen gut nutzbar, da Frequenzen in der Nähe der Abtastfrequenz sehr steilflankige Filter benötigen, die sich praktisch nur sehr aufwändig realisieren lassen.

Die Qualität der DDS hängt damit massgeblich von der des analogen Filters ab. Mit einem Filter hoher Ordnung lassen sich sehr gute Sinussignale erzeugen. Die Nichtlinearitäten des Filters im Bezug auf die Amplitude sind durch Variation des digitalen Ausgangssignals (Amplitude) kompensierbar. Gerade im Bereich der Grenzfrequenz kann damit der Frequenzgang gut linearisiert werden.

Eigenschaften

- vollständig digitaler Aufbau, damit keine Probleme mit analogen Parametertoleranzen und Temperaturdrift

- Extrem grosse Frequenzauflösung, theoretisch unbegrenzt, praktisch bis in den Bereich von Milli- un MikroHertz

- phasenkontinuierliche Phasen- und Frequenzmodulation mit praktisch Null Einschwingzeit möglich

- mehrere DDS-ICs lassen sich mit digitaler Genauigkeit und Reproduzierbarkeit synchronisieren

Mit Mikroprozessoren und DSPs sind je nach Güteanforderungen Ausgangsfrequenzen bis typisch 50MHz, mit FPGAs bis 100MHz und speziellen ASICs bis zu 1 GHz möglich

Anwendungen

Verwendung findet das DDS-Prinzip in vielen Bereichen:

- Niederfrequenz (NF), als Signal und Testgenerator, meist mit möglichst gutem Sinus

- Audiobereich, höchste Anforderungen an Wellenform

- Hochfrequenz (HF), hohe Frequenzanforderung

- Funk-Bereich (Taktfrequenzen bis 4 GHz und mehr) z.B. SDR

Bei geringen Ausgangsfrequenzen < 15kHz kann für einfache Audioanwendungen noch mit Mikrocontrollern gerarbeitet werden. Konkret wurden mit einem AVR@16MHz bei weniger als 10% Prozessorlast eine Schleife mit 150kHz erzeugt und passend gefiltert, wodurch ein Sinus mit <0,06% Fehler erzielbar war.

Bei anspruchsvolleren Audioanwendungen mit tauglicher Musikalität sind Abtastraten von wenigstens 100 x fg, konkret 9,6 MHz nötig, um den Sinus gut genug abzubilden und einen SFDR von besser als 60dB bis in die Höhen zu erreichen. Für 100dB Güte (z.B. Audiomessfunktionen) sind 10.000 x fg nötig. Konkret wird der DA-Wandler mit 20kHz x 10k = 200MHz angesteuert.

Bauteile und Hersteller

Bekanntester Hersteller ist Analog Devices.

Bekannte ICs:

- AD9833 (25MHz)

- AD9834 (75MHz)

- AD9835 (50MHz)

- AD9851 (180MHz)

- AD9854 (300MHz)

- AD9951 (400MHz)

Die moderneren ICs beinhalten weitere Funktionen wie automatische, programmierbare Amplitudenmodulation (AM), Phasenmodulation (PM), Frequency Shift Keying (FSK) und ähnliches mehr. Viele ICs sind mehrkanalig und liefern einen Sinus- und Cosinusausgang gleichzeitig.

Siehe auch

Artikel

- Digitaler Funktionsgenerator

- DDS basierter Funktionsgenerator mit AD5930

- 200MHz DDS-Generator

- FPGA Lab

- Digitale Sinusfunktion

- DDS-Signalgenerator_per_USB

- AVR - Die genaue Sekunde / RTC

Beiträge

- Universell programmierbarer Funktionsgenerator

- HF-Meßplatz:

- Einfache Schaltung: 6 Drehschalter - PIC16F84 - AD9833

- Berechnung des Frequency Tuning Words

- Praktische Umsetzung

- DDS Sinuserzeugung

- verbesserte DDS, basierend auf Jesper DDS, mit verschiedenen Modulationsarten.

- Signalgenerator, Grenzen eines Atmega8

- SPWM auf Atmega8, bitte um Feedback hinsichtlich Optimierung

- DDS mit AM Modulation

- Grundlagen

- Sinus mit DDS

- Nicht-Sinus DDS

- Sinustabelle mit 2 Geschwindigkeiten

- DDS AD9851 Synchronisierung

- Zwei 45kHz-Signale, 90° Phasenverschoben erzeugen

- Fraktionaler Teiler, 14:1 bis 524000:1

- DDS im FPGA

Suchen

- Suche nach *sinus* im Forum

- Suche nach tonerzeug* im Forum

- Suche nach dds* im Forum

- Suche nach synthe* im Forum

Weblinks

- DDS mit ML2037

- DDS-Signalgenerator, bis 500 MHz (1200MHz Takt) -> SYN500, SYN500/2

- AD9850 DDS-board (0 to 40 MHz), ATtiny2313 basiertes USB Interface

- AVR DDS signal generator V2.0, DDS 0-65534 Hz; Rechtecksignal 1-8 MHz

- MiniDDS, Jesper's AVR pages, DDS using an AVR (DTMF mit uC)

- AVR314 DTMF Generator, Microchip Application Note

- DDS Tutorial, Theorie und alle Vor-und Nachteile (Phasenrauschen etc); Analog Devices